- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

15.3 Організація циклічного буфера в dsp

Вхідний контроль:

Наведіть приклади використовування режиму обміну ПДП поміж МПС та зовнішніми пристроями.

Що таке модульна арифметика?

Завдання цифрової обробки сигналів потребують реалізації потокової обробки великих обсягів даних у реальному режимі часу. Це є можливе за високої швидкодії процесора та наявності апаратних засобів інтенсивного обміну із зовнішніми пристроями.

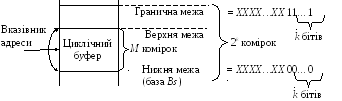

Циклічний буфер слугує за “вікно” заданого розміру, через яке “протягується” задана кількість відліків вхідного сигналу з метою їхнього оброблення в реальному часі.

Циклічний буфер у складі DSP– це обмежена за обсягом пам’ятьХабоYзМкомірок, які адресуються за типом непрямого регістрового адресування. Ефективна адреса комірки обчислюється як алгебраїчна сума вмісту регістра адресиRn, регістра зміщенняNnта регістра модифікаціїМnза правилами модульної арифметики. Модульна арифметика забезпечує звернення лише до тих комірок пам’яті, які належать конкретному буферові.

Нижня межа буфера визначається вмістом регістра Rn, а верхня дорівнює (Rn + M– 1), де значення (М– 1) зберігається в регістрі модифікаціїМn. Значення нижньої межі, яка називається ще базою адреси (Bs), має мати нулі уkмолодших розрядах,kвибирається з умови 2k ≥М; база адреси є кратна до 2k.

Для організації буфера обсягом 5 комірок пам’яті (М= 5) кількістьkмолодших нульових бітів у базіBsможе становити 3. БазаBsможе бути 101000 або 111000, тобто бути кратною до 2k. У загальному випадку база вибирається такою, що дорівнює

Х ХХХ...ХХ

00…0 , деХ= 0 або 1.

ХХХ...ХХ

00…0 , деХ= 0 або 1.

(16 – k) бітk біт

Верхня межа буфера дорівнює Bs + M– 1, а гранична межа –Bs+ 2k – 1.

На рис. 15.3 подано організацію циклічного буфера.

Рисунок 15.3 – Організація циклічного буфера

Початкова адреса, тобто вміст регістра Rnможе встановлюватись довільно у зазначених межах.

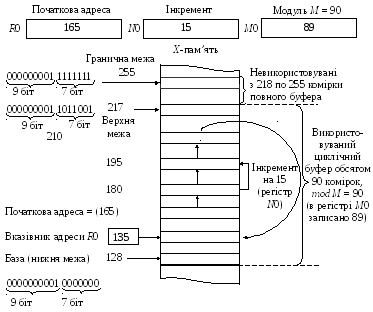

При використовуванні регістра Nnадреса обчислюється за формулою((Rn ± Nn)mod M. На рис. 15.4 подано виконування команди

MOVE Х0, Х: (RY) + N0

при роботі з циклічним буфером. Згідно з командою, вміст вхідного регістра АЛП даних Х0 пересилається до коміркиХ-пам’яті даних за адресою, зазначеною вR0, після чого здійснюється інкрементування адреси на вміст регістраN0 з використовуванням арифметики заmod M. Всі адреси зазначено в десятковій системі числення; циклічний буфер має обсяг 90 комірок з базоюBs= 128, верхньою межею 217 та граничною межею 255.

Рисунок 15.4 – Використовування арифметики за модулем М

Кількість молодших нульових бітів у базі вибрано з умови 2k≥ 90, тодіk= 7.Bs= 128 (крайнє 2k). Верхня межа становить 128 + 90 = 217. Гранична межа становить 128 + 27– 1 = 255; комірки з 218 по 255 повного буфера не використовуються і можуть використовуватись для інших цілей. Після першого виконання команди початкова адреса інкрементується на 15 і вмістR0 дорівнює 180. При подальшому інкрементуванні адреси вмістR0 послідовно стає 195 та 210. При черговому інкрементуванні адреса циклічного буфера могла б стати 225 і вийти за верхню межу буфера. Модульна арифметика примушує вмістR0 залишатися усередині буфера, тобто (R0) = 225 – 90 = 135.

Контрольні питання:

Як вибирається початкова адреса в межах циклічного буфера?

У якій пам’яті, ХабоY, може бути зорганізовано циклічний буфер?

В який спосіб визначаються верхня та нижня межі циклічного буфера?

Контрольні питання підвищеної складності:

З якою метою у DSPвикористовується циклічний буфер?

Організуйте у пам’яті циклічний буфер обсягом сім комірок.

Вкажіть значення нижньої, верхньої та граничної межі в пам’яті циклічного буфера.

Покажіть, як спрацьовує модульна арифметика при обчисленні адреси пам’яті у межах циклічного буфера?