- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

15.2 Узагальнена архітектура процесорів сімейства dsp563xx

Вхідний контроль:

Які операції цифрової обробки сигналів є найпоширенішими?

В який спосіб сприяє гарвардська архітектура підвищенню продуктивності процесорів?

Поясніть, як сприяє режим ПДП підвищенню швидкості обміну даними поміж МПС та периферійними пристроями?

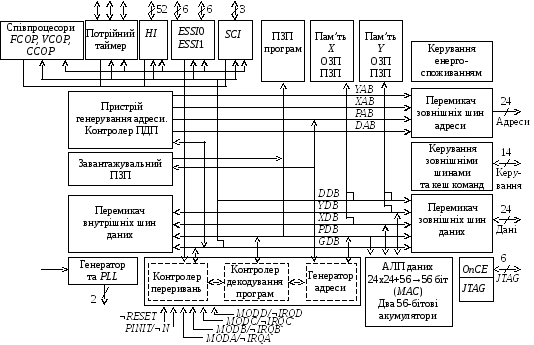

Процесори DSP563ХХвикористовуються в мобільному зв’язку, цифрових системах комутації, пристроях оброблення мовного сигналу, тонального набору, цифрових телевізійних- та радіосистемах, диктофонах, локальних мережах, портативній техніці, відеотелефонах, цифрових фільтрах, аналізаторах спектра, криптографії, системах керування, навігаційному обладнанні, супутниковому зв’язку, розпізнаванні образів тощо.DSP563XXпобудовані за гарвардською архітектурою і мають середню швидкодію 80MIPS.

Периферія вміщує 8-бітний паралельний хост-інтерфейс, 32-бітний універсальний хост-інтерфейс, два розширені синхронні послідовні інтерфейси – ESSI1 таESSI0, послідовний комунікаційний інтерфейсSCI, модуль таймера. На кристалі є вбудовані співпроцесори:

фільтр-співпроцесор FCCP(Filter Сo-Processor), який зреалізовує алгоритми фільтрації;

Вітербі-співпроцесор VCCP (Viterbi Co-Processor), який зреалізовує алгоритм задля відновлення з максимальною вірогідністю сигналу зі спотвореннями, наприкладGSM;

співпроцесор циклічного коду CCOP (Cyclic-code Co-Processor), який зреалізовує кодування та декодування даних, генерування коду парності та контролю.

Підсистема пам’яті – ОЗП програм, кеш інструкцій, ОЗП даних Х, ОЗП данихY– може бути сконфігурована в чотири способи і вміщує також ПЗП програм з організацією 6144х24, ПЗП данихY– 3072х24, ПЗП, яке завантажує програми із зовнішньої пам’яті – 192х24.

Узагальнену архітектуру процесорів сімейства DSP563ХХподано на рис. 15.2.

Сімейство DSP 563ХХвміщує нове ядро, базоване на новітніх технологіях, які зумовили низьку вартість, низьке енергоспоживання, високу ефективність мікропроцесорів. За рахунок включення кеша команд обсягом 1Кх24 процесори припускають підключення повільної зовнішньої пам’яті при зберіганні такої самої ефективності. Продуктивність процесора лінійно залежить від частоти генератора. На кристалі ВІС розміщено синтезатор частоти, порт налагоджуванняJTAG, потрійний таймер,host-інтерфейс (НІ) для

Рисунок 15.2 – Узагальнена архітектура процесорів сімейства DSP563ХХ

побудови багатопроцесорних систем, розширені синхронні послідовні інтерфейси ESSI0 таESSI1, контролер кеша, послідовний комунікаційний інтерфейс SCI, пристрій керування потужністю, шестиканальний контролер ПДП контролер переривань задля оброблення переривань у режимахMODA, MODB, MODC, MODD.

До архітектури процесорів сімейства долучено додаткову шину даних DDB (DMA Data Bus), що дозволяє за допомогою контролера ПДП передавати блоки інформації, не уповільнюючи роботу процесора.

Сімейство DSP563ХХ підтримує промислові стандарти щодо комп’ютерної техніки, мікропроцесорів,DSPта контролерів ПДП.

32-розрядна шина хост-інтерфейса (НІ) зреалізовує три класи інтерфейсів: шиниРСІ, універсальну шину, порт введення-виведення загального призначення.

Сімейство DSP563ХХмає продуктивність 66/80/100MIPSна частотах відповідно 66/80/100 МГц.

Контрольні питання:

Які співпроцесори вбудовуються у кристали сигнальних процесорів сімейства DSP563ХХфірмиMotorola?

У який спосіб пов’язані в архітектурі сигнальних процесорів наявність пам’яті програм, пам’яті ХтаYОЗП, окремих шин до пам’яті цих видів з можливістю виконувати в одній команді операції та кілька пересилань?

У яких областях телекомунікацій використовуються DSP?

Контрольні питання підвищеної складності:

У який спосіб здійснюється тестування сигнальних процесорів відповідно до стандарту ІЕЕЕІІ49.1 черезJTAG-порт?

З якою метою на кристалі DSP563ХХрозташовується синтезатор частоти?