- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

13.3 Налаштовування вбудованих засобів мікроконтролерів

Вхідний контроль:

Які периферійні пристрої входять до складу мікроконтролера МС68НС705J1А?

Для чого використовується регістр MORблока конфігурування МКМС68НС705J1Аі яке призначення мають його окремі розряди?

Яке призначення має блок контролю функціонування МК МС68НС705J1Аі які пристрої входять до його складу?

Яка різниця існує поміж послідовними і паралельними портами мікроконтролера?

Які порти входять до складу МК МС68НС705J1А?

Які регістри входять до складу паралельних портів МК МС68НС705J1А?

За допомогою яких команд можна здійснювати запис до регістра DDRA?

В який спосіб визначається напрямок обміну через паралельний порт МК МС68НС705J1А?

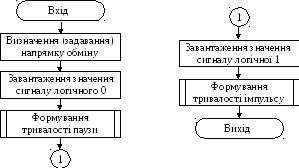

Виводи паралельних портів МК МС68НС705J1Аможна використовувати для обміну будь-якими сигналами. При використовуванні окремих розрядів можна формувати на них сигнали у послідовному вигляді, тобто МК можна використовувати в якості генератора послідовності імпульсів потрібної частоти і щілинності. Блок-схему алгоритму функціонування МКМС68НС705J1Ав якості генератора імпульсів подано на рис. 13.29.

Рисунок 13.29 – Блок-схема алгоритму роботи МС68НС705J1А

в якості генератора імпульсів

Визначення напрямку обміну зумовлюється встановленням відповідного біта в регістрі напрямку пересилання DDRA(адреса $0004) абоDDRB(адреса $0005), як було показано в розділі 13.1.1. Вважаємо, що це будуть всі 8 виводів портуА.

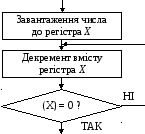

Виведення здійснюється з регістра даних порту PORTA, до якого треба завантажити значення сигналу з акумулятораА. Виведення даних триватиме упродовж такого відтинку часу, допоки сигнали на виходах порту не змінять свого значення. Тому треба сформувати часовий інтервал, котрий визначатиме час формування імпульсу чи то паузи поміж імпульсами. Цей часовий інтервал формується за допомогою підпрограми формування тривалості; вважаємо, що послідовність розпочинається з паузи (рівень логічного 0). Зазвичай формування часових інтервалів може відбуватися за допомогою таймера чи то у програмний спосіб. При формуванні часового інтервалу в програмний спосіб розроблюється циклічна підпрограма, час виконування якої дорівнює заданому часовому інтервалові. При розв’язуванні нашого завдання ця підпрограма може бути побудована за алгоритмом, який подано на рис. 13.30. На цьому рисунку не зазначено блоки входу та виходу, тому що вважається, що робота цієї підпрограми здійснюється згідно з алгоритмом рис. 13.29.

Рисунок 13.30 – Блок-схема алгоритму підпрограми часової затримки

Число, завантажуване до регістра, визначає час затримки підпрограми.

Після виконання цієї підпрограми слід завантажити до регістра даних нове значення сигналу і сформувати часову затримку, що дорівнювала б часові виведення цього значення.

За алгоритмом рис. 13.29, з урахуванням алгоритму рис. 13.30, розроблюємо програму генератора імпульсної послідовності мовою Асемблер:

lda#ff ; Визначення напрямку обміну на виведення

sta$0004 ; даних каналом А

М3: lda#00 ; Завантаження рівня сигналу, який

; виводитиметься каналом А

sta$0000 ; Виведення каналом А сигналу логічного 0

jsrM1 ; Безумовний перехід до підпрограми затримки,

; розташованої за міткою М1

lda#ff ; Встановлення рівня логічної 1 і виведення цього

sta $0000 ; сигналу каналом А

jsrM2 ; Безумовний перехід до підпрограми,

; розташованої за міткою М3

braМ3 ; Безумовний перехід до формування нового

; періоду сигналу

M1: ldx#8 ; Завантаження до індексного регістра Х кількості

; циклів виконування підпрограми формування

; сигналу логічного 0

M4: decx ; підпрограма формування часового інтервалу

; паузи поміж імпульсами. Декремент вмісту

; регістра Х

bneM4 ; Умовний перехід до командиdecx

rts ; Вихід з підпрограми формування часового

; інтервалу паузи поміж імпульсами. Повернення

; здійснюється до команди lda#ff, що є

; наступною за командою звернення до цієї

; підпрограми

M2: ldx #4 ; Завантаження до індексного регістра Х кількості

; циклів виконування підпрограми формування

; сигналу логічної 1

M5: decx ; підпрограма формування одного імпульсу

; з послідовності

; Декремент вмісту регістра Х

bneM5 ; Умовний перехід до командиdecx

rts ; Вихід з підпрограми формування часового

; інтервалу паузи поміж імпульсами. Повернення

; здійснюється до команди bra

Ця програма формуватиме імпульсну послідовність, частота слідування імпульсів в котрій визначатиметься тактовою частотою МК.

Використовуючи таймер, який входить до складу МК, можна також формувати сигнали з потрібною часовою затримкою і використовувати ці сигнали задля керування потрібними об’єктами. Для формування потрібних часових інтервалів можна використовувати сигнали переривання від таймера або від периферійних пристроїв.

Припустімо, що треба розробити програму керування станом об’єкта (періодичне включення/виключеня) по переповнюванні 15-розрядного лічильника багатофункціонального таймера MFT, якщо не надходить сигнал зовнішнього переривання. В разі надходження сигналу зовнішнього переривання, який надходить на вивід 0 портуА, програма формує сигнал логічної 1 на виводі 7 портуА.

Програма, яка функціонуватиме за цим алгоритмом, матиме такий вигляд:

CLRX ; Обнулення індексного регістра Х

LDa#$80 ; Завантаження сигналу включення, який

; виводитиметься у 8-му розряді порту А

STa$0000 ; Включення зовнішнього пристрою по каналу А

LDa#$FE ; Завантаження до регістра А коду, який

; визначатиме виводи порта А РА7...РА1 як

; виходи, а вивід РА0 – як вхід

STA $0004 ; Завантаження коду з регістра А до регістра

; напрямку пересилання DDRA

BSET 5,$0008 ; Встановлення біта дозволу переривання

; переповнювання лічильника у регістрі TSCR

CLI ; Скидання ознаки І в регістрі CCR (дозвіл

; переривання)

M1: JMP M1; Безумовний перехід на ту саму команду задля

; формування затримки формування вихідного

; сигналу до моменту переповнювання лічильника

; у багатофункціональному таймері

М2: BSET 3,$0008; Встановлення біта TOFR (біт скидання ознаки

; переповнювання) у регістрі TSCR

ldA$0000 ; Завантаження до акумулятора А вмісту регістра

; даних PORTA (число #$80)

EOR #$80 ; Обнулення вмісту акумулятора

STA $0000 ; Відключення зовнішнього пристрою по каналу А

; (виведення рівня логічного 0 каналом А)

rtI ; Вихід з підпрограми обслуговування

; переривання (повернення до команди JMP M1)

М3: BSET 1,$000A ; скидання ознаки IRQR (скидання запиту

; на переривання)і скидання ознаки IRQF

; (відсутність запиту на переривання) в регістрі

; ISCR

BSET 7,$0000; Виведення сигналу через вивід 7 PORTA

rtI ; Вихід з підпрограми формування сигналу на

; виводі 7 PORTA

До складу цієї програми входять дві підпрограми, які позначено мітками М2 таМ3. ПідпрограмаМ2 призначена для формування сигналу вимикання зовнішнього пристрою, який підімкнено до портуА. Повернення з цієї підпрограми відбувається до команди, позначеної міткоюМ1, яка формує часову затримку до моменту переповнювання лічильника багатофункціонального таймераMFT. Переповнювання лічильника призводить до встановлення внутрішнього переривання, яке забезпечує циклічне змінювання стану виводу 8 портуА. Для правильного функціонування програми до пам’яті слід завантажувати адреси, до яких здіснюватиметься звернення при виконуванні відповідних переривань.

$07F8 03 0F03 18 03 00 03 00

У комірках пам’яті з адресами $07F8 та $07F9 розміщено початкову адресу підпрограми обробки переривання по переповнюванні лічильника – $030F, в комірках $07FАта $07FВ – початкову адресу підпрограми обробки зовнішнього переривання – $0318 і в наступних комірках – початкову адресу розміщення всієї програми.

Звернення до підпрограми, позначеної міткою М3, здійснюється лише за наявності зовнішнього переривання.

Програма формує часові інтервали, що вони дорівнюють часові виконування 1025 та 1022 машинних тактів МК. Тривалість цих інтервалів можна змінити, встановлюючи потрібні значення RT1-0 в регістріTSCR.

Протокол виконування програми в режимі обробки переривання по переповнюванні лічильника наведено в табл. 13.11. В протоколі не зазначено вміст регістрів, які не використовуються при виконуванні цієї програми: регістра даних порту В, регістра напрямку пересилання порту В та регістраPDRB, а також регістрівISCRтаPDRA, які не змінюють своїх значень, $80 та $00 відповідно. В колонціCYCLESнаведено кількість машинних циклів, яка відповідає виконуванню поточної команди.

Таблиця 13.11 – Протокол виконування програми періодичного

включення/відключення периферійного пристрою за сигналом

переповнення лічильника

|

Команда |

A |

X |

PORTA |

DDRA |

TSCR |

TIMER |

CCR |

CYCLES |

|

CLRX |

XX |

$00 |

XX |

$00 |

$03 |

$00 |

111.I… |

$00 |

|

LDa#$80 |

$80 |

$00 |

XX |

$00 |

$03 |

$00 |

111.I.Z. |

$03 |

|

STa$0000 |

$80 |

$00 |

XX |

$00 |

$03 |

$01 |

111.IN.. |

$05 |

|

LDa#$FE |

$80 |

$00 |

XX |

$00 |

$03 |

$02 |

111.IN.. |

$09 |

|

STA $0004 |

$FE |

$00 |

XX |

$00 |

$03 |

$02 |

111.IN.. |

$0B |

|

Формування сигналу включення | ||||||||

|

BSET 5,$0008 |

$FE |

$00 |

$80 |

$FE |

$03 |

$03 |

111.IN.. |

$0F |

|

CLI |

$FE |

$00 |

$80 |

$FE |

$23 |

$05 |

111.IN.. |

$14 |

|

JMP M1 |

$FE |

$00 |

$80 |

$FE |

$23 |

$05 |

111..N.. |

$16 |

|

… | ||||||||

|

JMP M1 |

$FE |

$00 |

$80 |

$FE |

$23 |

$FF |

111..N.. |

$3FD |

|

JMP M1 |

$FE |

$00 |

$80 |

$FE |

$A3 |

$00 |

111..N.. |

$400 |

|

BSET 3,$0008 |

$FE |

$00 |

$80 |

$FE |

$A3 |

$03 |

111.IN.. |

$40D |

|

ldA$0000 |

$FE |

$00 |

$80 |

$FE |

$23 |

$04 |

111.IN.. |

$412 |

|

EOR #$80 |

$80 |

$00 |

$80 |

$FE |

$23 |

$05 |

111.IN.. |

$415 |

|

STA $0000 |

$00 |

$00 |

$80 |

$FE |

$23 |

$05 |

111.I.Z. |

$417 |

|

rtI |

$00 |

$00 |

$00 |

$FE |

$23 |

$06 |

111.I.Z. |

$41B |

|

Формування сигналу відключення | ||||||||

|

JMP M1 |

$FE |

$00 |

$00 |

$FE |

$23 |

$09 |

111..N.. |

$424 |

|

… | ||||||||

|

JMP M1 |

$FE |

$00 |

$00 |

$FE |

$23 |

$FF |

111..N.. |

$7FC |

|

JMP M1 |

$FE |

$00 |

$00 |

$FE |

$23 |

$FF |

111..N.. |

$7FF |

|

JMP M1 |

$FE |

$00 |

$00 |

$FE |

$A3 |

$00 |

111..N.. |

$802 |

|

BSET 3,$0008 |

$FE |

$00 |

$00 |

$FE |

$A3 |

$03 |

111.IN.. |

$807 |

|

ldA$0000 |

$FE |

$00 |

$00 |

$FE |

$23 |

$05 |

111.IN.. |

$814 |

|

EOR #$80 |

$00 |

$00 |

$00 |

$FE |

$23 |

$05 |

111.I.Z. |

$817 |

|

STA $0000 |

$00 |

$00 |

$00 |

$FE |

$23 |

$06 |

111.IN.. |

$819 |

|

rtI |

$80 |

$00 |

$80 |

$FE |

$23 |

$07 |

111.IN.. |

$81D |

Контрольні питання:

У який спосіб можна задати час затримки, що він формується при виконуванні часової затримки?

У який спосіб можна здійснювати вихід з підпрограми часової затримки за різних способів її побудови?

Чим визначатиметься час затримки при використовуванні переривання за переповнювання лічильника?

Скільки розрядів має регістр-лічильник багатофункціонального таймера MFT?

Контрольні питання підвищеної складності:

В чому полягає призначення бітів RT1-0 і як значення їхнього вмісту можна використовувати задля програмування вбудованих засобів?

У який спосіб можна визначити час формування МК певного інтервалу?

Напишіть програму керування (включення/відключення) певним об’єктом. Включення об’єкта відбувається формуванням сигналу логічної 1 на виводі 7 порту А, а відключення – формуванням сигналу логічного 0 на тому ж самому виводі. Включення відбувається при надходженні сигналу зовнішнього переривання, а відключення через певний час затримки, який формується за допомогою багатофункціонального таймераMFT.