- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

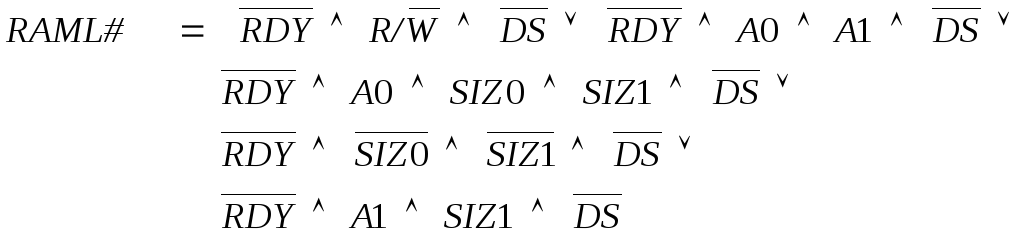

11.4.3 Організація підсистеми пам’яті мпс

Вхідний контроль:

Скільки мікросхем RAMз організацією 16х4 треба задіяти і як їх поєднати, якщо треба побудувати підсистему пам’яті з організацією 16х8?

Скільки мікросхем ROMз організацією 16х8 треба задіяти і як їх поєднати, якщо треба побудувати підсистему пам’яті з організацією 64х8?

За допомогою якого пристрою формуються сигнали вибирання мікросхем пам’яті

?

?Які вхідні сигнали треба подати на мікросхеми пам’яті RAM?

Які вхідні сигнали треба подати на мікросхеми пам’яті ROM?

Які вихідні сигнали знімаються з мікросхем пам’яті і скільки їх може бути?

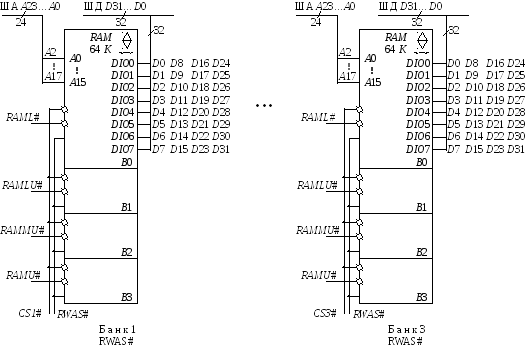

Шина даних D31…D0 МПМС68ЕС020 є тристабільна, двоспрямована, немультиплексована паралельна шина, яка слугує для обміну даними поміж мікропроцесором, пам’яттю та пристроями введення-виведення. За один цикл шини можуть пересилатися 8-, 16-, 24- або 32-розрядні дані.

Пам’ять заданого типу – постійна або оперативна – великого розміру, яка сягає сотен кбайтів або десятків Мбайтів, може бути побудована банками, кожний з яких складається з чотирьох однакових ВІС. Кожна ВІС призначена для зберігання байтів з однаковими індексами: всіх нульових (В0), перших (В1), других (В2) та третіх (В3). Така конфігурація пам’яті дозволяє легко адресувати будь-яку комірку пам’яті у будь-якому з чотирьох шарів банка. Кількість банків залежить від заданого обсягу пам’яті і ємності ВІС, які утворюють ці банки. Припустимо, що треба забезпечити чотиришарову організацію пам’ятіМх 8 кбайт, а в наявності є ВІС оперативної пам’яті з організацієюnх 8. Враховуючи, що один банк складається з чотирьох ВІС, ємність одного банка дорівнює 4 хnх 8 кбайт, а кількість банків, з яких буде побудовано пам’ять, можна обчислити за формулою

![]() ,

,

де М– заданий обсяг пам’яті, аn– обсяг пам’яті однієї ВІС. Припустимо, що заданий обсяг пам’яті дорівнює 750 кбайт, а ємність однієї ВІС – 64 кбайт. Ємність одного банка становить 4 х 64 = 256 кбайт, а кількість банків дорівнюватиме трьом.

Зрозуміло, що адресування будь-якої комірки пам’яті такої конфігурації повинно мати ієрархічну структуру. У адресному просторі пам’яті заданого типу спочатку адресується банк пам’яті, потім шар в обраному банку, а в шарі вже адресується комірка пам’яті.

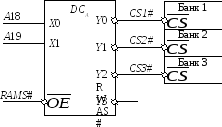

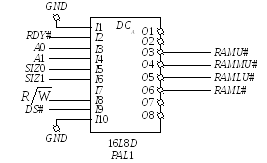

Адресування банків оперативної чи постійної пам’яті можна зреалізовувати за допомогою звичайного декодера адреси, дозвіл на роботу якого дають сигнали RAMS# абоRОMS#, сформованіPAL2. На рис. 11.27 наведено формування сигналів дозволу на роботу банківRAM.

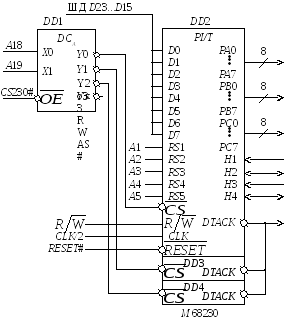

Рисунок 11.27 – Дешифратор адреси банків RAM

ВІС оперативної пам’яті повинні мати

два керувальних входи –

![]() ,

,![]() та вхід

та вхід![]() ,

на який подаються сигнали читання-записуRWAS#. В одному банку всі входи

,

на який подаються сигнали читання-записуRWAS#. В одному банку всі входи![]() може бути сполучено, через те що банк

обирається у цілому. Вибір шару

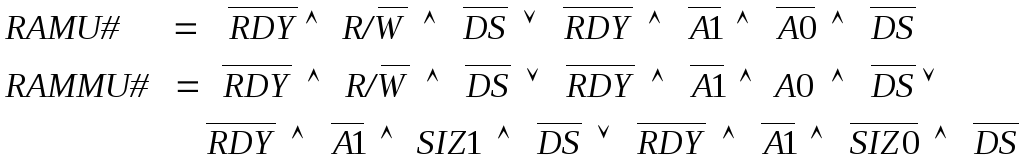

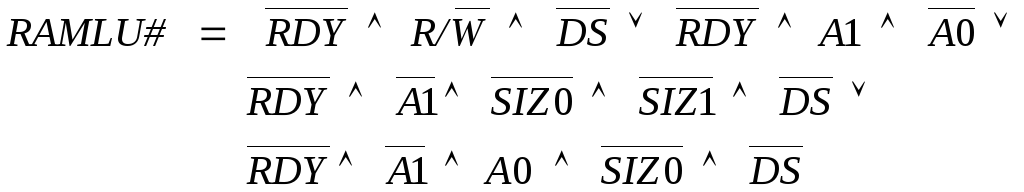

здійснюється сигналамиRAMU# (B3),RAMMU# (B2),RAMLU# (B1),RAML#

(B0), які можуть формуватися ПЛМPAL16L8DфірмиMotorola(PAL1).

Формування вихідних сигналів здійснюється

відповідно до аналітичних виразів:

може бути сполучено, через те що банк

обирається у цілому. Вибір шару

здійснюється сигналамиRAMU# (B3),RAMMU# (B2),RAMLU# (B1),RAML#

(B0), які можуть формуватися ПЛМPAL16L8DфірмиMotorola(PAL1).

Формування вихідних сигналів здійснюється

відповідно до аналітичних виразів:

На рис. 11.28 подано схему декодера адреси шарів пам’яті у банку.

Рисунок 11.28 – Декодер адреси шарів пам’яті у банку

Сигнал RDYє сигнал дозволу роботиRAMабоRОM; він може бути сформований на логічних елементах як логічна сума сигналівROMS# таRAMS#:

![]() .

.

Оскільки розряди адреси А1...А0 використовуються для формування сигналів адреси шарів, на адресні входи ВІС оперативної пам’яті на 64 К подаються адресні розрядиА17...А2, тому на вхід дешифратора банків можна подавати розрядиА18,А19 і, в разі необхідності, –А20 (адресування 8-ми банків).

На рис. 11.29 подано схему підсистеми

пам’яті, яка вміщує оперативну пам’ять.

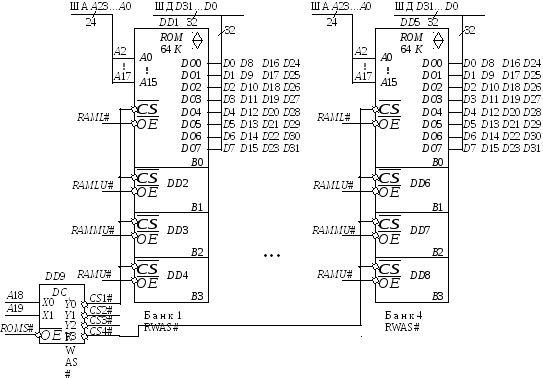

Підсистема пам’яті на RОMбудується

аналогічно, але сигнал![]() не подається (рис. 11.30).

не подається (рис. 11.30).

Контрольні питання:

З якою організацією доцільно використовувати мікросхеми RAMпри побудові банка пам’яті обсягом 64К, яка є чотиришарова?

Скільки мікросхем ROMз організацією 64Ктреба задіяти для побудови пам’яті з організацією 612Кі скільки банків, які вміщують чотири шари, треба зорганізувати?

Який пристрій чи програма забезпечують організацію окремих банків пам’яті для режимів супервізора та користувача МП МС680Х0 фірмиMotorola?

За допомогою якого пристрою розподіляється підпростір адрес, призначених для адресування банків підсистеми пам’яті?

За допомогою якого пристрою формуються сигнали дозволу роботи мікросхем різних шарів?

Як називаються сигнали, які дозволяють роботу шарів банків пам’яті? Як розшифровуються назви цих сигналів?

З якою метою з шини адреси МП М680Х0 на адресування мікросхем пам’яті надходять адресні розряди, розпочинаючи зА2?

Чому на входи Х0 таХ1DCA(див. рис. 11.27) подаються розряди адреси самеА18,А19, а не інші?

Контрольні питання підвищеної складності:

Чи потребують виходи адресних розрядів А31...А0 шинних формувачів і чому?

Чи можуть бути доступними для МП усі 32 розряди даних з чотиришарового банку пам’яті за один цикл шини?

11.4.4 Організація підсистеми введення-виведення

Вхідний контроль:

За скільки циклів мікропроцесора можна передати слово через периферійний інтерфейс/таймер МС68230?

За скільки циклів мікропроцесора можна прийняти довге слово з периферійного інтерфейса/таймера МС68230?

Рисунок 11.29 – Схема підсистеми пам’яті RAM

Рисунок 11.30 – Підсистема пам’яті на RОM

До яких розрядів шини даних МПС підмикаються входи РІ/Т?

Чи може таймер у складі РІ/Твикликати переривання роботи МП?

Чи можна через РІ/Тобмінюватись даними поміж периферійними пристроями та пам’яттю у режимі ПДП?

Якщо у МПС треба зорганізувати два послідовних канали на приймання та три на передавання, скільки ВІС DUARTМС68681 має бути задіяно?

П ідключення

кількох периферійних інтерфейсів-таймерів

та їхнє адресування здійснюється

аналогічно до підключення банків пам’яті

за допомогою декодерів адреси. У якості

сигналу дозволу роботи дешифратора

адреси використовується сигналCS230#.

На рис. 11.31 подано підключення трьохРІ/Т.

ідключення

кількох периферійних інтерфейсів-таймерів

та їхнє адресування здійснюється

аналогічно до підключення банків пам’яті

за допомогою декодерів адреси. У якості

сигналу дозволу роботи дешифратора

адреси використовується сигналCS230#.

На рис. 11.31 подано підключення трьохРІ/Т.

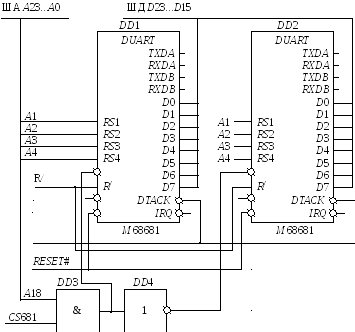

Рисунок 11.31 – Підсистема введення-виведення на трьох РІ/Т

Завдяки наявності тристабільних виводів

РІ/Тпри побудуванні підсистеми

введення-виведення з кількох ВІС

відповідні розрядиD7…D0, виводиDTACKможна підмикати, так само як і

входиR/![]() ,

CLKта

,

CLKта![]() .

Сигнали вибору чіпа подаються з виходів

декодера окремо до входів

.

Сигнали вибору чіпа подаються з виходів

декодера окремо до входів![]() кожногоРІ/Т.Виходи портівРА7...РА0,РВ7...РВ0,РС7...РС0, а також

виводиН1,Н2,Н3,Н4

підмикаються до зовнішніх пристроїв

через розмикачі, які і на рис. 11.31

зазначено лише для верхньої ВІС.

кожногоРІ/Т.Виходи портівРА7...РА0,РВ7...РВ0,РС7...РС0, а також

виводиН1,Н2,Н3,Н4

підмикаються до зовнішніх пристроїв

через розмикачі, які і на рис. 11.31

зазначено лише для верхньої ВІС.

Побудова підсистеми введення-виведення на ВІС DUARTздійснюється аналогічно, а адресний простір для побудови підсистеми можна робити спільним для різних видів інтерфейсів – паралельних та послідовних, якщо їхня кількість є невелика.

На рис. 11.32 наведено частину підсистеми введення-виведення, яка є побудована на DUART.

![]()

![]()

Рисунок 11.32 – Підсистема введення-виведення на двох DUART

Сигнали D7…D0DUARTможна подавати

до шини даних, поєднуючи однакові

розряди, так само можна поєднувати

сигналиR/![]() ,

RESET# таDTACK. На входи

,

RESET# таDTACK. На входи![]() різних ВІС подаються у загальному

випадку сигнали з декодера адреси; у

простому випадку, коли ВІСDUARTє лише

дві, розрядА18, у протилежних фазах

на входи

різних ВІС подаються у загальному

випадку сигнали з декодера адреси; у

простому випадку, коли ВІСDUARTє лише

дві, розрядА18, у протилежних фазах

на входи![]() подається поєднаний з сигналомCS681

на логічному елементі ТА.

подається поєднаний з сигналомCS681

на логічному елементі ТА.

Виходи двох приймачів RXDAта передавачівTXDAчерез підсилювачі-формувачі підмикаються до лінії зв’язку, яка підмикає їх до зовнішніх пристроїв (датчиків, вимірювальних приладів тощо).

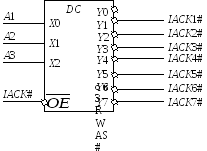

На рис. 11.33 наведено схему дешифратора, який формує сигнали підтвердження переривань IACK, які надходять на сім пристроїв введення-виведення (PI/TтаDUART).

Рисунок 11.33 – Схема формування сигналів IACK

На рис. 11.34 наведено передавання слова через РІ/Тза два цикли шини.

Рисунок 11.34 – Передавання слова через 8-розрядний інтерфейс

Сигнали DTACK# у разі обміну байтами можуть поєднуватись від усіх пристроїв введення-виведення через логічний елемент АБО-НІ і подаватись на входиDSACK1 таAVECмікропроцесора.

На вхід DSACK0 можна подати рівень логічного нуля для визначення розміру передаваного операнда як байта. СигналBERR# формувати не треба, через те що усі розряди шини адрес є задіяні. Режим ПДП не є передбачений, тому на вхідBRмікропроцесора треба подати рівеньL1.

Контрольні питання:

Який адресний простір займають три ВІС МС68230?

За допомогою якого комбінаційного вузла можна підімкнути до МПС три ВІС М68230?

Який адресний простір для кожної ВІС М68230 виокремлюється у схемі, яку наведено на рис. 11.31?

Який адресний простір виокремлюється для кожної ВІС МС68681 у схемі, яку наведено на рис. 11.32?

Контрольні питання підвищеної складності:

Куди надходять сигнали DTACKВІСМС68230 та ВІСМС68681?

У який спосіб формуються сигнали DSACK1 таDSACK0, які подаються на входи МП?

11.4.5 Підключення співпроцесора

Вхідний контроль:

Які функції виконує співпроцесор у складі двопроцесорної системи: центральний процесор – співпроцесор?

Які типи співпроцесорів Ви знаєте?

Який пристрій – центральний процесор або співпроцесор – є ініціатором їхньої спільної роботи?

Робота співпроцесора здійснюється в циклі, коли FC2 =FC1 =FC0 = 1, або, інакше, у просторіCPU.

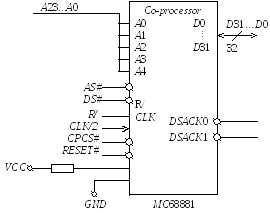

Мікропроцесор МС68ЕС020 припускає підключення співпроцесора обробки чисел з плаваючою точкою типу МС68881; тип процесора визначається кодом, який вміщує поле формату командиCPIDспівпроцесора (рис. 11.35). Мнемоніка команди співпроцесора розпочинається з символу F (1111).

|

15 |

12 |

11 |

9 |

8 |

6 |

5 |

0 |

|

1111 |

CpID |

TYPE |

TD | ||||

|

Додаткові слова (адреса, команди, умови) | |||||||

Рисунок 11.35 – Формат команд співпроцесора

Поле TYPEвизначає тип команди, яку виконує співпроцесор, – код операції, розгалуження за умовою, реалізація циклу тощо. ПолеCDй решта слів команди вміщують додаткову інформацію: адресу операнда, вибір операції, умови тощо.

Після отримання команди співпроцесора мікропроцесор виконує цикл звернення до співпроцесора: FC2,FC1 таFC0 дорівнюють 1, а на шину адреси (рис. 11.36) надходить інформація, яка описує стан шини адреси при зверненні до співпроцесора. Вміст розрядівА19...А13 використовується для адресування операнда зазначеного в команді співпроцесора, а розрядиА4...А0 обирають регістр у складі інтерфейсу співпроцесора, який слугує за джерело або приймач інформації.

|

31 |

20 |

19 |

16 |

15 |

13 |

12 |

5 |

4 |

0 |

|

0 ... 0 |

0010 |

CpID |

0 ... 0 |

Регістр | |||||

Рисунок 11.36 – Призначення розрядів шини адреси

при зверненні до співпроцесора

При зверненні до співпроцесора

мікропроцесор видає сигнали AS#,DS#,R/![]() ,

RESET# і приймає від нього сигнали

підтвердженняDSACK1#,DSACK0#.

,

RESET# і приймає від нього сигнали

підтвердженняDSACK1#,DSACK0#.

При виконуванні команди співпроцесора програмний лічильник мікропроцесора РСвміщує адресу коду операції (першого слова команди). На рис. 11.37 подано ВІС математичного співпроцесораМС68881. Сигнал вибору співпроцесораСРСSформується на ПЛМ або на декодері адреси.

Рисунок 11.37 – ВІС співпроцесора та її підключення

Контрольні питання:

Які поля входять до складу формату команди співпроцесора й що вони визначають?

З якого символу розпочинається кожна команда співпроцесора й чому?

Які пристрої можуть формувати сигнал CS# вибору мікросхеми співпроцесора?

Яку розрядність має шина даних співпроцесора й чому?

Контрольні питання підвищеної складності:

Яку функцію виконують у МПС вихідні сигнали співпроцесора DSACK0# таDSACK1#?

Які типи співпроцесорів може кодувати поле CpID:

а) 000;

б) 001?