- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

11.2.2 Розподіл адресного простору мпс

Вхідний контроль:

З якою метою адресний простір розподіляється поміж різних типів підсистем МПС?

Які вимоги визначають розподіл адресного простору поміж підсистемами МПС?

Які підсистеми МПС входять до адресного простору?

Чим визначається максимальний обсяг адресного простору МПС?

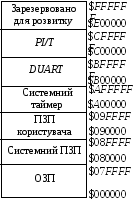

Кожна з підсистем МПС має власну область адрес у адресному просторі МПС. Розподіл адресного простору визначається мапою адрес, котра задає межі адресного простору для кожної з підсистем. Розподіл адресного простору МПС на базі МС68000 здійснено відповідно до мапи адрес материнської плати інтегрованої платформиM68EC0X0IDP. Мапу адрес для МПС наведено на рис. 11.10. Адресний простір, відповідно до мапи, розподіляється поміж модулями: постійного запам’ятовувального пристрою (ПЗП) –ROM, оперативного запам’ятовувального пристрою (ОЗП) –RAM, послідовного порту (інтерфейсу) –DUART, паралельного порту (інтерфейсу) та таймера –PI/T.

Розподіл адресного простору зреалізовано на ВІС FPGA, яка була розглянута вище, і сигналиBACK1 (2, 3, 4, 5) формуються відповідно до мапи. Звернення до ПЗП при вмиканні і перезавантаженні системи виконується апаратно – сигналBACK1 у ці моменти формується примусово.

Рисунок 11.10 – Мапа розподілу адресного простору МПС МС68000

Системний ПЗП призначено для зберігання системних програм: самотестування, початкового завантаження системи тощо.

Область системного таймера призначено задля обслуговування вбудованого таймера, який визначає часові інтервали при роботі системи. Він є енергонезалежним і продовжує функціонувати за вимикання живлення.

Контрольні питання:

Визначте інформаційну ємність кожної з областей мапи розподілу адресного простору МПС МП МС68000?

Які підсистеми МПС позначено в адресному просторі?

Яка з підсистем МПС займає найбільший адресний простір і чому?

Контрольні питання підвищеної складності:

Призначення програмованої логічної інтегральної схеми FPGAу складі підсистеми центрального процесорного елементаМС68000.

Для керування якими пристроями використовуються сигнали BACK1 (2, 3, 4, 5), які формуються на виходах програмованої логічної інтегральної схемиFPGA?

За допомого яких сигналів здійснюється визначання довжини даних, які оброблюються?

11.2.3 Організація підсистеми пам’яті

Вхідний контроль:

Якими параметрами схарактеризовуються пристрої пам’яті?

Визначте кількість мікросхем RAM, необхідних задля побудування блока пам’яті з організацією 64К×8, з мікросхем, які мають організацію 32К×4?

Скільки входів адреси повинна мати мікросхема ROMз організацією 32Кх8?

Які сигнали необхідні задля запису інформації до мікросхем пам’яті RAM?

Які сигнали необхідні задля зчитування інформації з мікросхеми пам’яті RAM?

Яких станів можуть набувати вихідні сигнали тристабільних мікросхем пам’яті?

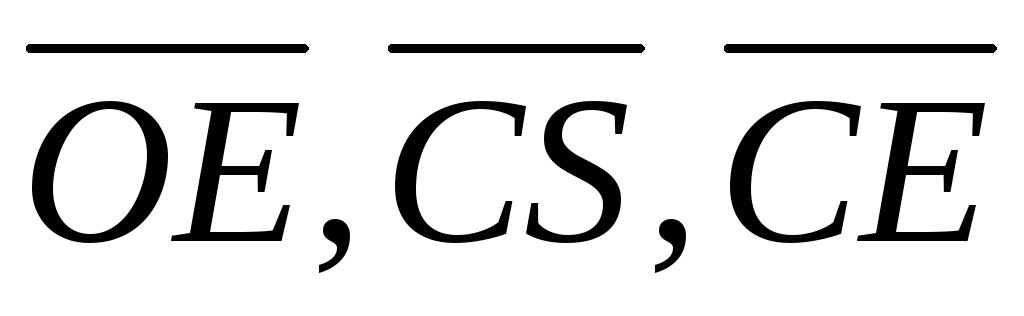

У який спосіб взаємодіють сигнали

поміж собою задля виконування запису

до мікросхеми пам’ятіRAM?

поміж собою задля виконування запису

до мікросхеми пам’ятіRAM?

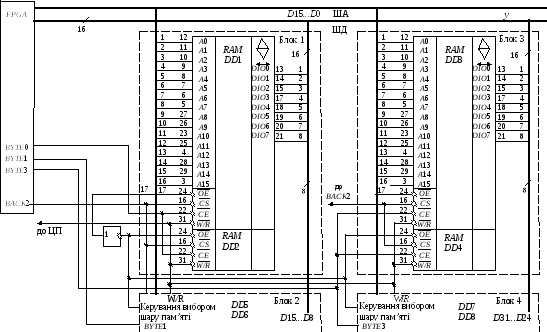

Побудова підсистеми пам’яті здійснюється відповідно до положень розділу 5, котрі доповнюються тим, що ПЗП і ОЗП МПС МС68000 повинні працювати з даними, які можуть бути байтами, словами та довгими словами. Відповідно до цього, водночас можливе звернення до однієї, двох чи чотирьох комірок пам’яті. Шина даних в МПСМС68000 16-розрядна, і робота з довгими словами виконується за два цикли шини, тому при роботі з байтами і словами відбувається звернення до комірок пам’яті з однією адресою, а молодше і старше слова довгих слів розміщуються у двох сусідніх парах комірок. Задля реалізації такого принципу побудови пам’яті необхідно будувати пам’ять з чотирьох блоків, кожен з яких призначено для роботи з байтами даних, поєднуючи їх відповідно до довжини операндів. Організацію такої пам’яті подано на рис. 11.11. Блоки ПЗП та ОЗП будуються в однаковий спосіб.

Рисунок 11.11 – Організація чотириблокової пам’яті

В чотириблоковій пам’яті всі блоки пам’яті до шини адреси під’єднуються паралельно (до одних і тих самих розрядів), що забезпечує звернення до комірок з однаковими номерами. Сигнали вибору блока (BACK) і читання/запис (R/W) також надходять одночасно. Вибір відповідного блока здійснюється за допомогою дешифратора і схеми АБО. Якщо на входи дешифратора надходить код 00 (робота зі словами), то активний сигнал формується лише на виходіY0 і надходить на відповідні входи всіх блоків (на вхід блока 1 він проходить через логічну схему АБО). Отже, водночас всі 16 виводів двох блоків пам’яті будуть з’єднані з шиною даних. Якщо на входи дешифратора надходить код 01 (робота з байтом), то сигналY1 дозволить роботу лише блокові 1; інші блоки в цей момент будуть перебувати в режимі зберігання інформації (будуть неактивними). Задля нарощування інформаційної ємності блока пам’яті збільшується кількість однотипних мікросхем пам’яті у кожному з блоків, відповідно до положень розділу 5.5. Сукупність мікросхем пам’яті в усіх чотирьох блоках, які обслуговують однакові адреси, можна назвати шаром пам’яті. Отже, якщо кожен з блоків пам’яті складається з кількох мікросхем пам’яті, то можна говорити про використовування багатошарової пам’яті.

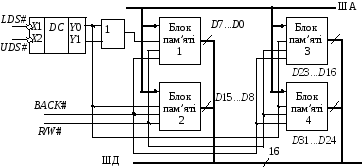

Побудова кожного з блоків пам’яті здійснюється відповідно до положень розділу 5.5. Припустімо, що треба побудувати ОЗП з організацією 115К×8 з мікросхемАМ21С512, які було розглянуто в розділі 5.5. ОЗП має працювати з байтами, словами та подвійними словами. Кількість мікросхем, потрібних для побудови, визначатиметься за виразом

![]() ,

,

де 4 – кількість блоків пам’яті; 115К×8 – організація ОЗП кожного з блоків; 64К×8 – організація мікросхемиАМ21С512.

Якщо у результаті здобуто дробове число, то його слід заокруглювати обов’язково до більшого цілого числа.

Отже, блок ОЗП вміщуватиме чотири блоки пам’яті, кожен з яких складатиметься з двох мікросхем. Схему цієї пам’яті наведено на рис. 11.12.

Керування схемою здійснюється сигналами,

які формуються ВІС FPGA. Сумарний

обсяг пам’яті кожного блока 128К.

Блок 1 може працювати з байтами, сумісно

з блоком 2 – зі словами і всі чотири

блоки – з довгими словами. Молодша

частина довгого слова оброблюється

блоками 1 та 2, старша – блоками 3 та 4.

Керування шарами пам’яті в кожному з

блоків здійснюється за сигналом адресиА16 у такий спосіб, що молодші комірки

пам’яті з адресами $00000...$0FFFFоброблюються верхньою (за схемою)

мікросхемою, а старші з адресами

$10000...$1FFFF– нижньою. Задля керування

використовується вхід![]() ,

на котрий подається або сам сигналА16,

або його інверсія. Отже, якщо на вхід

верхньої мікросхеми надходить сигнал

безпосередньо з шини адреси, то в

діапазоні адрес $10000...$1FFFFроботу

цього блока буде заборонено.

,

на котрий подається або сам сигналА16,

або його інверсія. Отже, якщо на вхід

верхньої мікросхеми надходить сигнал

безпосередньо з шини адреси, то в

діапазоні адрес $10000...$1FFFFроботу

цього блока буде заборонено.

Контрольні питання:

Чому при побудові МПС на МП МС68000 рекомендовано використовувати пам’ять, яка складається з чотирьох блоків?

У який спосіб зорганізовується робота блоків при роботі з даними різної розрядності?

Який пристрій керує роботою блоків пам’яті МПС на МП МС68000?

Для чого використовується багатошарова пам’ять?

Чи є обов’язковим використовування багатошарової пам’яті?

За допомогою яких сигналів та пристроїв здійснюється вибір шарів блоків пам’яті?

Контрольні питання підвищеної складності:

Розробити схему ПЗП з організацією 128×8 задля зберігання даних у вигляді байта, слова і довгого слова, використовуючи мікросхеми пам’яті, які наведено в розділі 5.5.

Які сигнали керують вибором шару для роботи блоків пам’яті і з якого пристрою вони надходять?

У який спосіб взаємодіють поміж собою блоки пам’яті при роботі з операндами різної розрядності?

За скільки циклів 32-розрядні дані може бути записано до пам’яті RAM?

Рисунок 11.12 – Принципова схема блока пам’яті