- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

Вхідний контроль:

Які технології виробництва мікросхем Ви знаєте?

Чим відрізняються одна від одної мікросхеми з різними технологіями?

Флеш-пам’ять (Flash-пам’ять). Мікросхеми пам’яті такого типу були розроблені фірмою Intel у 1988 році.

Як ЕП флеш-пам’яті використовується МОН-транзистор з ПЗ, який виготовлено за спеціальною технологією, яка називається ETOX (EPROM Thin Oxide) і запатентована фірмоюIntel. У цілому, структура МОН-транзистора з ПЗ подібна описаним вище. Відмінністю, яка забезпечуються технологієюETOX,є зменшення товщини прошарку оксиду кремнію більш ніж втричі, що дозволило зменшити напругу програмування до 12 В і зменшити напругу стирання за рахунок тунельного ефекту, також до 12 В. Ці заходи дозволяють виконувати перепрограмування флеш-пам’яті безпосередньо у складі МПС і забезпечують можливість збільшення кількості циклів запису інформації.

Для забезпечення правильної організації роботи флеш-пам’яті фірмою Intelрозроблена низка заходів, що дозволяють уникнути виходу її з ладу під час програмування. До них можна віднести:

застосування спеціальних алгоритмів запису і стирання з контролем стану і завершенням процесу за результатами контролю;

попереднє програмування в режимі стирання, коли перед стиранням усі ЕП матриці установлюються в стан 0;

включення до складу мікросхеми регістра, який зберігає ідентифікатори фірми-виробника й типу мікросхеми, що дозволяє захистити елемент від помилок вибору алгоритму;

вбудування в мікросхему кіл, що реалізують алгоритм стирання і запису. Це спрощує зовнішнє керування і захищає від помилок під час перезапису.

Існує три групи мікросхем флеш-пам’яті:

мікросхеми першого покоління, які виготовлені у вигляді єдиного масиву (блока), інформація в якому стирається цілком (BULK-ERASE);

мікросхеми, масив пам’яті яких поділено на блоки різного розміру, що мають різні рівні захисту від випадкового звернення до них (BOOT-BLOCK);

мікросхеми третього покоління, які мають найбільший розмір масиву, що поділено на блоки однакового розміру з незалежним стиранням (FLASH-FILE).

Мікросхеми різних груп мають відмінності в їх використанні. Так, мікросхеми BULK-ERASEможуть використовуватись замість традиційних мікросхемEPROM, з можливістю перепрограмування безпосередньо у складі обладнання під керівництвом процесора самої системи. МікросхемиBOOT-BLOCKзастосовуються для зберіганняBIOSу персональних комп’ютерах, що дає можливість оновлення системи безпосередньо з зовнішніх носіїв інформації. МікросхемиFLASH-FILEвикористовуються для зберігання даних великого обсягу вFlash-картах, які є альтернативою жорстким магнітним дискам. Очікується, щоFlash-картки зможуть замінити жорсткі магнітні диски, особливо у системах, що працюють в умовах сильних механічних впливів.

Швидкодія флеш-пам’яті в 125…250 разів перевищує цей параметр для жорсткого диска, але поступається йому щодо інформаційної ємності.

Напруга живлення мікросхем флеш-пам’яті становить – 5 В, а стирання і програмування –12 В. Споживаний струм суттєво залежить від режиму роботи мікросхеми. Так, в режимі очікування (Standby) споживаний струм значно менший за струм, який споживається у режимі стирання і запису, переважно у колі джерела 12 В.

Більшість мікросхем флеш-пам’яті працюють з даними у вигляді послідовного коду з використанням шини І2С (Inter Integrated Circuit Bus). Ця шина складається з двох двонаправлених ліній:SСL(Serial Clock) іSDA(Serial Date), до яких можна підключати до 128 пристроїв. Один з пристроїв є ведучим (master), інші – веденими (slave). Ведучий пристрій генерує імпульси синхронізаціїSСLі керує всією роботою шини. Ведені працюють під керуванням ведучого, обслуговуючи його запити.

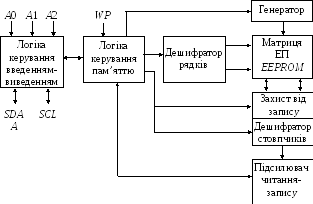

Типова структурна схема мікросхеми флеш-пам’яті з послідовним введенням-виведенням інформації з використанням шини І2Споказана на рис. 5.1.

Рисунок 5.1 – Структурна схема ВІС флеш-пам’яті, що працює з шиною І2С

На рис. 5.1 на блок логіки керування введенням-виведенням інформації надходять з шини І2СсигналиA0,A1,A2, які визначають три молодші розряди адреси веденої ВІС, а старші чотири розряди адреси пам’яті не змінюються і мають значення 1010. По лініяхSСLіSDAпроводиться обмін відповідними сигналами. ВхідWP(Write Protect) блока логіки керування пам’яттю призначений для керування захистом даних, що записані у ВІС. Якщо цей вивід з’єднаний з загальним проводом, то можливо змінювати вміст будь-яких комірок пам’яті. Сигнал високого рівня, що подано на цей вивід захищає увесь масив даних або його частину від змін. Нині випускаються мікросхеми, в яких блокування стирання і запису можливо виконувати в інший спосіб, наприклад, за командами ведучого.

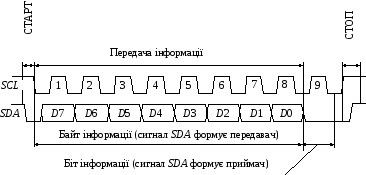

У неактивному стані шини І2Сна лініяхSСLіSDAприсутні високі рівні сигналу. Для початку сеансу роботи ведучий змінює стан лініїSDAна низький, не змінюючи стану лініїSСL. Після установлення низького рівня на лініїSDAзмінюється стан лініїSСL,що відповідає команді СТАРТ. Передавання інформації відбувається побітно. Сеанс передавання закінчується командою СТОП, під час якої на лініїSСLустановлюється високий рівень сигналу і за його наявності відбувається зміна стану лініїSDA. Часові діаграми процесу передавання інформації показано на рис. 5.2.

Рисунок 5.2 – Часові діаграми процесу передавання інформації

Частота проходження імпульсів синхронізації SСLстановить 100 (400) кГц. При передаванні першим передається старший байт, а останнім – молодший. Пристрій, який прийняв байт, підтверджує його прийом, установлюючи на лініїSDAсигнал низького рівня, після чого формується сигнал СТОП.

Сім бітів, що передаються безпосередньо за командою СТАРТ, є адресою веденого пристрою, з яким необхідно установити зв’язок. Пристрій з такою адресою підтверджує приймання і готується до наступної роботи. Якщо у МПС немає пристрою з адресою, що передана по шині, то всі пристрої відключаються.

Молодший біт першого байта – це ознака напряму передавання. Значення 0 цього біта відповідає напряму від ведучого до веденого і не може змінитися у поточному сеансі роботи.

Контрольні питання:

Як проводиться програмування ПЗП, програмованих маскою?

Який пристрій використовується як елемент пам’яті у ПЗП з ультрафіолетовим стиранням?

Як відбувається робота флеш-пам’яті з шиною I2C?

Контрольні питання підвищеної складності:

Які заходи застосовуються для уникнення виходу з ладу ВІС флеш-пам’яті?

Які типи ВІС флеш-пам’яті Ви знаєте?

Чим відрізняються ВІС РПЗП-УФ від ВІС РПЗП-ЕС?