РГР3.2014 / Методические указания к РГР3

.pdfМетодические указания к расчѐтно-графическому заданию по дисциплине

«Электроника и микропроцессорная техника»

1. Общие положения.

Методические указания разработаны в соответствии с программой дисциплины «Электроника и микропроцессорная техника» для студентов специальности ________________ и содержат общие рекомендации по синтезу и схемной реализации цифрового устройства с временным разделением выходных сигналов.

Содержание РГЗ базируется на материале, излагаемом в ряде курсов:

высшая математика, физика, электротехника. Основные положения этих курсов студенты должны использовать при выполнении РГЗ, в котором в соответствии с заданием необходимо разработать цифровое устройство на

интегральных микросхемах (ИМС), обеспечивающее формирование прямоугольного сигнала заданной частоты fг (скважность 2) и периодической последовательности из 16-ти тактов логического сигнала Y с заданным периодом Tвых с возможностью включения и выключения формирователей выходных сигналов посредством замыкания «сухих контактов» - кнопок

«Пуск» и « Стоп».

Методические указания определяют цели и задачи РГЗ, включая основные требования к объему, содержанию и порядку выполнения,

оформлению и защите. В них приводится перечень исходных данных для синтеза схемы, обобщенная структурная схема устройства, общие рекомендации по минимизации логических функций и их схемной реализации в элементных базисах И-НЕ, И-ИЛИ-НЕ, общая методика расчета симметричного автоколебательного мультивибратора, перечень источников информации,

ГОСТов, ДСТУ.

2. Цель расчётно-графического задания.

Основной задачей РГЗ по дисциплине «Электроника и микропроцессорная техника» является практическое использование теоретического материала по данному курсу при синтезе и схемной реализации реального цифрового устройства: минимизация логических функций с целью получения структуры устройства минимальной сложности; выбор оптимальной структуры обобщенной комбинационной схемы, выполненной на цифровых ИМС; выбор и электрический расчет автогенератора релаксационных колебаний; применение современных методов расчета электронных схем;

использование справочной литературы, ГОСТов, ЕСКД, ДСТУ.

3. Методические указания к основной (расчетной) части.

3.1. Исходные данные.

В общем случае логическая функция, определяющие алгоритм формирования 16-ти тактов логического сигнала, может быть задан в виде:

таблицы истинности, в которой для всех возможных комбинаций n-логических переменных (N=2n) указываются значения самой функции в двоичном коде; в

алгебраической форме в виде совершенной дизъюнктивной нормальной формы

(СДНФ); ); в числовой форме в виде суммы соответствующих минтермов логической функции F= (mi).

В задании к данному РГЗ исходная логическая функция Y представлена в виде таблицы истинности, в которой для всех возможных комбинаций n

логических переменных (N=2n) указываются значения самой функци в двоичном коде.

Значения логической функций Y формируются на выходе разрабатываемого цифрового устройства формируются путем последовательного перебора 16 состояний входных переменных (X1,X2,X3,X4)

подачей на вход комбинационной схемы реализующей Y циклического нарастающего четырехразрядного двоичного кода с заданным периодом цикла

Tвых., при этом управляюшее устройство обеспечивает возможность включения и выключения формирователей выходных сигналов Y и сигналов автоколебательного генератора тактовых импульсов (ГТИ) заданной частоты fг

и скважности посредством замыкания «сухих контактов» - кнопок «Пуск» и «

Стоп».

3.2. Структурная схема цифрового логического устройства.

Структурная схема устройства отображает принцип работы изделия в самом общем виде, при этом на схеме изображают все основные функциональные части изделия (элементы, устройства, функциональные группы), а также основные взаимосвязи между ними. Построение структурной схемы должно давать наглядное представление о последовательности взаимодействия функциональных частей изделия. Направление хода процессов,

происходящих в устройствах, обозначают стрелками на линиях взаимосвязи.

Функциональные части на схеме изображают в виде прямоугольников, при этом наименования, типы и обозначения функциональных частей вписывают внутрь прямоугольников.

Поставленная в задании к РГЗ цель схемной реализации цифрового устройства формирования сигналов в общем случае может быть реализована в структурной схеме (рисунок 1)

Рис 1.Структурная схема устройства.

В приведенной структурной схеме разрабатываемого цифрового устройства генератор тактовых импульсов (ГТИ) формирует на выходе прямоугольный сигнал потенциального типа с заданной частотой fг,

совместимый по параметрам с потенциальными уровнями цифровых ИМС

предварительного делителя частоты, комбинационной логической схемы

и остальных узлов устройства.

Предварительный делитель частоты это счетчик-делитель с постоянным кооффициентом деления формирующий на входе узла сканирования прямоугольный сигнал потенциального типа с частотой

f*= fвых*16. |

|

Узел сканирования – черырехразрядный двоичный счетчик |

с |

асинхронным сбросом формирующий на входах X1--X4 комбинационной

логической схемы циклический нарастающий четырехразрядный двоичный код от X1=0, X2=0, X3=0, X4=0 до X1=1, X2=1, X3=1, X4=1.

Комбинационная логическая схема (КС) формирует потенциальные уровни сигналов, соответствующие значениям функции Y=F(X1,X2,X3,X4)

заданой в табличном виде, при этом КС должна иметь минимальную сложность схемной реализации и быть выполненной с использованием

минимального числа корпусов цифровых ИМС.

Значения логической функций Y с выхода комбинационной схемы и fг с

выхода генератора тактовых импульсов подаются на выходные логические устройства (ЛУ1, ЛУ2), которые обеспечивают передачу значений функции Y

и fг на выход цифрового устройства только при поступлении разрешающего

сигнала из узла управления.

Узел управления - цифровая логическая схема на основе асинхронного

RS-триггера формирующая логические сигналы управления узлом

сканирования, выходными логическими устройствами (ЛУ1, ЛУ2) и

индикатором включения режима формирования выходных сигналов.

RS-триггер управляется логическими сигналами сформироваными

посредством замыкания «сухих контактов» - кнопок «Пуск» и « Стоп» и

схемы автоматического сброса при включении питания.

Индикатор включения выходного устройства – схема индикации,

построенная на базе дискретного (ных) светодиода(дов).

4. Расчет и проектирование узлов цифрового логического устройства.

4.1. Разработка схемы генератора таковых импульсов (ГТИ).

Функциональное назначение генератора тактовых импульсов (ГТИ)

заключается в генерировании последовательности прямоугольных импульсов с заданной частотой, амплитудой и скважностью.

Электрические параметры этих импульсов должны быть совместимы с основными параметрами цифровых ИМС предварительного делителя,

комбинационной логической схемы (КС), в т.ч. входными и выходными напряжениями логической единицы U1вх , U1вых и логического нуля U0вх , U0вых , при

этом скважность выходных импульсов Q T / tи может быть равна двум, но может и отличаться от этого значения. Скважность выходных импульсов ГТИ указана в задании на курсовой проект.

В качестве одной из возможных схем ГТИ может быть применен генератор на логических элементах НЕ, схемная реализация которого осуществляется на одной микросхеме КМОП СD4001 (К561ЛЕ5), имеющей в своем составе четыре логических элемента 2ИЛИ-НЕ. Соединив между собой

входы каждого |

логического элемента |

ИМС К561ЛЕ5, |

получим четыре |

|

инвертора (рис 2.) . |

|

|

|

|

U1:A |

|

U1:B |

U1:C |

|

|

5 |

U1:D |

||

1 |

|

4 |

8 |

|

|

3 |

6 |

10 |

12 |

2 |

|

|

9 |

11 |

|

|

4001 |

|

13 |

4001 |

|

|

4001 |

|

|

|

|

|

4001 |

Рис. 2.

Соединим их последовательно и охватим первые три (U1.a,U1.b, U1.c)

параллельной отрицательной обратной связью по напряжению, подключив резистор R1 между выходом U1.c и входами U1.a (см.рис.3.) При этом коэффициент усиления по напряжению схемы из трех последовательно включенных инверторов уменьшается и соответственно расширяется линейный участок передаточной (статической) характеристики.

R1

|

|

10000 |

|

U1:A |

|

U1:B |

U1:C |

5 |

|

||

1 |

|

4 |

8 |

3 |

6 |

|

10 |

2 |

|

|

9 |

|

|

4001 |

|

4001 |

|

|

4001 |

U1:D

12 |

|

|

|

11 |

fg |

13 |

|

|

|

|

4001

Рис. 3.

Охватим инверторы U1.A и U1.B частотнозависимой параллельной обратной связью по напряжению, подключив конденсатор С1 между выходом

U1.B и входами U1.A. (см. рис. 4.)

|

R1 |

|

|

|

|

|

10000 |

|

|

|

|

U1:A |

U1:B |

U1:C |

|

|

|

5 |

|

U1:D |

|

||

1 |

4 |

8 |

|

|

|

3 |

6 |

10 |

12 |

|

|

2 |

|

9 |

|

11 |

fg |

|

4001 |

|

13 |

|

|

|

|

|

|

||

4001 |

|

4001 |

|

|

|

|

|

|

|

4001 |

|

|

|

C1 |

|

|

|

|

|

100nF |

|

|

|

Рис.4.

Полноценный выходной сигнал в виде последовательности прямоугольных импульсов с коэффициентом разветвления 10 формируется на выходе 11(U1.D). Частота выходного сигнала генератора определяется параметрами цепей обратных связей - сопротивления R1 и конденсатора C1.

Fg=0.42/R*C

Конденсатор С1 должен быть неполярным с малым температурным коэффициентом емкости (ТКЕ), рабочим напряжением больше 16 В (например К73-17 или К10-17. см. приложение 1.), номинальное значение емкости конденсатора выбирается по ряду Е6 в диапазоне от 1нф до 1000нф. Резистор

R1 металлопленочный с температурным коэффициентом сопротивления (ТКС)

менее 100 ppm, рассеиваемой мощностью 0,125 Вт (например С2-14, С2-29,

С2-23, MFR, С2-33 см. приложение 1.). Номинальное значение сопротивления резистора выбирается из рядов Е24, Е96 или Е192 в диапазоне от 1кОм до 100

кОм.

4.2. Разработка схемы предварительного делителя частоты.

Схема предварительного делителя с постоянным кооффициентом деления формирует на входе узла сканирования прямоугольный сигнал потенциального типа с частотой f*= fвых*16, в случае, если коэффициент деления K=Fg/ f* кратен 2n , она может быть построена, например, на базе КМОП ИМС CD4520, состоящей из двух четырехразрядных синхронных двоичных счетчиков со сбросом (см рис 5.)

|

|

U2:A |

|

|

|

|

U2:B |

|

|

|

||

|

1 |

|

CLK |

Q0 |

3 |

|

9 |

|

CLK |

Q0 |

11 |

|

2 |

|

4 |

10 |

|

12 |

|

||||||

|

E |

Q1 |

|

E |

Q1 |

|

||||||

|

|

|

5 |

|

|

|

13 |

|

||||

|

|

|

|

Q2 |

|

|

|

|

Q2 |

|

||

7 |

|

|

6 |

15 |

|

|

14 |

|

||||

|

MR |

Q3 |

|

MR |

Q3 |

|

||||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4520 |

|

|

|

|

4520 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.5.

Включив последовательно несколько счетчиков, можно на одном из выходов получить требуемую частоту выходного сигнала f*=fвых *16 (см. рис 6).

Fg

|

R6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

U3:A |

|

3 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

10k |

|

|

|

U2:A |

|

|

|

|

|

|

|

|

|

|

CLK |

Q0 |

|

Fg/512 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

4 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

Q1 |

|

|

|

|

|

|

|

|

1 |

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|||

|

|

|

|

|

CLK |

Q0 |

|

Fg/2 |

|

|

|

|

|

Q2 |

|

|

||||||||||

|

|

|

|

2 |

|

4 |

|

7 |

|

|

6 |

|

|

|||||||||||||

|

|

|

|

|

E |

Q1 |

|

|

|

|

|

|

|

|

MR |

Q3 |

|

|

||||||||

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

6 |

|

|

|

|

|

|

|

|

|

|

4520 |

|

|

|

|

||||

|

|

|

|

|

MR |

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4520 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U3:B |

|

|

|

|

|

|

|

|

U2:B |

|

|

|

9 |

|

11 |

||||||||||

|

|

|

|

|

|

|

|

|

CLK |

Q0 |

|||||||||||

|

|

|

9 |

|

|

|

11 |

|

|

|

|

10 |

|

12 |

|||||||

|

|

|

CLK |

Q0 |

|

|

E |

Q1 |

|||||||||||||

|

|

10 |

|

12 |

|

|

|

|

|

|

|

|

|

|

13 |

||||||

|

|

|

E |

Q1 |

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|||||

|

|

|

|

|

|

13 |

|

15 |

|

|

14 |

||||||||||

|

|

|

|

|

|

|

Q2 |

|

|

MR |

Q3 |

||||||||||

|

|

|

15 |

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

MR |

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4520 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

4520 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.6.

Если полученный коэффициент делеления не кратен 2n, то счетчик-

делитель необходимо либо дополнить комбинационной логической схемой формирующей сигнал сброса при заданом коде на выходе счетчика, либо применить счетчики с параллельной записью (предустановкой) начального кода.

4.3. Разработка узла сканирования.

Узел сканирования - черырехразрядный двоичный счетчик,

формирующий на выходах циклический нарастающий четырехразрядный

двоичный код. Он должен быть синхронным и иметь вход асинхронного сброса. Требование синхронности связано с необходимостью одновременной смены состояний выходных сигналов Х1-Х4. В противном случае на выходе комбинационной логической схемы устройства возможно появление кратковременных ложных логических состояний (импульсов), длительность которых соизмерима со временем смены кода (переключения) асинхронного счетчика.

4.4. Синтез комбинационной схемы цифрового устройства.

Рассмотрим пример синтеза с минимизацией комбинационного устройства, заданного таблицей функционирования (см. табл. 1). Воспользуемся для минимизации методом карт Карно. Преимуществом таблиц Карно (см.рис.7) является простота обнаружения возможных упрощений логической функции.

В первую очередь при составлении дизъюнктивной нормальной формы (ДНФ) следует составить логическое произведение всех входных переменных для каждой ячейки, в которой стоит единица. Для ячейки, расположенной в левом верхнем углу получается:

Для ячейки, расположенной правее следует записать:

Таблица _1___.

Рис. 7. Таблица Карно Таким образом, в логической сумме всех произведений встретится такой фрагмент:

,

,

который упрощается следующим образом:

Отсюда следует общее правило упрощения логических функций для таб-лиц Карно:

если в двух, четырех, восьми и т. д. (2n) ячейках, ограниченных прямоугольным и квадратным контуром, стоят только единицы, можно

записывать непосредственно логическое произведение для всей этой группы, причем в это произведение должны входить лишь те входные переменные, которые остаются неизменными для всех ячеек данной группы. Таким образом, в этом примере логическое произведение для группы В, состоящей из двух ячеек, равно:

,

,

что соответствует ранее полученной функции.

В одну группу связываются также те ячейки, которые находятся на левом и правом краях одной строки (2nсоседних строк) или в верхней и нижней частях одного столбца (2nсоседних столбцов).

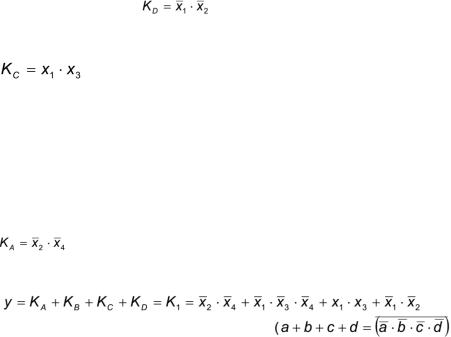

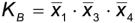

Для столбца D, состоящего из четырех ячеек, можно записать:

Для контура С, имеющего квадратную форму и состоящего также из четырех элементов, получим следующее логическое произведение:

Еще одна единица осталась в правом верхнем углу. Она может быть свя-зана, например, с единицей в нижней части рассматриваемого столбца в группу, содержащую две ячейки. Другая возможность состоит в объединении единиц находящихся на левом и правом краях первой строки. Однако, если принять во внимание, что в каждом углу таблицы Карно находится единица, то можно найти простейшее решение. Связывая эти единицы в одну четырехэлементную группу A, получим:

Для дизъюнктивно нормальной формы (ДНФ) с помощью таблиц Карно сразу находим максимально упрощенный результат:

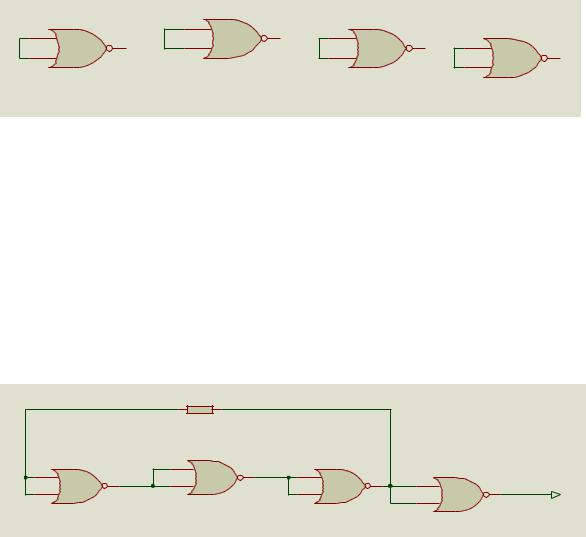

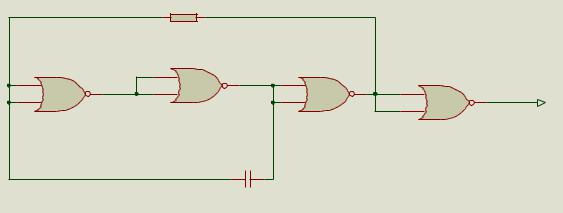

Используя теорему де Моргана и учитывая выбранный базис логических элементов (И-НЕ или NAND), представим схемотехническую реализацию заданной функции в виде принципиальной электрической схемы ( рис. 8).

а)

б)

б)