- •В коде Бодо

- •Тактируемый rs-триггер

- •Тактируемый rs-триггер

- •Исключающее или

- •Исключающее или – не

- •Исключающее или

- •Исключающее или-не

- •Исключающее или

- •Исключающее или

- •Исключающее или

- •Исключающее или-не

- •Исключающее или

- •Исключающее или

- •Исключающее или

- •Исключающее или

- •Исключающее или

- •Исключающее или

-

Тактируемый rs-триггер

4. Какой триггер называют счетным?

-

T-триггер

-

JK-триггер

-

D-триггер

-

RS-триггер

-

Тактируемый rs-триггер

5. Какой из логических элементов называют иногда элементом типа «что нибудь или все»?

-

логический элемент ИЛИ

-

логический элемент И

-

инвертор

-

логический элемент И-НЕ

-

логический элемент исключающее ИЛИ

6. Какой из перечисленных символов используется для обозначения функции исключающее ИЛИ?

7. Логический элемент, обладающий двумя устойчивыми состояниями называется:

-

триггером

-

сумматором

-

шифратором

-

кодопреобразователем

-

операционным усилителем

8. Соединяя триггеры друг с другом, можно получить:

-

различные запоминающие устройства

-

арифметические устройства

-

компараторы

-

кодопреобразователи

-

шифраторы специального типа

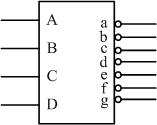

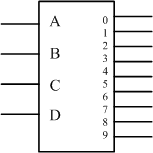

9. На рисунке изображено условное обозначение:

-

мультиплексора “1 из 8”

-

селектора данных “1 из 16”

-

демультиплексора

-

дешифратора

-

шифратора

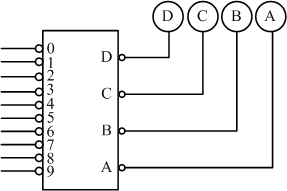

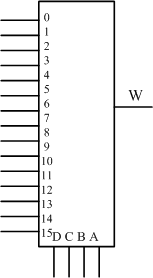

10. На рисунке изображено условное обозначение:

-

дешифратора – формирователя

-

шифратора

-

дешифратора

-

мультиплексора “1 из 16”

-

селектор данных “1 из 8”

$$8$$

1. Счетчик, в котором запуск триггеров осуществляется в один и тот же момент времени, называется:

-

синхронным счетчиком

-

счетчиком со сквозным переносом

-

асинхронным счетчиком

-

кодированным

-

пульсирующим

2. Параллельные сумматоры относятся к классу:

-

комбинационных логических схем

-

комбинированных логических схем

-

последовательностных логических схем

-

параллельных логических схем

-

резистивных схем

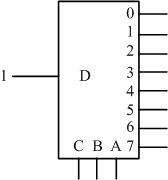

3. На рисунке дано условное обозначение:

-

шифратора на 10 входов и 4 выхода

-

мультиплексора “1 из 16”

-

дешифратора

-

мультиплексора “1 из 8”

-

дешифратора – формирователя

4. На рисунке изображено условное обозначение:

-

демультиплексора “1 из 8”

-

селектора данных “1 из 16”

-

мультиплексора “ 1 из 8”

-

шифратора

-

дешифратора

5. Трёхразрядный параллельный сумматор состоит из:

-

одного полусумматора и двух полных сумматоров

-

одного полного сумматора и двух полусумматоров

-

одного полусумматора и трёх полусумматоров

-

трёх полных сумматоров

-

трёх полусумматоров

6. Последовательный сумматор содержит:

-

1 полный сумматор и два регистра сдвига, регистр суммы и D-триггер задержки

-

1 полусумматор и 3 полных сумматора

-

1 полусумматор и 4 полных сумматора

-

4 полусумматора

-

4 полных сумматора

7. Четырехразрядный параллельный вычитатель состоит из:

-

одного полувычитателя и трех полных вычитателей

-

четырех полных вычитателей

-

двух полувычитателей и двух полных вычитателей

-

одного полного вычитателя и трех полувычитателей

-

четырех полувычитателей

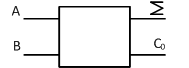

8. На рисунке дано условное обозначение:

-

полусумматора

-

полувычитателя

-

полного вычитателя

-

полного сумматора

-

последовательного вычитателя

9. На рисунке дано условное обозначение:

-

дешифратора

-

дешифратора-формирователя

-

шифратора

-

мультиплексора

-

демультиплексора

10. На рисунке изображено условное обозначение:

-

селектора данных “ 1 из 16 ”

-

демультиплексора

-

селектора данных “ 1 из 8 ”

-

шифратора приоритетов

-

дешифратора

$$9$$

1. Устройство, осуществляющее преобразование двоично-десятичного кода в семисегментный код, называется:

-

дешифратором-формирователем

-

шифратором

-

мультиплексором

-

демультиплексором

-

мультивибратором

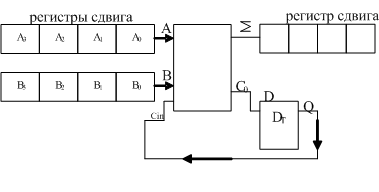

2. На рисунке изображена структурная схема:

-

последовательного сумматора

-

параллельного вычитателя

-

параллельного сумматора

-

последовательного вычитателя

-

сумматора-вычитателя

3. Для уменьшения стоимости разработок по конструирования цифровых электронных схем используют логику на элементах:

-

И-НЕ

-

И

-

ИЛИ

-

НЕ