2.1. Краткая теория о среде Active-hdl

Active-HDL— среда разработки, моделирования и верификации проектов дляпрограммируемых логических интегральных схем, разработанная фирмойAldec.

Программа позволяет описывать устройства с помощью языков программирования аппаратуры, а также с помощью структурных схем. Изначально программа поддерживала только языкVHDL, но со временем добавилась поддержка языковVerilogиSystemC. С помощью программы можно графически проектироватьконечные автоматы, а также конвертировать HDL описание в графические структурные схемы и обратно.

Компоненты Active-VHDL

Все компоненты Active-VHDL объединены в единообразную графическую среду, являющуюся основным каркасом. Каркас обеспечивает рабочую область окна и связывающую среду для всех элементов системы. Кроме ядра моделирования, каждый Active-VHDL инструмент выполнен в отдельном окне. В таблице представлено краткое описание компонентов Active-VHDL.

Таблица 1- Компоненты Active-VHDL

|

Компонент |

Описание |

|

Console |

Окно консоли – это интерактивное окно, предназначенное для ввода - вывода текста. Оно обеспечивает ввод команд Active-VHDL и вывод сообщений сгенерированных Active-VHDL инструментальными средствами. |

|

Design Browser |

Окно просмотра проекта показывает текущее содержание проекта, включая:

|

|

HDL Editor |

HDL редактор - текстовый редактор, разработанный для создания исходных файлов VHDL. Он показывает определенные категории синтаксиса в различных цветах. Редактор глубоко интегрирован с моделирующим устройством, что позволяет просто отлаживать исходный текст. |

|

Language Assistant |

Языковый помощник является вспомогательным инструментом который обеспечивает ряд типичных VHDL шаблонов и их логическое преобразование в функциональные блоки. Он объединен с HDL редактором так, чтобы можно было автоматически вставить желаемый шаблон в отредактированный исходный файл. |

|

State Machine Editor |

Редактор автоматов с конечными состояниями – графический инструмент, разработанный для редактирования диаграмм конечного автомата. Редактор осуществляет автоматический перевод графических примитивов в коды VHDL. |

|

Waveform Viewer |

Просмотрщик временных диаграмм показывает результаты моделирования, под действием тестовых сигналов. Это позволяет графически редактировать форму сигнала, для создания нужных испытательных векторов. |

|

List |

Окно списка показывает результаты моделирования, выполненные в сведенном в таблицы текстовом формате. |

|

Watch |

Окно средств наблюдения показывает текущие значения избранных сигналов и переменных в течение моделирования. |

|

Processes |

Окно процессов показывает текущее состояние одновременных процессов в разработанном проекте в течение моделирования. |

|

Library Manager |

Библиотечный менеджер разработан, чтобы управлять VHDL библиотеками и их содержанием. |

|

Design Explorer |

Проводник проекта облегчает управление Active-VHDL проектами. Он позволяет не запоминать физическую локализацию файлов проекта. |

|

Script Editor |

Редактор сценария - текстовый редактор с вмонтированным отладчиком. Он разработан, чтобы редактировать VBA Basic сценарии и выполнять команды Active-VHDL. |

Структура файлов

При реализации проекта ряд файлов создается в каталоге проектов. Это файлы конфигурации проекта, исходные файлы, файлы формы сигнала, Active-VHDL проекты. Расширения файлов представлены в таблице.

Таблица 2- Расширения файлов в проекте

|

*.VHD |

Источник VHDL код |

|

*.VHQ |

Источник VHDL код, сгенерированный из корневого файла |

|

*.ASF |

Исходный файл диаграммы состояний |

|

*.DO |

Файл сценария |

|

*.BAS |

Исходный командный файл |

|

*.ADF |

Файл описания проекта |

|

*.WSP |

Файл рабочей области окна |

|

*.WFV |

Файл формы сигнала |

|

*.LOG |

Файл отчета |

|

*.ERF |

Ошибки и сообщения компилятора |

|

*.EPR |

Список исходных файлов для компиляции |

|

*.SDF |

Стандартный файл задержки |

|

*.INI |

Библиотечный индексный файл |

|

*.MFG |

Библиотечный главный файл |

|

*.DAT |

Файл данных |

|

*.OID |

Вспомогательный файл Мастера HDL |

|

*.TXT |

Текстовый файл |

Структура проекта

Каждый проект записан в отдельном каталоге, названном каталогом проектов. И каталог проектов, и проект имеет то же самое название. Каждый каталог проектов содержит подкаталоги SRC И GENERIC а также файлы описания проектов, которые имеют то же самое имя, как и название проекта, только с расширением .ADF.

Подкаталог SRC содержит исходные файлы VHDL или файлы диаграмм автоматов с конечными состояниями с расширением VHD или .ASF.

Подкаталог GENERIC содержит файл рабочей области окна с .WSP расширением и рабочей библиотекой проектов с .VLB расширением. Оба имеют то же самое название, как и имя проекта. Подкаталог GENERIC также содержит ряд рабочих файлов, которые используются в процессе синтеза и моделирования.

Конфигурация проекта и его состояние описаны в следующих файлах:

*.ADF – файл описания проекта, содержащий информацию относительно структуры проекта: исходные файлы и библиотеки, которые формируют проект.

*.WSP – файл рабочей области окна, содержащий данные относительно текущего состояния проекта. Он всегда восстанавливает все параметры после закрытия проекта и повторного его открытия. Текущий статус содержит информацию о том, какие файлы были открыты, и в каком месте текста расположен курсор, какие закладки были выбраны, какие окна раскрыты и т.д.

Порядок выполнения работы

На основании данных, полученных в первой части лабораторной работы, необходимо синтезировать проект на языке VHDL, работающий по заданному алгоритму (например, реализующий функцию Not_M,как в ПРИМЕРЕ п. 1.2.).

В программе Active-HDL создаем новое рабочее пространство (рис. 2.1).

Рисунок 2.1 – Новое рабочее пространство в Active-HDL

В поле Type the workspace nameвводим имя рабочего пространства и нажимаемОК (рис. 2.2).

РисуРисунок

2.2 – Имя рабочего пространства в

Active-HDL

РисуРисунок

2.2 – Имя рабочего пространства в

Active-HDL

В окне New Design Wizard выбираем Create an empty design и нажимаем Next (рис. 2.3).

Рисунок 2.3 – Создание пустого проекта в Active-HDL

В выпадающем списке Default HDL Language выбираем язык VHDL и нажимаем Next (рис. 2.4).

Рисунок 2.4 – Выбор языка

Откроется окно New Design Wizard (Мастер нового проекта) - инструмент, который помогает в создании новых проектов и добавлении новых файлов в процессе проектирования. В поле Type the design name необходимо ввести название микросхемы (не должно начинаться с цифры) и нажать Next (рис. 2.4).

Рисунок 2.5 – Название микросхемы в Active-HDL

В появившемся окне нажимаем Finish.

На панели design flow выбираем HDE (или на панели Design Browser выбираем Add New File, и на вкладке Wizards выбираем VHDL Source Code) (рис. 2.6).

Рисунок 2.6 – Расширенный маршрут проектирования

Выбираем шаблон языка VHDL и нажимаем ОК (рис. 2.7).

Рисунок 2.7 – Выбор языка

В окне New Source File Wizard оставляем галочку на Add the generated file to the design и нажимаем Next (рис. 2.8).

Рисунок 2.8 – Добавление генерируемого файла к проекту

Далее необходимо указать название создаваемого файла и нажать Next.

В появившемся окне New Source File Wizard – Ports необходимо указать входы и выходы микросхемы. Для этого нужно нажать на кнопку New, ввести имя порта в поле Name и указать в меню Port Direction тип порта (in-вход, out-выход, inout-двунаправленный порт).

В зависимости от количества одновременно входящих и выходящих портов, в разделе Array Indexes указывается их количество (отсчет начинается с 0).

Нажмаем кнопку Finish для создания скелетного файла (рис. 2.9).

Рисунок 2.9 – Ввод данных об интерфейсный портах проекта (обратите внимание, что a и b задаются в виде массивов, где слева указан старший разряд)

В результате создан файл-шаблон с расширением *.vhd.

На основании проектной части, нужно написать код работы микросхемы. Затем вставить его в сгенерированный код с расширением .vhd вместо -- enter your statements here (вводим формулу для Y=Not_M):

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity comp is

port(

a : in STD_LOGIC_VECTOR(3 downto 0);

b : in STD_LOGIC_VECTOR(3 downto 0);

Y : out STD_LOGIC

);

end comp;

architecture comp of comp is

begin

Y<=not(a(2) and a(3));

end comp;

Компилируем файл, нажав Compile All.

Для проверки правильности работы схемы необходимо создать испытательный стенд - Test Bench. Для этого в панели инструментов выбираем Tools/Generate Test Bench.

В появляющихся окнах выбираем Далее/Далее/Готово.

На панели Design Browser во вкладке Files открываем папку Test Bench, нажимаем правой кнопкой мыши на файле, с расширением .do и выбираем Execute.

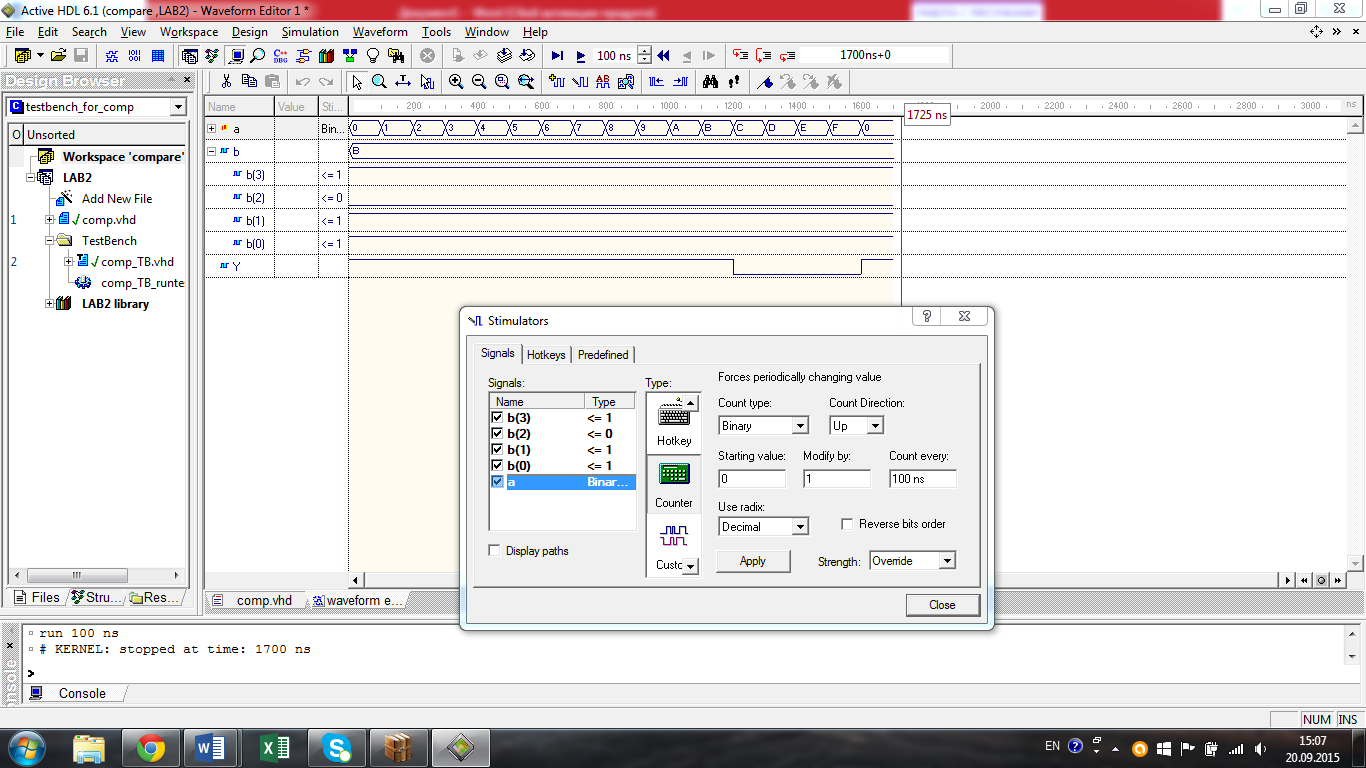

В появившемся файле временных диаграм нужно задать входные сигналы (рис.).

Значение а(3:0) задаем с помощью счетчика (рис.).

Значение b(3:0) задаем порозрядно, в соответствии с заданием (рис. )

Запускаем процесс симуляции Simulation/Run. Результаты моделирования представлены на рис.

Проанализировав временную диаграму убеждаемся, что заданная в задании схема компаратора работает корректно.