- •К лабораторным работам

- •1 Компьютерное моделирование с помощью ewb

- •1.1 Основные технические характеристики микросхем

- •1.2 Типы логики

- •1.3 «Стандартные» микросхемы

- •1.4 Семиотика «стандартных» микросхем

- •1.5 Микросхемы-аналоги

- •1.6 Техническая документация

- •1.7 Краткий англо-русский словарь терминов

- •2 Разработка испытательного стенда

- •3 Структурное моделирование с помощью сапр aldec active-hdl

- •4 Моделювання мікропрограмного автомата

- •4.1 Мікропрограмний автомат

- •4.2 Абстрактний автомат

- •4.3 Мова опису цифрових систем vhdl

- •4.4 Модель мікропрограмного автомату

- •4.5 Побудова графу переходів

- •X: in std_logic_vector (1 to 4); -- логічні умови

- •4.6 Моделювання роботи автомата

- •4.7 Отримання часових діаграм

- •4.8 Хід роботи

- •4.10 Контрольні запитання

- •5 Економічне кодування станів автомату

- •5.1 Структурний автомат

- •5.2 Тригери

- •5.3 Економічне кодування станів

- •5.4 Хід роботи

- •5.6 Контрольні запитання

- •6 Канонічний метод структурного синтезу

- •6.1 Кодована форма пст

- •6.2 Складання логічної схеми

- •6.3 Ціна логічної схеми за Квайном

- •6.4 Хід роботи

- •6.6 Контрольні запитання

- •7 Проектування мікропрограмного автомата

- •7.1 Реалізація автомату на плм

- •7.2 Хід роботи

- •7.4 Контрольні запитання

- •Література

4.7 Отримання часових діаграм

4.7.1

Виберіть команду File

→

New

→

waveform

або піктограму New

waveform

![]() .

З'явиться вікно редактора часових

діаграм.

.

З'явиться вікно редактора часових

діаграм.

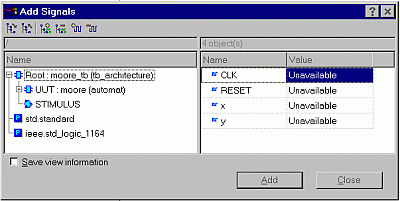

4.7.2 Додайте в редактор часових діаграм сигнали, що визначені у випробувальному стенді moore_tb. Клацніть правою кнопкою в лівій частині вікна редактора. В контекстному меню виберіть команду Add Signals. З'явиться вікно Add Signals (рис. 4.10).

Рисунок 4.10 – Вікно Add Signals

4.7.3 Вибираючи по черзі сигнали x, CLK, RESET, у і клацаючи на кнопці Add, додайте ці сигнали у вікно редактора часових діаграм.

4.7.4 В головному меню Active–HDL виберіть команду Simulation → Reset Simulation (скидання результатів попереднього сеансу моделювання).

4.7.5 Натисніть декілька разів клавішу <F5> до тих пір, поки у вікні Console не з'явиться повідомлення "Simulation has finished. There are no more test vectors to simulate" (Моделювання завершено. Тестова послідовність закінчилась).

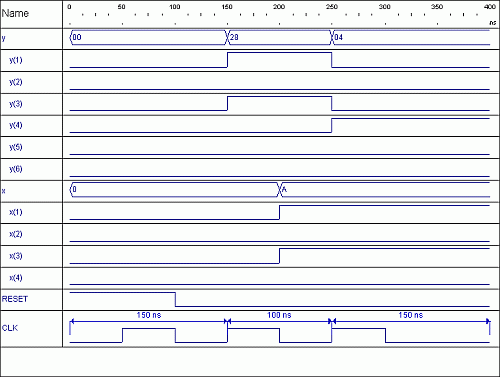

4.7.6 Вибравши команду головного меню Simulation → End Simulation, зупиніть процес моделювання. На рис.4.11 показаний результат функціонального моделювання правильно працюючого МПА Мура S1.

Рисунок 4.11 – Функціональне моделювання МПА Мура S1

4.7.7 Правильно працюючий VHDL-проект МПА S1 покажіть викладачу.

4.8 Хід роботи

Остання цифра номера студентського квитка – це варіант індивідуального завдання. Виконайте аналіз ГСА МПА Мура, що відповідає вашому варіанту (див.п.5).

Виконайте дії у відповідності до алгоритму А4.1. В якості зразка, шаблонів програм та покрокових інструкцій звертайтесь до пп.4.4-4.7. Під час редагування програм зверніть увагу на такі деталі.

Файл MOORE.VHD. Умовні оператори, що вкладені в оператор вибору, повинні відповідати логіці роботи автомату яка описується МФ ПСТ. Значення вектору вихідних сигналів Y повинно відповідати поточному стану МПА Мура.

Файл MOORE_TB.VHD. Значення вектору вхідних сигналів X треба визначати перед тим, як сигнал CLK змінює своє значення з '0' на '1'.

За результатами роботи оформіть звіт.

4.9 Зміст звіту

Титульний лист з номером студентського квитка, номером варіанту індивідуального завдання. Мета роботи.

Результат аналізу ГСА.

Відзначена ГСА.

Мнемонічна форма структурної таблиці МПА Мура.

Текст VHDL-програм.

Граф переходів автомата.

Таблиця найкоротших переходів автомата.

Часова діаграма результату моделювання.

Висновки.

4.10 Контрольні запитання

В чому полягає принцип мікропрограмного керування?

Що таке операційний пристрій, КА, ОА, МПА?

Визначення абстрактного автомата. Наведіть приклад формування послідовності вихідних слів кінцевого автомата (див. П4.1).

Що таке мікропрограма, мікрокоманда, мікрооперація, логічна умова?

Алгоритм А4.2 розмітки ГСА мікропрограмного автомата Мура.

Особливості обходу вершин ГСА під час складання МФ ПСТ. Що таке цикл, контур, безкінечний цикл, мертвий перехід?

Організація VHDL-проекту. Декларативна, виконавча частини VHDL-програми.

Самостійно побудувати граф переходів кінцевого автомата за заданою ГСА МПА.

Самостійно побудувати відзначену таблицю переходів за заданою ГСА МПА.

Інструменти САПР Active-HDL редагування графу переходів кінцевого автомата.