- •2. Построение реализуемой таблицы переходов.

- •3. Построение таблиц переходов-выходов и возбуждений элементов памяти.

- •4. Условия работы автомата.

- •1. Минимизация логических функций, полученных на этапе абстрактного синтеза, записанных в восьмеричной системе счисления. База y1y2abc.

- •2. Приведение полученных минимизированных функций, записанных в днф к виду, удобному для

Пермский Государственный Технический Университет

Кафедра ВТАУ

Курсовая работа

Вариант 15

«Решение комплексной задачи синтеза дискретного устройства с памятью»

Выполнил: студент гр. ЭВТ-99-1

Молганов А.С.

Проверил: профессор кафедры ВТАУ

Коган Т.И.

г. Пермь, 2001г.

ЗАДАНИЕ

Спроектировать цифровой автомат(кодовый замок), имеющий три входа(a, b, c) и два выхода (Z1, Z2).

Выход Z1 возбуждается при подаче входной последовательности сигналов 0-2-6-4-0, а Z2 – при нарушении заданной последовательности.

В качестве элементной базы использовать интегральные микросхемы. В качестве элементов памяти использовать RS-триггеры или JK-триггеры. После получения функциональной схемы автомата провести ее анализ на отсутствие состязаний типа “Риск в 1” в функции выхода Z2 ( или Z1 ). Входные сигналы образуют совокупность соседних чисел.

СОДЕРЖАНИЕ

ЗАДАНИЕ 2

СОДЕРЖАНИЕ 3

АБСТРАктный синтез 4

СТРУКТУРНЫЙ СИНТЕЗ 9

АНАЛИЗ АВТОМАТА НА ОТСУТСТВИЕ СОСТЯЗАНИЙ ТИПА "РИСК В 1" В ФУНКЦИИ ВЫХОДА Z2 11

АВТОМАТИЗИРОВАННЫЙ СИНТЕЗ АВТОМАТА НА ЭВМ 12

СРАВНЕНИЕ РУЧНОГО И МАШИННОГО РЕШЕНИЙ 14

ЭЛЕМЕНТЫ ФИЗИЧЕСКОГО СИНТЕЗА 15

СПИСОК ЛИТЕРАТУРЫ 16

АБСТРАктный синтез

1. Построение и минимизация первичной таблицы переходов-выходов.

Таблицу строим по словесной формулировке, приведенной в задании.

|

Таблица переходов |

||||||||||

|

N |

abc |

Z1 |

Z2 |

|||||||

|

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|||

|

1 |

1 |

6 |

2 |

-- |

7 |

-- |

-- |

-- |

0 |

0 |

|

2 |

8 |

-- |

2 |

9 |

-- |

-- |

3 |

-- |

0 |

0 |

|

3 |

-- |

-- |

10 |

-- |

4 |

-- |

3 |

11 |

0 |

0 |

|

4 |

5 |

-- |

-- |

-- |

4 |

12 |

13 |

-- |

0 |

0 |

|

5 |

5 |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

1 |

0 |

|

6 |

-- |

6 |

-- |

-- |

-- |

-- |

-- |

-- |

0 |

1 |

|

7 |

-- |

-- |

-- |

-- |

7 |

-- |

-- |

-- |

0 |

1 |

|

8 |

8 |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

0 |

1 |

|

9 |

-- |

-- |

-- |

9 |

-- |

-- |

-- |

-- |

0 |

1 |

|

10 |

-- |

-- |

10 |

-- |

-- |

-- |

-- |

-- |

0 |

1 |

|

11 |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

11 |

0 |

1 |

|

12 |

-- |

-- |

-- |

-- |

-- |

12 |

-- |

-- |

0 |

1 |

|

13 |

-- |

-- |

-- |

-- |

-- |

-- |

13 |

-- |

0 |

1 |

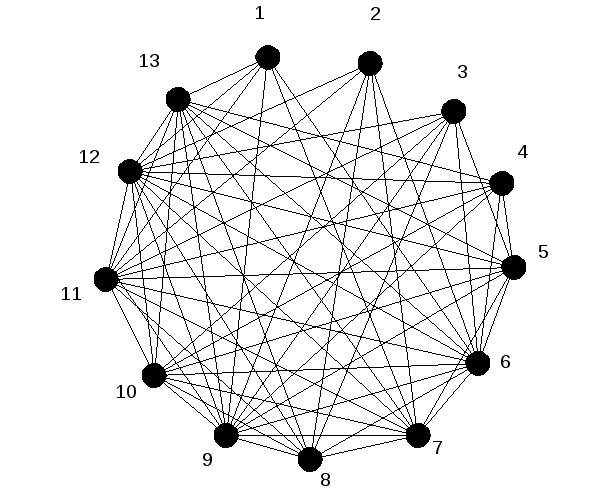

С целью уменьшения числа элементов памяти желательно иметь таблицы переходов с минимальным числом строк. Число строк первичной таблицы переходов-выходов может быть уменьшено за счет объединения некоторых из них. Воспользуемся наиболее простым методом минимизации первичной таблицы переходов-выходов - методом объединения совместимых внутренних состояний. Для наглядности представления всех возможных объединений строк таблицы построим диаграмму объединений. Наиболее оптимальным вариантом будет объединение строк: (4,5,12,13); (1,6,7); (2,8,9); (3,10,11). Строим минимизированную таблицу переходов.

|

Минимизированная таблица переходов |

||||||||

|

N |

abc |

|||||||

|

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

|

a |

1 |

6 |

2 |

-- |

7 |

-- |

-- |

-- |

|

b |

8 |

-- |

2 |

9 |

-- |

-- |

3 |

-- |

|

c |

-- |

-- |

10 |

-- |

4 |

-- |

3 |

11 |

|

d |

5 |

-- |

-- |

-- |

4 |

12 |

13 |

-- |

2. Построение реализуемой таблицы переходов.

Для каждой строки минимизированной таблицы переходов по каждому столбцу (с неустойчивым тактом) выписываем все переходы:

a b010

b c110

c d100

Все имеющиеся переходы обязательные. На основании полученных результатов строим диаграмму переходов.

![]()

Так как переходы от строки к строке для исключения состязаний должны осуществляться при изменении состояния только элемента памяти, то комбинации состояний элементов памяти тех строк, между которыми есть переходы, должны быть соседними. Для выбора соседних комбинаций состояний элементов памяти, т.е. для кодирования строк таблицы переходов, воспользуемся картой Карно. Возьмем карту Карно на 2 элемента.

|

Y2 Y1 |

0 |

1 |

|

0 |

a |

B |

|

1 |

d |

C |

|

Реализуемая таблица переходов |

||||||||

|

Y1Y2 |

abc |

|||||||

|

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

|

00 |

1 |

6 |

2 |

-- |

7 |

-- |

-- |

-- |

|

01 |

8 |

-- |

2 |

9 |

-- |

-- |

3 |

-- |

|

11 |

-- |

-- |

10 |

-- |

4 |

-- |

3 |

11 |

|

10 |

5 |

-- |

-- |

-- |

4 |

12 |

13 |

-- |

3. Построение таблиц переходов-выходов и возбуждений элементов памяти.

В таблице переходов-выходов вместо номеров тактов в клетках проставляются состояния элементов памяти в следующий момент времени Y(t+1) (в числителе) и значение выходных сигналов Z(t) (в знаменателе).

|

Таблица переходов-выходов |

|||||||||

|

Y1Y2 |

abc |

|

|||||||

|

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

|

|

00 |

00/00 00 |

00/01 01 |

01/00 02 |

-- 03 |

00/01 04 |

-- 05 |

-- 06 |

-- 07 |

|

|

01 |

01/01 10 |

-- 11 |

01/00 12 |

01/01 13 |

-- 14 |

-- 15 |

11/00 16 |

-- 17 |

|

|

11 |

-- 30 |

-- 32 |

11/01 32 |

-- 33 |

10/00 34 |

-- 35 |

11/00 36 |

11/01 37 |

Y1Y2(t+1)Z1Z2(t) |

|

10 |

10/10 20 |

-- 22 |

-- 22 |

-- 23 |

10/00 24 |

10/01 25 |

10/01 26 |

-- 27 |

|

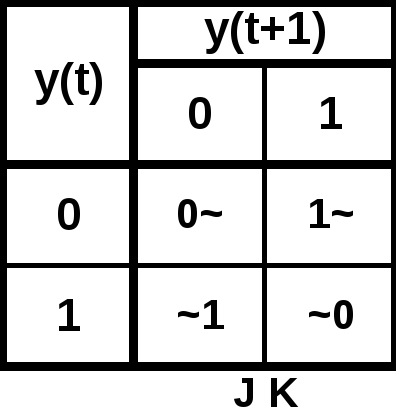

В качестве элементов памяти возьмем JK-триггер, т.к. он требует больше всего условных сигналов на входах и на этапе структурного синтеза будет легче минимизировать. Такой триггер есть в серии К155.

Т

аблица

переходов JK-триггера

Таблица

входов JK-триггера

аблица

переходов JK-триггера

Таблица

входов JK-триггера

Построим таблицу возбуждений ДУ, описываемого таблицей переходов-выходов, для JK-триггеров.

|

Таблица возбуждений элементов памяти |

|||||||||

|

Y1Y2 |

abc |

|

|||||||

|

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

|

|

00 |

0~,0~ 00 |

0~,0~ 01 |

0~,1~ 02 |

-- 03 |

0~,0~ 04 |

-- 05 |

-- 06 |

-- 07 |

|

|

01 |

0~,~0 10 |

-- 11 |

0~,~0 12 |

0~,~0 13 |

-- 14 |

-- 15 |

1~,~0 16 |

-- 17 |

|

|

11 |

-- 30 |

-- 32 |

~0,~0 32 |

-- 33 |

~0,~1 34 |

-- 35 |

~0,~0 36 |

~0,~0 37 |

J1K1,J2K2 |

|

10 |

~0,0~ 20 |

-- 22 |

-- 22 |

-- 23 |

~0,0~ 24 |

~0,0~ 25 |

~0,0~ 26 |

-- 27 |

|