Схемотехника / Схемотехника(1) / LAB3

.pdfГосударственный комитет РФ по высшему образованию

Пермский государственный технический университет

Кафедра автоматики и телемеханики

ИЗУЧЕНИЕ ЦИФРОВОЙ СХЕМОТЕХНИКИ С ИСПОЛЬЗОВАНИЕМ САПР MAX+PLUSII

Проектирование комбинационных схем, программирование ПЛИС и анализ размещения схемы на кристалле

МЕТОДИЧЕСКИЕ УКАЗАНИЯ К ЛАБОРАТОРНОЙ РАБОТЕ №3

Пермь, 2003 г.

Лабораторная работа №3: «Проектирование комбинационных схем, программирование ПЛИС и анализ размещения схемы на кристалле»

Цель работы: освоение проектирования комбинационных схем с привлечением платы лабораторного стенда, анализ размещения схемы устройства на кристалле с использованием редактора конфигурации БИС системы MAX+plusII.

ВВЕДЕНИЕ

Комбинационными называются цифровые устройства, логическое состояние которых зависит только от комбинации логических сигналов, поступающих на их входы в настоящий момент времени. К этому классу устройств относятся такие широко распространенные функциональные узлы цифровых систем, как преобразователи кодов, шифраторы и дешифраторы, мультиплексоры и демультиплексоры, компараторы, сумматоры, арифметико-логические устройства (АЛУ), умножители и ряд других.

Функциональное описание комбинационного устройства задается в виде таблицы истинности, алгебраического выражения или описания на специализированном языке высокого уров-

ня (VHDL, AHDL, Verilog HDL и другие).

В настоящее время для реализации комбинационных устройств используются два возможных способа.

1.Сборка устройства из набора отдельных логических элементов (И-НЕ, ИЛИ-НЕ и других). Этот способ применяется при разработке относительно несложных устройств, реализуемых на серийно выпускаемых микросхемах малой степени интеграции, или при проектировании комбинационных блоков в составе сложнофункциональных устройств, реализуемых в виде заказных или полузаказных БИС, которые разрабатываются с использованием библиотек логических элементов.

2.Создание устройства на базе программируемых логических интегральных схем (ПЛИС), в которых заданная логическая функция реализуется путем соответствующего программирования и соединения универсальных логических элементов и блоков, составляющих внутреннюю структуру ПЛИС.

Традиционные методы проектирования комбинационных устройств, ориентированные на первый способ их реализации, описаны в ряде учебных пособий. В данной лабораторной работе описывается методика проектирования цифровых устройств на базе ПЛИС, выпускаемых компанией Altera, с помощью системы MAX+plusII.

Система MAX+plusII предоставляет возможность анализа размещения схемы устройства на кристалле с использованием редактора конфигурации БИС. Редактор конфигурации формирует две разновидности изображения ПЛИС - Device View и LAB View. Первое изображение представляет корпус микросхемы с указанием всех выводов, их номеров и функций. Второе представляет внутреннюю структуру ПЛИС в виде совокупности блоков ячеек (LABs - logic array blocks), отдельные ячейки внутри блоков, ячейки ввода-вывода. Этот тип изображения также включает информацию о выводах, поэтому можно проследить связи между ними и внутренними ячейками микросхемы.

2

ОПИСАНИЕ ЗАДАЧИ

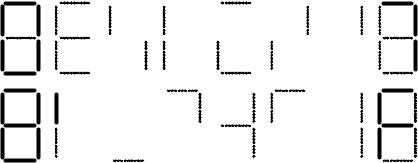

В данной работе рассмотрим дешифратор для семисегментного индикатора, который, в зависимости от комбинации сигналов на 4 входных линиях, формирует код выборки сегментов на семи выходных линиях. Активным значением сигнала на выходной линии (при котором зажигается сегмент) является уровень "1". Обозначение дешифратора с указанием входных и выходных линий, распределение имен сегментов и индицируемые знаки приведены на Рис. 1.

DI3 |

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

a |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

DI2 |

|

|

|

|

|

|

|

|

|

|

|

c |

|

|

|

|

f |

|

g |

b |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

DC |

|

|

|

|

|

|

|

|

|

d |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

DI1 |

|

|

|

|

|

|

|

|

|

|

|

e |

|

|

|

|

e |

|

|

|

c |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d |

|

||||

DI0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

g |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1. Дешифратор 7-сегментного индикатора, распределение имен сегментов, индицируемые знаки

ПОСЛЕДОВАТЕЛЬНОСТЬ РЕШЕНИЯ ЗАДАЧИ

Создание и трансляция текстового файла.

Созданный проект дешифратора можно проверить с привлечением платы лабораторного стенда. На этой плате (см. описание стенда) имеется 8-разрядный переключатель, который можно использовать для задания входных сигналов, и 3-хразрядный 7-сегментный индикатор, один из разрядов которого может быть использован для отображения результатов. Эти устройства на плате подключены к определенным выводам ПЛИС EPF8282ALC84-4, поэтому в проекте необходимо указать тип ПЛИС и соответствие номеров ее выводов входным и выходным линиям дешифратора.

Описать такой дешифратор на языке AHDL можно в виде таблицы истинности следующим образом:

TITLE "7-Digit Indicator Decoder";

SUBDESIGN decode7

(

di[3..0] : INPUT;

a, b, c, d, e, f, g : OUTPUT;

)

BEGIN

3

TABLE |

|

|

!di[] |

=> |

(a, b, c, d, e, f, g); |

H"0" |

=> |

B"1111110"; |

H"1" |

=> |

B"0110000"; |

H"2" |

=> |

B"1101101"; |

H"3" |

=> |

B"1111001"; |

H"4" |

=> |

B"0110011"; |

H"5" |

=> |

B"1011011"; |

H"6" |

=> |

B"1011111"; |

H"7" |

=> |

B"1110000"; |

H"8" |

=> |

B"1111111"; |

H"9" |

=> |

B"1111011"; |

H"A" |

=> |

B"1110111"; |

H"B" |

=> |

B"0011111"; |

H"C" |

=> |

B"1001110"; |

H"D" |

=> |

B"0111101"; |

H"E" |

=> |

B"1001111"; |

H"F" |

=> |

B"1000111"; |

END TABLE; |

|

|

END;

Справа в таблице указаны шестнадцатиричные значения кода на входных линиях, а слева - двоичные значения выходного кода на линиях, соответствующих определенному сегменту индикатора. Инверсия входных сигналов в таблице обусловлена тем, что в положении переключателя «ON» (замкнутом) на соответствующий вход ПЛИС поступает сигнал логического «0» (см. описание стенда).

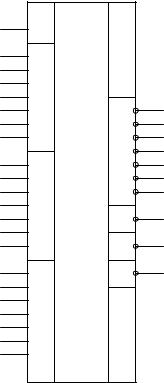

Для стенда с динамическим 3-хразрядным 7-сегментным индикатором управление индикатором осуществляется через специальный модуль d_ind7, функциональное назначение выводов которого показано на Рис. 2.

d_ind7

clk |

|

a1 |

|

b1 |

|

c1 |

|

d1 |

|

e1 |

a |

f1 |

b |

g1 |

c |

|

d |

a2 |

e |

b2 |

f |

c2 |

g |

d2 |

|

e2 |

en1 |

f2 |

|

g2 |

en2 |

a3 |

en3 |

b3 |

|

c3 |

|

d3

e3

f3

g3

Рис. 2. Графическое обозначение блока преобразования сигналов управления статического индикатора в сигналы управления динамическим индикатором

4

На вход clk (Рис. 2) должен поступать сигнал с выхода генератора опорной тактовой частоты 4 МГц. Входы a1-g1, a2-g2, a3-g3 устанавливают состояние сегментов разрядов 1-3 индикатора соответственно, причем, при подаче на вход логической «1» сегмент индикатора будет светиться. Выходы модуля (a-g, en1-en3) необходимо связать с выводами ПЛИС, подключенными к соответствующим выводам динамического индикатора.

Дешифратор, описанный на языке AHDL с выводом на динамический индикатор, будет реализован в следующем виде (для стенда со статическим 3-хразрядным 7-сегментным индикатором текст модуля дешифратора останется прежним):

TITLE "7-Digit Indicator Decoder";

INCLUDE "d_ind7.inc";

SUBDESIGN decode7

(

di[3..0] : INPUT;

a, b, c, d, e, f, g : OUTPUT; clk : INPUT;

en[1..3] : OUTPUT;

)

VARIABLE

ind : d_ind7;

BEGIN

ind.clk = clk;

ind.(a2, b2, c2, d2, e2, f2, g2) = B"0000000"; ind.(a3, b3, c3, d3, e3, f3, g3) = B"0000000"; en[1..3] = ind.(en1, en2, en3);

(a, b, c, d, e, f, g) = ind.(a, b, c, d, e, f, g);

TABLE |

|

|

!di[] |

=> |

ind.(a1, b1, c1, d1, e1, f1, g1); |

H"0" |

=> |

B"1111110"; |

H"1" |

=> |

B"0110000"; |

H"2" |

=> |

B"1101101"; |

H"3" |

=> |

B"1111001"; |

H"4" |

=> |

B"0110011"; |

H"5" |

=> |

B"1011011"; |

H"6" |

=> |

B"1011111"; |

H"7" |

=> |

B"1110000"; |

H"8" |

=> |

B"1111111"; |

H"9" |

=> |

B"1111011"; |

H"A" |

=> |

B"1110111"; |

H"B" |

=> |

B"0011111"; |

H"C" |

=> |

B"1001110"; |

H"D" |

=> |

B"0111101"; |

H"E" |

=> |

B"1001111"; |

H"F" |

=> |

B"1000111"; |

END TABLE; |

|

|

END;

Вызовем текстовый редактор (Max+plusII | Text Editor), введем текст описания декодера, соответствующее имеющемуся лабораторному стенду, и сохраним файл (File | Save As) с описанием декодера под именем decode7.tdf (имя файла decode7 должно совпадать с именем модуля). Свяжем проект с текущим файлом, выбрав меню File | Project Set Project to Current File.

5

Определим тип ПЛИС для проекта командой меню Assign | Device. В открывшемся диалоговом окне в строке Device Family нужно указать семейство FLEX8000, а в строке Devices определить тип микросхемы - EPF8282ALC84-4 (необходимо отключить опцию Show Only Fastest Speed Grades в окне Device для отображения полного списка устройств).

Поскольку целью работы является создание дешифратора для индикатора, правильность функционирования спроектированного устройства можно проверить, наблюдая отображаемые знаки на левом разряде 7-сегментного 3-хразрядного индикатора платы стенда. Задавать входной код можно с использованием тумблеров 1-4 (Sw1-Sw4 на схеме) 8-разрядного микропереключателя. Нужно учитывать, что младший разряд управляется тумблером 1, т.е. визуально порядок тумблеров является обратным относительно общепринятого, когда младшим разрядом является крайний правый.

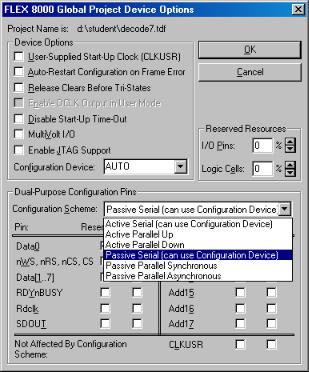

Для указания соответствия выводов входным и выходным линиям дешифратора, предназначена команда меню Assign | Pin Location Chip, при выборе которой открывается диалоговое окно, приведенное на Рис. 3. После ввода имени линии в строке Node Name, в строке Pin следует указать номер соответсвующего этой линии вывода ПЛИС (см. описание стенда) и щелкнуть по кнопке Add. В списке Existing Pin/Location/Chip Assignment появляется строка соответствия вывода и линии. При назначении выводов групповой линии (di[3..0]) отдельный разряд указывается в квадратных скобках, следующих за названием группы (например, di[0]). Вход clk (в случае динамического индикатора) необходимо связать с выводом ПЛИС, подключенным к генератору тактовой частоты 4 МГц, а выходная шина en[1..3] в этом случае должна быть связана с выводами ПЛИС, подключенными к соответствующим входным сигналам индикатора en1-en3 (см. описание стенда). После назначения всех линий, вводом ОК, нужно вернуться в редактор.

Рис. 3. Назначение выводам ПЛИС входных и выходных линий проекта

Трансляция исходного текстового файла осуществляется с помощью компилятора, вызвать который можно командой меню Max+plusII | Compiler и, осмотрев открывшееся окно компилятора, убедиться, что к процессу трансляции на последней стадии будет подключен ассемблер. Если его в списке нет, следует выбрать команду меню Processing (окно компилятора должно быть активным) и отключить опцию Functional SNF Extractor. После этого можно щелкнуть указателем мыши по кнопке Start диалогового окна компилятора.

6

Отладка с привлечением платы лабораторного стенда.

Для проверки функционирования разработанного дешифратора необходимо выполнить следующие действия (пункты 1-5 выполняются под наблюдением преподавателя).

1.Подключить к разъему платы кабель устройства ByteBtaster, который в свою очередь должен быть подключен к разъему LPT компьютера.

2.Подключить к разъему платы кабель блока питания +12В.

3.Включить источник питания - на плате должен загореться индикатор питания.

4.Выбрать в системе MAX+plusII команду меню Assign | Global Project Device Options и

воткрывшемся диалоговом окне в строке Configuration Scheme указать Passive Serial (выбрать из меню в соответствии с Рис. 4), после чего установить опции Reserve и Tri-State для вывода Data0, и удалить эти опции для всех остальных выводов.

5.Вызвать приложение Programmer, при активном окне приложения щелкнуть по меню

Options | Hardware Setup и установить для Hardware_Type значение ByteBlaster, ввести ОК.

Инициировать процесс загрузки ПЛИС, щелкнув по кнопке Configure приложения Programmer.

5.Переключая тумблеры 1-4 8-разрядного переключателя, наблюдать отображаемые на левом 7-сегментном индикаторе шестнадцатиричные цифры. Проверить правильность работы дешифратора.

Рис. 4. Определение способа загрузки ПЛИС

Анализ размещения схемы устройства на кристалле с использованием редактора конфигурации БИС.

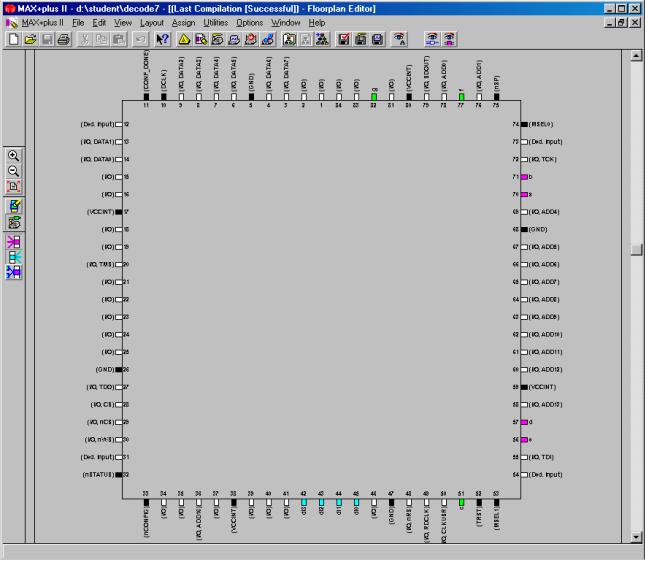

Вызвать редактор конфигурации можно командой меню Max+plusII | Floorplan Editor или щелчком по кнопке в панели инструментов. Откроется одно из двух вариантов изображения конфигурации ПЛИС (в данном случае типа EPF8282ALC84-4). Пусть это изображение типа Device View, приведенное на Рис. 5. На нем видно расположение всех выводов ПЛИС и назначенные им имена входных и выходных линий проекта. Переключить тип изображения конфигурации можно командой меню Layout| Lab View или Layout| Device View, или двойным щелчком мыши по изображению ПЛИС.

7

Рис. 5. Изображение конфигурации ПЛИС типа Device View

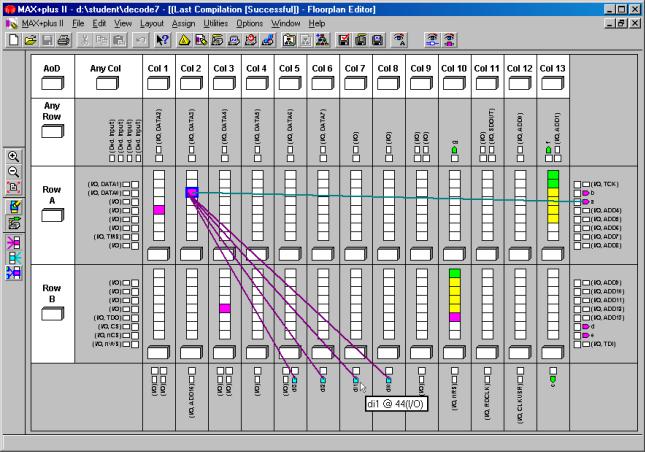

Изображение типа LAB View, приведено на Рис. 6.

Из рисунка видно, что при наведении указателя на вывод, рядом с указателем в рамке отображается имя линии проекта и номер вывода микросхемы. Редактор конфигурации позволяет получить информацию о связях отмеченных логических ячеек и выводов. Это делается следующим образом:

1.Выберем опцию Show Node Fan-In ("входные цепи") и/или опцию Show Node Fan-Out ("выходные цепи") в меню Option.

2.Установим режим LAB View и отметим одну или более логических ячеек или выво-

дов.

Редактор отобразит входные и выходные цепи отмеченных элементов. На Рис. 6 отображены связи третьей логической ячейки ряда А, столбца 2. Редактор конфигурации позволяет просматривать и изменять текущие назначения, которые хранятся в файле project's Assigment&Configuration File (.acf). После трансляции проекта можно вручную редактировать назначения, сделанные компилятором и хранящиеся в файле project's Fit File (.fit). Для этого существует опция Back-Annotate Project в меню Assign, которая осуществляет копирование назначений из файла .fit в файл .acf.

8

Рис. 6. Изображение конфигурации ПЛИС типа LAB View

Процесс корректировки назначений проекта с использованием редактора конфигурации следующий:

1.Выберем команду меню Assign | Back-Annotate Project.

2.В открывшемся диалоговом окне включим опцию Chips, Logic Cells, Pins&Devices раздела Back-Annotate to ACF. После ввода OK будет проведено копирование назначений из файла .fit в файл .acf.

3.Введем команду меню Layout | Current Assignments Floorplan. Редактор конфигурации отобразит текущие назначения проекта.

4.Выберем опцию Show Node Fan-In ("входные цепи") и/или опцию Show Node Fan-Out ("выходные цепи") меню Option.

5.Введем команду поиска, выбрав пункт меню Utilities | Find Text, в диалоговом окне выключим опцию Аll и включим опцию Pin&Node Names. Укажем слово для поиска di0 и завершим ОК. В окне редактора конфигурации будет отмечен назначенный этому имени вывод и указаны его связи.

6.Введем команду меню Option | Show Moved Nodes in Gray, которая отмечает серым цветом новые назначения.

7.Переведем редактор в режим просмотра текущих назначений, для чего нужно нажать

на кнопку  в левой вертикальной панели инструментов.

в левой вертикальной панели инструментов.

8. Наведем указатель мыши на отмеченный вывод линии di0 и при нажатой левой кнопке мыши «перетащим» назначение с вывода 45 на вывод 37. Аналогично переназначим линию di1 с

9

вывода 44 на вывод 39, линию di2 с вывода 43 на вывод 40, линию di3 с вывода 42 на вывод 41. Новые назначения будут отмечены серым цветом.

9.Запустим перекомпиляцию проекта (Max+plusII | Compiler), убедившись, что отклю-

чена опция Processing | Functional SNF Extractor, и включена опция Processing | Timing SNF Extractor.

10.После успешной перекомпиляции вернемся в окно редактора конфигурации и, включив опцию Layout | Last Compilation Floorplan, убедимся, что новые назначения выполнены. Эти назначения определяют в качестве формирователей входных векторов на плате тумблеры 5-8 (SW5-SW8) 8-разрядного переключателя, причем младший разряд (di0) задается переключателем 8, т.е. целью переназначения было установить общепринятый порядок, когда младший значащий бит находится справа.

11.Введем команду меню Assign | Back-Annotate Project.

12.Загрузим файл проекта в ПЛИС на плате, вызвав окно программатора командой меню Max+plusII | Programmer и, переключая тумблеры 5-8 8-разрядного переключателя, проверим правильность работы дешифратора, наблюдая отображаемые на левом 7-сегментном индикаторе шестнадцатиричные цифры.

10