Схемотехника(Тюрин) / инфа по MS и DS

.docx27. Сумма по модулю 2 - функция равна 1,когда нечетное число переменных равно 1, функция равна 0, когда четное число переменных равно 1.

29. Минимизация с помощью диаграмм Карно

Правило построения диаграммы Карно

Для n переменных заполняется прямоугольная таблица, содержащая 2n клеток так, чтобы в соседних клетках конъюнкции отличались не более, чем одним сомножителем.

Если минимизируемая функция при данном наборе переменных равна 1, то в соответствующую клетку ставится 1 (нули можно не ставить). В прямоугольной таблице единицы обводятся контурами и записывается функция в виде суммы произведений,описывающих контуры. Число клеток внутри контура 2к (1,2,4,8...).

Следует покрыть все единицы возможно меньшим числом возможно более крупных блоков. Каждому блоку сопоставляется конъюнкция, записываемая следующим образом:

1) Если блок целиком лежит в единичной области переменной хi, то она включается в конъюнкцию без инверсии, если в нулевой области, то с инверсией.

2) Если блок делится точно пополам между нулевой и единичной областями хi, то хi в конъюнкцию не включается (склеивание по хi).

17. Дешифратор – логический узел, осуществляющий коммутацию одного из N выходов по заданным n адресным входам. При подаче на входы а0а1а2 какого-либо кода на выходе с номером определенным адресным кодом появляется 1, а на остальных выходах - 0. Дешифратор используется для выбора (коммутации) одного из блоков цифрового устройства.

Логический узел осуществляющий коммутацию с N входов на 1 выход называется мультиплексор. Номер входа bi определяется кодом, поданным на адресные входы аi

Сумматор – устройство, осуществляющее операцию сложения двоичных кодов {глава 4.1} по правилам:

0+0 = 0, 0+1 = 1, 1+0 = 1, 1+1 = 0 и 1 - перенос.

Для сложения младших разрядов кода применяется полусумматор.

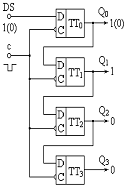

21 Регистр – функциональный узел объединяющий несколько однотипных триггеров. Сдвигающие регистры – выполняют функцию только последовательного приема кода. Сдвигающий регистр -

это регистр, содержимое которого при подаче управляющего сигнала может сдвигаться в сторону старших или младших разрядов.

На вход DS поступает последовательный код.

Рис.7-1 Регистр с однофазной синхронизацией

В регистр (рис.7-1) в момент поступления стробирующего импульса происходит запись входного бита DS в триггер ТТ0. В триггер ТТ1 переписывается информация, имевшаяся в ТТ0, в ТТ2 из ТТ1 и т.д.

При подаче следующего бита DS и сигнала С происходит тот же процесс, в результате все биты имевшиеся на выходах Q0-Q3 передвигаются на 1 разряд влево

18. В отличие от комбинационных схем (КС) значения выходных сигналов последовательностных схем (ПС) в данный момент времени зависят не только от значений входных сигналов в этот же момент времени, но и от их предыдущих значений. Из этого следует, что ПС реализует функциональную связь уже не между отдельными значениями входных и выходных сигналов, а между их последовательностями. Поэтому, в отличии от КС, работу ПС следует рассматривать во времени.

Триггеры – это логические устройства с памятью, которые способны длительно оставаться в одном из двух возможных устойчивых состояний и скачком чередовать их под действием внешних сигналов.

Синхронный RS-триггер

Синхронный RS-триггер

Счётчиком называется устройство, сигнал на выходе которого в определённом коде отображает число импульсов, поступающих на счётный вход.

Назначение регистров – хранение и преобразование многоразрядных двоичных чисел. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счётчиков, делителей частоты, узлов временной задержки. Регистры строят на синхронных D-триггерах или на RS(JK) - триггерах с динамическим или статическим управлением.

22.М ультиплексор – адресный коммутатор, который может выполнить коммутацию

на выход сигнала с того информационного входа, адрес которого задан сигналами

на адресных входах.

Синтез КЛС на основе мультиплексоров: Мультиплексор можно использовать

для преобразования параллельной информации в последовательную, если

последовательно задавать адреса разрядов кода числа. Мультиплексор на большое

число входов, как правило, приходится строить из мультиплексоров меньшей

размерности. «8-1» На адресные входы подаются входные переменные, а

информационные входы, соответствующие входящим в функцию конституентам единицы,

соединяются с шинами питания, остальные инф. входы соединяются с шинами земли.

На выходе мультиплексора формируется значение функции. «4-1» В

качестве управляющих сигналов используются переменные, которые подаются на

адресные входы мультиплексора. На инф. входы поступают переменные.