- •Лабораторная работа №1 «Исследование работы регистра сдвига» Краткие теоретические сведения. Цифровой логический уровень.

- •Постановка задачи Базовое задание

- •Задание повышенной сложности

- •Рекомендации к выполнению

- •Лабораторная работа №2 «Моделирование работы буфера данных»

- •Классификация полупроводниковых зу по способу доступа к данным и хранению.

- •Краткая характеристика памяти

- •Память fifo

- •Описание лабораторной работы

- •Постановка задачи Базовое задание

- •Рекомендации к выполнению

- •Лабораторная работа №3 «Моделирование кэш-памяти» Описание лабораторной работы

- •Постановка задачи

- •Рекомендации к выполнению

- •Блок микропрограммного управления

- •Блок-схема блока микропрограммного управления (см. Рис. 4.5.)

- •Блок управления с жесткой логикой

- •Лабораторная работа№4а «Моделирование блока управления с микропрограммным управлением» Описание лабораторной работы

- •Рекомендации к выполнению

- •Лабораторная работа №4б «Моделирование блока управления с жесткой логикой»

- •5.Индивидуальные домашние задания

- •5.1. Индивидуальное домашнее задание №1 «Комбинационные многовходовые схемы»

- •Варианты заданий

- •Рекомендации к выполнению

- •5.2.Индивидуальное домашнее задание №2 «Проектирование модуля памяти» Описание домашнего задания

- •Назначение выводов микросхем к155ру5 и к155ру7 Таблица 5.2.1 .

- •Варианты заданийТаблица 5.2.2

- •Методика проектирования модуля памяти

- •6.Курсовое проектирование Список тем курсовых проектов

- •6.1.Память эвм

- •6.1.1.Модуль памяти с блоком ключей защиты

- •6.1.2.Модуль памяти с буфером fifo для записи сбойных адресов, в которых были обнаружены одиночные ошибки блоком контроля с использованием кода Хемминга для их обнаружения в считываемых данных.

- •6.1.3.Модуль памяти с блоком контроля количества обращений к страницам памяти и заменой содержимого страницы с наименьшим количеством обращений (операций чтения) при операции записи в модуль.

- •6.1.4.Модуль памяти с блоком контроля последовательности обращений к адресам памяти в группе заранее указанных адресов.

- •6.2.Процессор

- •6.2.1.Устройство управления объектом, обходящим препятствия.

- •6.2.2.Устройство управления движением объекта на плоскости с контролем за движения его на табло, собранным на сдвиговых регистрах.

- •6.2.3.Анализатор формы сигнала.

- •6.2.4.Универсальный информационный конвейер.

- •6.3.Система ввода-вывода

- •6.3.1.Устройство сбора информации с датчиков и ее обработки.

- •6.3.2.Шифровальное устройство.

- •6.3.3.Электронный коммутатор на четыре направления.

- •Приложение 1. П1 .1. Перечень тем рефератов

- •П1.2. Перечень тем семинаров

- •П1.3. Перечень вопросов к зачету

- •П1.4. Перечень вопросов к экзамену Вводная часть

- •Запоминающие устройства эвм

- •Процессор

- •Система прерываний

- •Организация ввода-вывода

- •Организация мультипрограммного режима эвм

- •Многопроцессорные системы

- •Приложение 2.Справочные данные по микросхемам серии ттл к155 п2.1. Микросхема 2d триггера к155тм2

- •П2.2.Микросхема счетчик двоичный реверсивный к155е7

- •П2.3.Микросхема памяти к155ру2.

- •П2.4.Микросхема зу регистровое на 16 бит к155рп1

- •П2.5.Микросхема регистр сдвига 8- разрядный к155ир13

- •П2.6. Микросхема алу к155ип3

- •Рекомендуемая литература

- •Дополнительная литература

- •Содержание

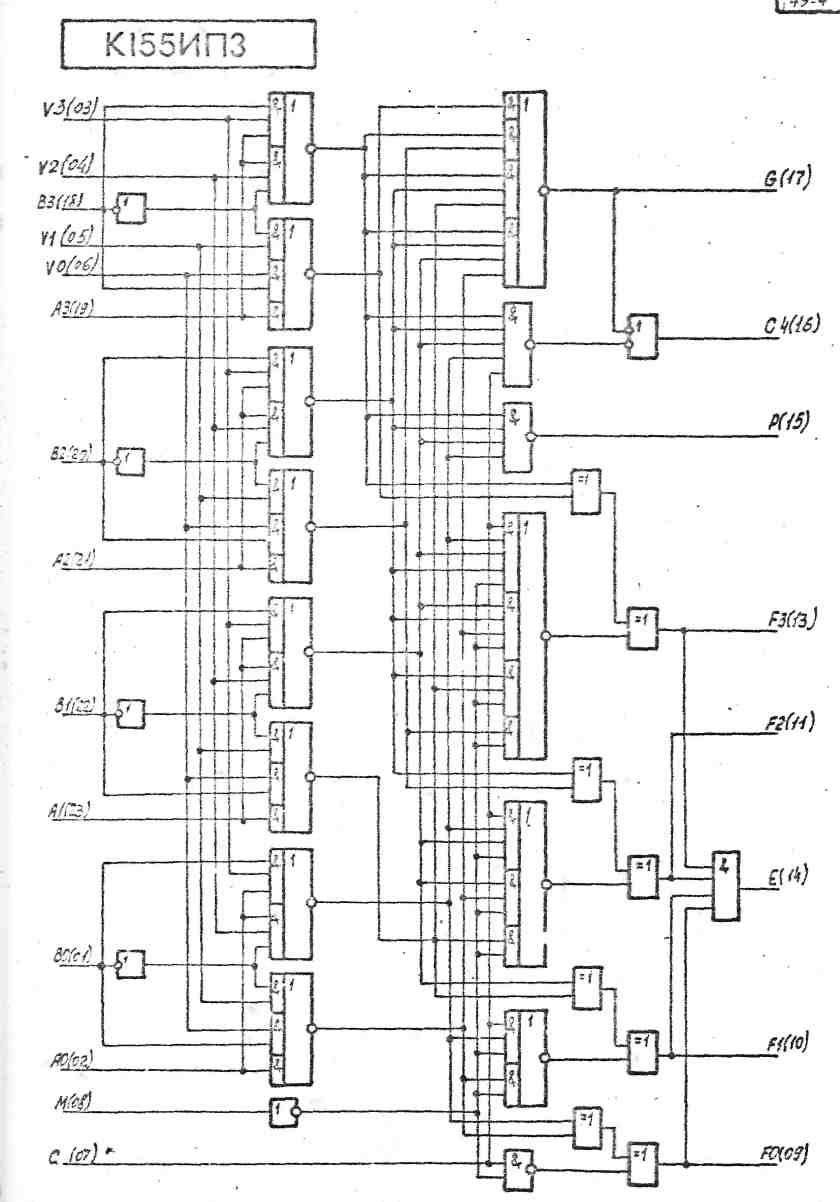

П2.6. Микросхема алу к155ип3

Универсальная микросхема КI55ИПЗ представляет собой 4-разрядное арифметико-логическое устройство (АЛУ), предназначенное для выполнения 16 арифметических операций с двумя 4-разрядными словами и формирования 16 логических операций. Функциональная схема АЛУ приведена на рис.П2.6.-1.

Схема имеет информационные входы А0 – А3, В0-В3, управляющие входы V0-V3 вход переноса с предыдущего разряда С, вход выбора режима М, выходы F1-F4, на которых фиксируется результат операций, выход сравнения Е, выходы образования переноса G и распространения переноса Р, выход переноса с четвертого разряда С4.

На информационные входы А0 – А3 и В0-В3 поступает 4-разрядные двоичные числа. В зависимости от кодовой комбинации на управляющих входах V0-V3 осуществляется выполнение одной из 16 реализуемых операций.

Схема может выполнять одни и те же операции как при активном высоком, так и активном низком уровне при различных кодовых комбинациях на управляющих входах.

Функции, выполняемые АЛУ при активном высоком уровне, приведены в табл.П2.6.-1. Наличию переноса с предыдущего разряда при выполнении арифметических операций при активном высоком уровне соответствует уровень логического "0" на входе С.

Функции, выполняемые АЛУ при активном низком уровне, приведены в табл.П2.6.-2. Наличию переноса с предыдущего разряда при выполнении арифметических операций при активном низком уровне соответствует уровень логической "I" на входе С.

ТаблицаП2.6.-1

|

Условное графическое обозначение |

V0 |

V1 |

V2 |

V3 |

Арифметическая операция при М=0, С=0 |

Логическая операция при М=I |

|

|

0 I 0 I 0 I 0 I 0 I 0 I 0 I 0 I |

0 0 I I 0 0 I I 0 0 I I 0 0 I I |

0 0 0 0 I I I I 0 0 0 0 I I I I |

0 0 0 0 0 0 0 0 I I I I I I I I |

|

|

ТаблицаП2.6.-2

|

Условное графическое обозначение |

V0 |

V1 |

V2 |

V3 |

Арифметическая операция при М=0, С=0 |

Логическая операция при М=I |

|

|

0 I 0 I 0 I 0 I 0 I 0 I 0 I 0 I |

0 0 I I 0 0 I I 0 0 I I 0 0 I I |

0 0 0 0 I I I I 0 0 0 0 I I I I |

0 0 0 0 0 0 0 0 I I I I I I I I

|

|

|

Состояние входа М обуславливает выполнение арифметических или логических операций. При выполнении арифметических операций на вход М должен быть подан уровень логического "0". С подачей на вход М уровня логической "I" запрещается выполнение переносов, и на выходах АЛУ появляются результаты логических операций.

Сигнал переноса с 4-го разряда С4 формируется с учетом переноса, поступающего на вход С предыдущего каскада и переноса, образованного АЛУ.

Выходы образования переноса G и распространения переноса Р увеличивают логические возможности АЛУ, позволяя использовать его совместно со схемой ускоренного переноса.

На выходах F1-F4 фиксируется результат операций, а на выходе с открытым коллектором Е - результат сравнения, соответствующий уровню логической "I" при равенстве между собой двух 4-разрядных чисел А и В.

Рис.П2.6.-1. Схема функциональная