- •Глава I

- •06Ласти применения эвм

- •1.6,1. СуперЭвм

- •Глава 2

- •8 Разрядов

- •11110001 11111001 11110001 11110111 А число — 6.285 запишется в память в виде слова из 6 байт:

- •Глава 3

- •Глава 4

- •Лечит узап j

- •Сверхоперативная или местная память

- •4.2. Адресная, ассоциативная и стековая организации памяти

- •Буфер входа-выхода

- •Усилители считывания-записи

- •Глава 5

- •Проклей

- •Идентификатор адреса (s байт)

- •Сектор на дискете

- •Глава 6

- •Управляющий блок автомат)

- •Глава 7

- •В цпршВляющай блок у б

- •Сумматор частичных произведений Регистр множимого

- •О vМножимое перед началом Выполнения умножения

- •Слой элементов и

- •Глава 9

- •Двойное слада па адреса о 32 бит

- •Слобо по адресу z в бит

- •Заслать в стек ад РеЗ

- •Загрузить аз стана в Pa V

- •Номер регист

- •Непосредственный операнд 1а

- •15Ю кГго 51

- •Оповещающий сив нал „Состояние

- •Блок ревастрод

- •Ветвление в макропроерамме по уело дую Акк*0

- •Макрокоманды управления последовательностью выборка микрокоманд

- •Окно процедуры

- •Регистры параметров (а) Регистры глобальных переменных |

- •1 Нуль м Знак-

- •Запоминание состояния процессора (программы)

- •Общий сигнал прерывания

- •Код приоритетного запроса

- •Маска ввоОагвывода

- •Прерывающая

- •01 23*56789 Время

- •I участка I

- •Запись льта мп

- •I Прием операндов на регистры 1

- •Умножение чисел с фиксированной точкой

- •Сложонив чисел с плавающей точкой

- •Глава 10

- •Вызов команды и модификация счетчика команд

- •Процедура тандемных пересылок

- •Однобайтная

- •16 Разрядов

- •Передача д стек а восстановление содержимого регистров

- •Команды досстаяовяения из стеки содержимого регистров

- •Блок сегментных регистров

- •Первый байт команды Второй ffaSm команды (постбайт адресации)

- •Сегментные селекторы

- •Регистры задачи и регистры дескрипторнои таблицы

- •Блок управления и контроля оп

- •Справочник страниц

- •Физическая память

- •16 Мбайт

- •Расширенная память

- •1 Мбайт

- •С каналом ес эвм

- •Связь с другой эвм

- •I Манипулятор % I Графа- I I типа „Мышь” I I построитель I

- •Глава 11

- •Интерфейс основной намята

- •Общее оборудование мультиплексного канала

- •Глава 12

- •Определения четности переносод

- •Глава 13

- •Ill:Выполнснис программы а Выполнение про ерам мы в

- •Пакеты заданий и Входные наборы данных

- •Выходные очереди разных классов в зу на дисках

- •I требует ‘'ода

- •Пользователь обдумывает | ответ системе I (новый запрос)

- •Блок управления памятью

- •Схемы совпадения

- •Шифратор номера отделения

- •Входной коммутатор

- •Коммутации

- •Сегментная таблица п-й программы

- •Векторные, средства

- •К периферийным устройством

- •К периферийным устройствам

- •Глава 15

- •Устройства Ввода- вывода

- •Процессор 2

- •Процессор 3

- •8 Векторных регистров (по 6* слова в каждом)

- •Готовности операндов

- •Глава 16

- •Комплекс абонентского пункта

- •16.2.. Классификация вычислительных сетей

- •1 Элемент

- •Время распрост- ранена*

- •Задержка сета лри коммутации пакетов[

- •Абонентская система

- •Данные пользователя

- •Сеансовый

- •Транспортный

- •Сетевой

- •Интерфейс высоког о уровня

- •Аппаратура передачи данных

- •Установление связи

- •Данные пользователя 00Длина поля и слови я обслуживания

- •Идентификатор протокола

- •7» Бшдта) Данные пользователя б вызове

- •Поток бит

- •Новый пакет (кадр)

- •Станция 1 ведет передачу

- •Передатчик Коаксиальный кйбель

- •Глава 15. Принципы организации многопроцессорных и многомашинных вычислительных систем (комплексов) и суперЭвм 489

- •1S в 7 о Слада па адресу ь

Устройства Ввода- вывода

IРУУЛ

с

дкп

U-

г

Дисковое

ЗУ Q

Ленточное

ЗУ

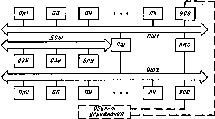

Рис. 15.4. Способы и средства системной организации в ЕС ЭВМ. Структура двухпроцессорного комплекса ВК2П46:

ВТМК

иБЛМК

—

байт-

и блок-мультиплексные каналы;АОП

— адаптер

оперативной памяти;РУУД

иРУУЛ

—

разделенные устройства управления

соответственно дисковыми и ленточными

ЗУ;ДКП

—

двухканальный переключатель;ПКФ

—

пульт

конфигурации комплекса

(находится в общем регистре, указанном в поле /?3 команды) и приказ (находится в полях Вг, команды). С помощью соответствующих приказов вызываемый процессор может быть установлен в состояние стоп или работа; в него может быть произведена начальная загрузка микропрограмм, могут быть вызваны экстренное внешнее прерывание и некоторые другие процедуры.

Синхронизация часов. В МПК должна быть едидая служба астроно-

мического времени, что достигается соответствующей синхронизацией часов процессоров путем одновременного изменения значений младших разрядов всех часов.

Общее поле памяти многопроцессорных вычислительных комплексов в ЕС ЭВМ реализуется либо с помощью многовходовых адаптеров модулей памяти, либо с помощью коммутаторов межмодульных связей (коммутаторов перекрестных связей). Так, например, в двухпроцессорном ВК на основе ЭВМ ЕС-1046 общее поле ОП (до 8 Мбайт) строится с использованием двухвходовых адаптеров основной памяти (АОП) (рис. 15.4) [68].

В ЕС ЭВМ на основе рассмотренных средств комплексирования можно создавать многомашинные комплексы, содержащие до четырех ЭВМ, причем каждая из них может быть двухпроцессорной.

Важным направлением повышения производительности ЭВМ и систем общего назначения является включение в их состав специализированных процессоров, ориентированных на определенный круг задач. Примером является «матричный процессор» !, подключаемый через двухбайтный интерфейс ввода-вывода к блок-мультиплексному каналу. Процессор воспринимает и по-своему интерпретирует команды ввода-вывода и управляющие слова канала, при этом обеспечивается возможность параллельных вычислений в процессоре ЭВМ и матричном процессоре. Матричный процессор предназначен для выполнения над потоком входных данных операций свертки, корреляции, преобразования Фурье, операций над матрицами и векторами. В матричном процессоре при выпол- нении арифметических операций реализуется конвейерная обработка (совмещаются операции умножения, сложения с нормализацией, выдача результатов). ЭВМ ЕС-1046 в штатном составе имеет производительность 1300 тыс. опсраций/с, а при подсоединении матричного процессора и решении задач с многократно повторяющимися действиями над группой данных (например, матрицами) производительность возрастает до 30 млн. эквивалентных операций/с.

Многопроцессорные и многомашинные комплексы с общей шиной (СМ ЭВМ)

Организация межмодульных (и межмашинных) связей на основе общей шины является одним из распространенных способов построения многопроцессорных и многомашинных вычислительных комплексов.

1Здесь термин «матричный» отражает ориентацию этого специализированного процессора на решение задач матричной алгебры, а в § 15.5 этот же термин характеризует структуру многопроцессорной системы.

Общая структура многопроцессорной системы с общей шиной изображена на рис. 15.5. Входящие в состав системы процессоры, модули ОП, блоки управления периферийными.устройствами (ВЗУ и устройствами ввода-вывода) подключены к одной общей шине, состоящей из линий, по которым передаются информационные и управляющие сигналы.

Одновременно через общую шину может передаваться информация только между двумя устройствами, т. е. шина используется подсоединенными к ней устройствами в режиме разделения времени. Это является цричиной возникновения конфликтов, при которых несколько устройств претендуют на занятие шины. Наличие конфликтов на общей шине вызывает простои оборудования и уменьшает производительность системы. Частоту возникновения конфликтов и потери из-за них производительности удается снизить, если наряду с общей доступной всем процессорам памяти иметь для каждого процессора небольшую местную (локальную) оперативную память, к которой процессор может обращаться непосредственно, минуя общую шину [26].

Из-за конфликтов в общей шине, снижающих производительность системы, организация межмодульных связей на основе общей шины не находит применения в МПС, ориентированных на достижение высокой производительности. Однако общая шина широко применяется при построении многопроцессорных и многомашинных вычислительных комплексов, предназначенных для обеспечения повышенной надежности и живучести, необходимой производительности и пропускной способности при работе в режиме реального времени в различных системах управления технологическими процессами, автоматизации экспериментов и испытаний и др. Применению шинной структуры способствует то, что в оборудовании этих комплексов широко используются малые и микроЭВМ, микропроцессорные средства, в которых реализованы различные модификации интерфейса «общая шина».

В СМ ЭВМ при построении на основе аппаратуры малых ЭВМ многопроцессорных и многомашинных комплексов с шинной структурой в качестве средств комплексирования (систем-

процессорныв Модули

модули памяти

фф-ф фф-ф

Шина

межмодульных связей

Рис.

15.5. Многопроцессорные ВС с общей шиной

межмодульных связей

Периферийные

устройства

Рис.

15.6. Пример использования системных

средств СМ ЭВМ — переключателя шины

(ПШ) и адаптера межшинной связи (АМС)

для построения многомашинных и

многопроцессорных комплексов:

Пр1,

Пр2—

процессоры;У

СО—

устройство связи с объектом управления;БПУ—

быстродействующее печатающее устройство

ных средств) служат переключатель шины (ПШ) и адаптер межшинной связи (АМС) (рис. 15.6) [40, 56].

Переключатель шины. С помощью ПШ дополнительная общая шина ДОШ с подсоединенным к ней оборудованием может быть подключена к общей шине одного из двух процессоров комплекса или устанавливаться в отключенное состояние. Дополнительная общая шина допускает подключение любых устройств (модулей памяти, ПУ и др.), кроме процессоров.

После подключения ДОШ становится участком соответствующей общей шины комплекса и обмен с подсоединенным к ней оборудованием как программно-управляемый, так и с прямым доступом производится по обычным процедурам интерфейса общей шины.

Адаптер межшинной (межинтерфейсной) связи предназначен для осуществления быстрого доступа процессора и ПУ одного комплекса к памяти и ПУ другого комплекса. Здесь под комплексом понимается совокупность устройств, подключенных к одной общей шине.

Наличие АМС позволяет реализовать совместное решение комплексами задачи, иерархическую организацию обработки данных с обменом данных между главным и подчиненным комплексами, различные режимы резервирования оборудования.

Межмашинная связь с помощью АМС основана на автоматическом преобразовании адресов в командах инициировавшего

межкомплексный обмен информацией «комплекса-задатчика: в адреса «комплекса-исполнителя». Это преобразование осуще ствляется с помощью окна интерфейса, представляющего co6oi фиксируемую при изготовлении комплекса часть неиспользуе мых им адресов. Размер окна ограничивает размер блока дан ных, передаваемых из одного комплекса в другой.

Адаптер позволяет производить обращение устройства одно го комплекса с помощью команд процессора через окно к устрой ствам другого комплекса для выборки команды, записи и считы вания данных, реализуемых в этом случае в другом комплекс» как передача с прямым доступом и выполнение запроса про граммного прерывания из другого комплекса.

Процессор задает область адресов, к которым через. сво< окно может обратиться другой комплекс, имеет возможност) запретить обращение из другого комплекса к устройствам своеп комплекса или только запретить запись в свои устройства, за претить прерывание от другого комплекса.

Входящий в состав АМС регистр исполнительного адреса (младши! его разряды носят название регистра смещения) содержит сформирован ный окном исполнительный адрес обращения к другому комплексу МладпЫе разряды этого адреса («смещение») берутся из адреса окна выставленного на своей шине комплексом — инициатором обмена а старшие — из регистра адреса «перемещения», устанавливаемого дру гим комплексом при подготовке обмена через окно.

Организация связи между комплексами через окна интерфейса по ясняется на рис. 15.7. Адресное пространство 0—64 К обоих комплек сов используется модулями памяти. Неиспользуемые 8 К адресов (64— 72 К) предоставлены для окна интерфейса (фиксируются при изготовле нии комплекса). При подготовке передачи комплекс-исполнитель за сылает перемещение в АМС, устанавливая таким образом связь окн* другого комплекса с областью своих адресов. Так, на рис. 15.7 первы»

Адреса

_УЧ_

OKHgZ

8К ГОК 2*К 3ZKWK49К 56К 6+К7ZK 80К век 9бК1МК11гК120КП8К

Ч

1 1 1 1 *■

«*-

1

Адреса подсоединенных модулей памяти

Г

Неиспользуемые

адреса

Адреса регистр од ПУ

-I—I—I—I—I—

0Ш11 1 Н

вк юк гьк згк но к *вк 56 к bw^zkjbok век зек ючкткпоктк

Окно 1

Рис. 15.7. Организация межшинной связи через окно интерфейса

комплекс через свое окно связан с ПУ второго комплекса, а второй комплекс — через свое окно с областью 24—32 К памяти первого комплекса. Время преобразования адреса в окне составляет примерно 300 не.

Рассмотрим особенности процедуры выполнения процессором Пр2операции с использованием в качестве операнда слова с адресомАиз памяти первого комплекса. ПредварительноПр2устанавливает в АМСперемещение— группу старших разрядов адреса, задающих область памяти с адресом Л, и выдает команду чтения по адресу Л', Принадлежащему окну2.Выполняя эту команду,Пр2устанавливает наOU12 запрос на чтение по адресуА'.Окно 2 с помощью перемещения, предварительно установленногоПр2>трансформирует этот адрес в адресАобласти памяти первого комплекса и выставляет наОШ1запрос прямого доступа. Запрашиваемая информация (слово) из адресаАпамяти первого комплекса передается во входной буферный регистр АМС. Затем это слово из выходного буферного регистра пересылается поОШ2в процессорПр2.

Аналогично одной командой выполняется передача блока информации от одного комплекса другому. Например, для передачи в память первого комплекса блока данных с ЗУ на дисках второго комплекса процессор Пр1предварительно устанавливает перемещение для задания области своей памяти (24—32 К), куда будут записываться данные с ЗУД, и выдает наОШ1запрос на чтение по соответствующему адресу из области адресов своего окна. Окно / преобразует этот адрес в адрес регистраЗУДи выставляет наОШ2запрос прямого доступа для передачи блока данных сЗУДпо адресам окна 2, при этом адреса окна 2 преобразуются в адреса области (24—32 К) памяти первого комплекса, установленной перемещением.

На одной ОШ может быть организовано несколько окон (выделено несколько областей неиспользуемых адресов) для связи с несколькими комплексами.

На рис. 15.6 показан пример использования ПШ и АМС для построения на основе оборудования СМ ЭВМ многомашинных управляющих вычислительных комплексов. В представленной структуре реализуются общее поле памяти и общее поле ВЗУ, двухпроцессорная параллельная обработка данных и резервирование наиболее важных для управления объектом устройств — процессора, памяти, УСО и некоторых ПУ.

Особенности организации отказоустойчивых многопроцессорных вычислительных комплексов

Перспективы широкого применения построенных на основе микроЭВМ и микропроцессоров управляющих вычислительных устройств (УВУ) и комплексов (УВК) для управления в реальном масштабе времени различными технологическими процесса-

ми и установками выдвигают на первый план проблему обеспе- * чения надежности их работы. Управляющие комплексы и устройства, работающие в составе различных АСУ ТП, должны обеспечивать длительное достоверное (безошибочное) функционирование без остановки технологического процесса при сбоях и отказах в оборудовании УВУ и УВК. В ряде случаев предъявляются жесткие требования в отношении недопустимо- ^ сти перерывов или задержек в осуществлении УВУ и УВК управляющих функций.

Указанную проблему призваны решать отказоустойчивые УВУ и УВКу т. е. устройства и комплексы, которые сохраняют £ работоспособность, при выходе из строя отдельных элементов, ; узлов или модулей.

Вопросам обеспечения отказоустойчивости уделялось довольно много внимания в рамках ЭВМ III поколения, и при этом получены определейные результаты; например, в составе ?ЕС ЭВМ и СМ ЭВМ созданы многомашинные и многопроцессорные комплексы (см. § 15.2 и 15.3), хотя ЭВМ ЕС, как, впрочем, и машины СМ ЭВМ, сначала проектировались в основном ' для одномашинного и однопроцессорного режимов работы. Но- . вые возможности, связанные с небольшими размерами и сравнительно низкой стоимостью микропроцессорных и других БИС, J позволяют существенно продвинуться в этом направлении путем ^ создания ЭВМ и комплексов со специальной архитектурой, ори- ентированной на достижение отказоусточивости.

Основным принципом, на основе которого создаются отказоустойчивые ЭВМ, системы и комплексы, является аппаратурная избыточность. В настоящее время определилось несколько направлений в организации отказоустойчивых вычислительных ^комплексов. При сравнении этих направлений следует учитывать гразмеры аппаратурной избыточности (хотя в ряде случаев это [может и не иметь определяющего значения), меру обеспечения «достоверности результатов обработки комплексом данных, степень исключения влияния сбоев и отказов в аппаратуре на изменение временной диаграммы выдачи результатов обработки данных на объект управления.

Надежность УВУ и УВК при необходимости длительного функционирования весьма сильно зависит от степени их приспособленности к техническому обслуживанию (в первую очередь от ремонтопригодности) в конкретных условиях эксплуатации. Этот показатель может в ряде случаев оказаться основным при выборе варианта построения отказоустойчивых УВУ и УВК.

Организация отказоустойчивого УВК (его структура, динамическое изменение конфигурации и т. п.) должна быть «прозрачной» для пользователя в том смысле, что пользователь при взаимодействии с УВК и при подготовке и отладке программ для него должен воспринимать комплекс как обычную однопроцессорную ЭВМ с неизменной конфигурацией.

Отказоустойчивые УВК с автоматической реконфигурацией. Обычно функции (программы), реализуемые УВК, неравнозначны, и временная утрата некоторых второстепенных функций при сохранении основных жизненно важных допустима. Поэтому для таких УВК основной характеристикой надежности следует считать не среднее время наработки на отказ, используемое для оценки надежности ЭВМ общего назначения, а вероятность сохранения на заданном интервале любой из основных функций вследствие отказов отдельных модулей системы. Эта вероятность может быть принята за меру живучести комплекса. Особенности построения отказоустойчивых УВК с автоматической реконфигурацией описаны в [51].

Отказоустойчивость достигается введением избыточного оборудования и логической организацией, обеспечивающей при отказах в оборудовании автоматическую реконфигурацию системы для сохранения жизненно важных функций, возможно, ценой утраты второстепенных. Системы, обладающие указанной способностью, иногда называют «системами с элегантной деградацией».

Основными принципами построения отказоустойчивых комплексов на основе автоматической реконфигурации являются многоустройственность (в том числе многопроцессорность), общие поля процессоров; оперативной памяти, каналов и периферийных устройств, динамическое распределение функций между однотипными устройствами.

Многоустройственность предполагает, что система должна содержать несколько экземпляров однотипных устройств (процессоров, модулей ОП, каналов и др.), при этом должна быть обеспечена избыточность устройств всех типов по отношению к минимальному набору, необходимому для выполнения жизненно важных функций.

Динамическое распределение функций означает, что программы не привязаны жестко к процессорам, каналам и ПУ. Заранее неизвестно, какое из однотипных устройств будет выполнять данную функцию. Более того, работа может быть начата на одном, продолжена на другом и закончена на третьем устройстве.

Наличие общих полей устройств и динамического распределения функций позволяет комплексу сохранять работоспособность, пока имеется хотя бы по одному исправному устройству каждого типа.

Практическое осуществление отказоустойчивых УВК с автоматической реконструкцией требует реализации рассматриваемых ниже логических свойств.

Многосвязные интерфейсы позволяют многовходовым устройствам связываться друг с другом по независимым шинам.

Динамическое распределение (диспетчирование) программ. В ОП организуются очереди для программ (работ), имеющих различные уровни приоритета. Аппаратура выделяет среди процессоров кандидата на прерывание, которым является процессор, обрабатывающий программу наименьшего приоритета.

Аппаратура непрерывно сравнивает приоритет программы процессора — кандидата на прерывание с приоритетом программ, находящихся в очередях. Если в очереди появляется программа большего приоритета, процессор-кандидат прерывает свою программу, заносит ее в очередь соответствующего приоритета и начинает выполнять программу из непустой очереди наибольшего приоритета. Обработка прерванной программы будет продолжена, причем необязательно на. том же процессоре, когда ее приоритет станет выше приоритета программы — кандидата на прерывание. Следует обратить внимание на то, что здесь образуется общая очередь к освобождающимся процессорам.

Описанный механизм обеспечивает в каждый момент времени выполнение наиболее приоритетных программ на наличных исправных процессорах.

Системы автоматического контроля правильности работы устройства и диагностирования — см. гл. 12.

Иерархия рестартов (восстановлений) программ при сбоях и отказах. Для уменьшения потерь времени на восстановление программ после сбоев и отказов следует иметь возможность восстанавливать работоспособность программ на разных уровнях: 1) сбои и отказы в ОП; б) сбои в процессорах и каналах; в) отказы в процессорах и каналах; г) сбои и отказы в периферийных устройствах.

В ОП сбои и отказы исправляются с пдмощью самокорректирующего кода Хэмминга (см. гл. 42).

Микрокомандный рестарт. Средства контроля проверяют правильность каждой микрооперации, и при неправильном выполнении микрокоманда повторяется. Для микрокомандного рестарта необходимо, чтобы в процессе исполнения микрооперации сохранялись ее операнды. Это требует дополнительного оборудования (регистров и др.) и приводит к некоторому уменьшению скорости работы процессора.

Если при повторении микрокоманда выполнится правильно, обработка программ на устройстве продолжается. Если повторение микрокоманды установленное число раз не дает правильного результата, фиксируется отказ.