VHDL 801а вопросы на экзамен / Матрица

.pdfМинистерство образования и науки

Государственное образовательное учреждение высшего профессионального образования

«Новосибирский государственный университет» (НГУ)

Высший колледж информатики НГУ (ВКИ НГУ)

Кафедра информационных технологий

А. Н. Салтовский

Проектирование цифровых схем на основе ПЛИС

Методические указания

Новосибирск 2013

1

Составитель: Салтовский А. Н.

Проектирование цифровых схем на основе ПЛИС

Пособие содержит материалы для изучения инженерного применения ПЛИС Xilinx при создании цифровых автоматов в рамках лабораторных практикумов и курсового проектирования. Рассмотрен необходимый инструментальный комплекс – САПР Xilinx ISE и отладочный модуль для CPLD Cool Runner-II. Тематика охватывает ключевые аспекты проектирования на основе ПЛИС: создание цифрового устройства с помощью схемотехнического редактора или на основе программы на языке VHDL, синтез кристалла, функциональное и временное моделирование, особенности конфигурирования.

Материалы пособия соответствуют программе спецкурса «Введение в программирование ПЛИС» и будут полезны студентам третьего и четвертого курса ВКИ НГУ, которые изучают технологию проектирования современных контрольно-измерительных и управляющих систем.

2

Оглавление

1.Что такое ПЛИС и чем они интересны

2.Архитектура ПЛИС – основные понятия

3.Этапы проектирования в САПР Xilinx ISE

4.Первый проект

5.Проектирование устройства в схемотехническом редакторе

6.Трассировка и конструкторский файл

7.Функциональное и временное моделирование проекта

8.Конфигурирование кристалла ПЛИС

9.Создание проекта средствами языка VHDL

10.Список литературы

3

Что такое ПЛИС и чем они интересны

Современные технологии микроэлектроники практически перенесли традиционные инструменты создания программ (software) в зону аппаратных методов обработки информации (hardware). Безусловными лидерами при создании разнообразных цифровых автоматов являются программируемые микроконтроллеры и ПЛИС.

FPGA (field programmable gate array), или ПЛИС (программируемые логические интегральные схемы), представляют собой цифровые интегральные микросхемы, состоящие из программируемых логических блоков и программируемых соединений между этими блоками. Возможность конфигурировать эти устройства позволяет инженерам-разработчикам решить множество различных задач.

По сравнению с программируемыми микроконтроллерами универсальность ПЛИС значительно выше: во-первых, в матрице можно создать микроконтроллер с определенными свойствами, во-вторых, от этой предыдущей функциональности матрица может перейти к другой. Например, часть времени ПЛИС может представлять PIC-процессор, а потом изменить свою конфигурацию и поработать сигнальным процессором и вновь вернуться к прежней конфигурации. То есть слово «field» в названии матрицы означает, что внутренняя функциональность не является жестким атрибутом и может быть изменена «в полевых условиях» обработки информации.

Привлекательность данной технологии проектирования заключается в представляемой конечному пользователю возможности быстрого создания цифровых устройств с произвольной внутренней структурой.

Вместе с тем есть определенные ниши в специализированной обработке, которые устойчиво принадлежат ПЛИС.

Заказные интегральные схемы. У заказчика не всегда есть желание декларировать свои решения или алгоритмы. ПЛИС идеально приспособлено для охраны авторского права.

Цифровая обработка сигналов. Традиционно этот тип высокоскоростной обработки принадлежал сигнальным процессорам (DSP). Однако современные ПЛИС содержат встроенные умножители, схемы ускоренного арифметического переноса и большой объем оперативной памяти внутри кристалла. Все это в сочетании с высокой степенью параллелизма выполняемых в ПЛИС операций обеспечивает значительное преимущество ПЛИС над самыми быстрыми сигнальными процессорами в 500 и более раз.

Встраиваемые микроконтроллеры. Несложные задачи управления обычно выполняются встраиваемыми процессорами специального назначения, которые называются микроконтроллерами. Все что необходимо для организации микроконтроллера – таймеры, память команд, интерфейсы ввода/вывода расположены рядом с ядром на одном кристалле. С одной стороны это позволяет просто решать задачи аппаратного интерфейса, например, с сенсорами, с другой – стоимость ПЛИС падает и это делает все более привлекательными для реализации функций микроконтроллеров.

Физический уровень передачи данных. ПЛИС уже давно используется в качестве связной логики, выполняющей функцию интерфейса между микросхемами, реализующими физический уровень передачи данных, и высшими уровнями сетевых протоколов. Тот факт, что современные

4

ПЛИС могут содержать множество высокоскоростных передатчиков, означает, что сетевые и коммуникационные функции могут быть реализованы в одном устройстве.

Системы с перестраиваемой архитектурой. Программные алгоритмы могут быть значительно ускорены аппаратными методами, если будут использованы такие свойства ПЛИС, как параллелизм и перенастраиваемость. Такие свойства востребованы широким спектром инженерных задач – от моделирования аппаратуры до криптографического анализа.

Архитектура ПЛИС – основные понятия

Простейшим видом программируемого логического устройства является обычная микросхема ПЗУ. Действительно, обладая N адресными линиями и М линиями данных, микросхема ПЗУ может реализовать М N-входных логических функций. Содержимое ПЗУ может рассматриваться как таблица истинности некоторой цифровой схемы, содержащей комбинаторную логику. Использование ПЗУ в качестве логических генераторов долгое время было эффективным приемом, позволявшим резко снизить количество корпусов микросхем при решении задач аппаратной обработки.

Простую программируемую функцию, представляющую основу дальнейшего рассказа о ПЛИС, представляет следующая схема (Рис.1).

Рис.1. Простая программируемая функция

Совершенно ясно, что характер активации предполагаемых перемычек позволяет изменять таблицу истинности функции. Технология создания перемычек может быть различной. От плавких перемычек и фотошаблонов, программируемых в заводских условиях изготовления кристалла до различных типов ЗУ. Кроме того, перемычки соединяют и коммутируют между собой массивы подобных блоков. Нас будет интересовать механизм создания перемычек с помощью электрически стираемых постоянных запоминающих устройств (ЭСПЗУ) и Flash-ЗУ. Именно такие запоминающие устройства являются теневыми партнерами ПЛИС и хранят информацию о созданной в процессе проектирования цифрового устройства конфигурации ПЛИС.

Внастоящее время наиболее распространенные серии ПЛИС имеют следующую архитектуру:

CPLD (Complex Programmable Logic Device), устройства, использующие для хранения конфигурации энергонезависимую память (Flash или ЭСПЗУ);

5

FPGA (Field Programmable Gate Array), устройства, использующие для хранения конфигурации энергозависимую память, которая требует инициализации после включения питания.

Характерным представителем ПЛИС, выполненным в технологии CPLD, и который используется в лабораторном практикуме, является кристалл CoolRunner-II. Эти устройства отличаются пониженным энергопотреблением – статический ток не превышает 100 мкА.

Структурная схема ПЛИС CoolRunner-II представленная на Рис.2 содержит четыре основных функциональных узла:

I/O Blocks – блоки ввода/вывода. Каждый блок связан со своим контактом (pin) корпуса микросхемы.

Functional Block – функциональный блок. В кристалле лабораторного практикума – CoolRunner XC2C256 – таких блоков 256, и каждый, в свою очередь, состоит из шестнадцати независимых макроячеек.

AIM - расширенная матрица межсоединений. Коммутация сохраняется после отключения питания.

JTAG – выводы, через которые производится периферийное сканирование и программирование микросхемы.

Рис.2 Структурная схема CPLD CoolRunner

Микросхемы с организацией FPGA используют энергозависимую статическую память для хранения конфигурационной информации. Разумеется, это требует повторной инициализации после включения, например, электропитания. И здесь, в качестве источника информации может выступить какое-либо предусмотренное проектировщиком, ЗУ. Это может быть небольшое Flash-ЗУ, установленное на плате рядом с матрицей. Но возможна и загрузка, к примеру, непосредственно из памяти персонального компьютера, то есть из иной микропроцессорной системы. Функциональная сложность и логическая организация FPGA значительно сложнее, чем у матриц CPLD. Соответственно и ресурс предоставляемый разработчику цифрового устройства значительно выше. Причиной этому является предоставление матрицей FPGA большого объема памяти (триггеров).

6

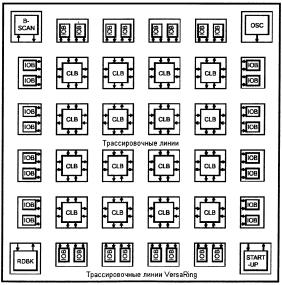

Структура матрицы (Pис.3) FPGA Spartan-3 – а именно эта матрица на отладочном стенде лабораторного практикума – содержит уже знакомые функциональные узлы: блоки ввода-вывода, загрузочный интерфейс JTAG.

Рис.3 Структура ПЛИС FPGA Spartan

Но основным массовым элементом в этой архитектуре является конфигурируемый логический блок (CLB). Кроме двух триггеров каждый блок содержит собственный фрагмент коммутатора (LUT

– Look-Up Table, таблица истинности). В составе FPGA отсутствует Flash-память для хранения конфигурации. Для хранения таблицы истинности должны быть занесены в обычную статическую память. Ее фрагментами и являются LUT, которые представляют собой блоки памяти с организацией

16х1.

Следует отметить особенности блоков ввода-вывода: современные семейства ПЛИС поддерживают до 20 электрических интерфейсов, включая TTL и CMOS с множеством разновидностей, а также высокоскоростные дифференциальные интерфейсы, такие как, LVDS, LVPECL и др. Тип интерфейса, реализуемый в различных блоках можно установить при проектировании индивидуально. В составе ПЛИС FPGA Xilinx в качестве дополнительных ресурсов могут быть: блочная память (Block RAM), блоки распределения тактовых сигналов (DLL – Delay Locked Loop), умножители, до двух аппаратно реализованных ядер процессора PowerPC. Разумеется, все эти возможности определяются типом используемой матрицы. Для FPGA фирмы Xilinx – это серии Spartan и Virtex.

Обратите внимание, в обозначении ПЛИС FPGA присутствует их информационная емкость. в тысячах эквивалентных логических вентилей (например, Spartan-3 XC3S200 имеет 200 тыс. вентилей).

В обзоре Xilinx, посвященном новой серии Virtex, указывается, что за последнее десятилетие информационный объем ПЛИС увеличился в 250 раз, рабочие частоты - в 25, пропускная способность памяти – в 800, а пропускная способность внешних интерфейсов – в 1000 раз. Одновременно стоимость ПЛИС упала в 350 раз. Успехи конструкторов и технологов ведущих фирм-производителей ПЛИС – Xilinx и Altera - позволяют сказать, что ПЛИС – инструмент инженеров-схемотехников будущего.

7

Этапы проектирования в САПР Xilinx ISE

Источником выполнения любого технического проекта является техническое задание. Немного позднее, при наличии финансирования, появляются средства. Такое средство, как САПР Xilinx ISE 10.1i, не потребует от нас денежных вложений (freeware download), но потребует определенных трудозатрат для освоения технологии проектирования. А в качестве задания будем проектировать – для простоты – обычный многоразрядный двоичный счетчик.

САПР Xilinx ISE 10.1i состоит из пакета специализированных программ. В рассказе о последовательных этапах проектирования они будут именоваться вместе с задачами, которые они выполняют в проекте.

Вся цепочка этапов проектирования выглядит следующим образом.

Создаем папку нового проекта и указываем тип ПЛИС, с которой будем работать.

Рисуем принципиальную схему проектируемого устройства в схемотехническом редакторе Xilinx ISE Design Suite 10.1 (FPGA Editor) или создаем описание данного устройства на языке VHDL или Verilog. Созданный файл включаем в проект и записываем.

После первого запуска автоматического трассировщика Implement Design выявляются грубые ошибки проекта, но главное (при успешном завершении) – получим возможность работы с системой моделирования. Выполняем функциональное или временное моделирование создаваемого устройства (Behavioral Simulation) для выявления ошибок и проверки работоспособности проекта или его отдельных частей.

Далее привязываем выводы проекта к вводам-выводам кристалла и уточняем, например, характер выходной уровень сигналов – создаем конструкторский файл (Constraints Editor).

Снова запускаем Implement Design для автоматизированного размещения проекта в кристалле и анализируем генерируемые отчеты для выявления ошибок. Если ошибки отсутствуют – переходи к следующему этапу.

Поскольку физическая привязка к топологии кристалла завершена, то выполняется верификация проекта – окончательное временное моделирование (Post-Fit Simulation) при всех реальных задержках внутри микросхемы ПЛИС.

Если модель удовлетворяет функциональным требованиям технического задания, то конфигурируем кристалл ПЛИС с помощью битового потока (iMPACT 10.1).

Небольшое уточнение: чтобы конфигурировать ПЛИС необходимо иметь загрузочный JTAGкабель. Загрузка битового потока осуществляется через специально выделенные конфигурационные выводы ПЛИС с использованием различных способов и режимов загрузки. После удачной загрузки конфигурации проект проверяется и отлаживается на плате, на которой устанавливается ПЛИС. В случае необходимости корректировки или дальнейшего развития проекта на ПЛИС все пройденные этапы повторяются до полного завершения проекта в целом.

Первый проект

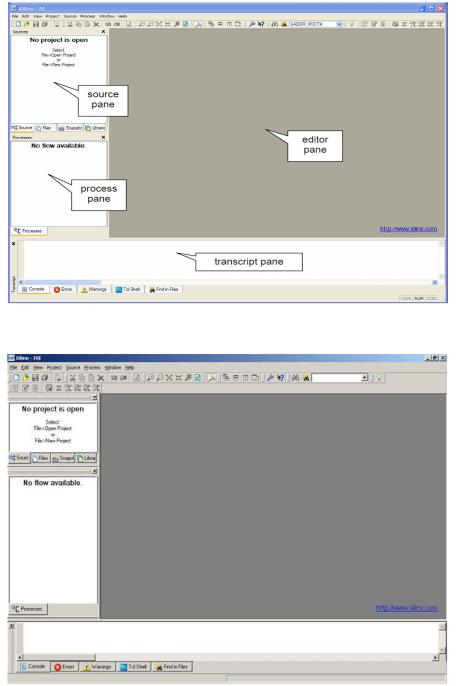

После установки и регистрации программного обеспечения на рабочем столе компьютера появляется иконка Xilinx ISE 10.1, Запускаем с ее помощью систему проектирования. Видим следующее окно - Навигатора проекта (Project Navigator).

8

Рис.5 Рабочее поле схемотехнического редактора

Выбираем меню File -> New Project для создания нового проекта. Заполняем и выбираем все необходимые поля предлагаемые мастером создания нового проекта (New Project Wizard) в открывшемся окне диалога.

Следует отметить, что рабочую папку создаем на корневом диске и на трассе доступа к рабочим файлов нежелательны шрифты кириллицы (например, «Рабочий стол»). Назовем первый проект «First», а в качестве основного информационного источника укажем файл, который будет создан с помощью схемотехнического редактора.

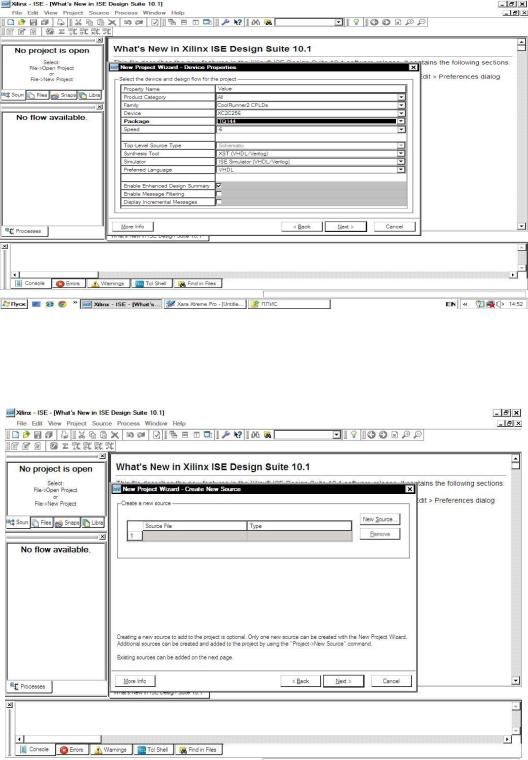

На следующем шаге работы мастера (Wizard) уточняем следующие детали: во-первых, сообщаем через падающие окна, что работаем с матрицей CPLD CoolRunner-II, содержащей 256

9

блоков, выполненной в пластмассовом корпусе TQ-144. Именно такая матрица размещена на плате лабораторного стенда. Во-вторых, что будем пользоваться для моделирования проектируемого устройства симулятором, встроенным в пакет САПР.

Рис.6 Указываем тип матрицы и ее особенности

Далее Wizard предлагает присоединить исходный файл проекта. Пропустим этот шаг, скажем Next. Файл схемотехники присоединим позднее, в процессе непосредственного создания.

Рис.7 Возможность подсоединения стороннего файла пропускаем

Наконец, мастер создает файл отчета о наших намерениях в проекте - файл проекта. Нажимаем Finish и переходим к следующему этапу проектирования.

10