Allen and Holberg - CMOS Analog Circuit Design |

|

Page V.2-5 |

|||||

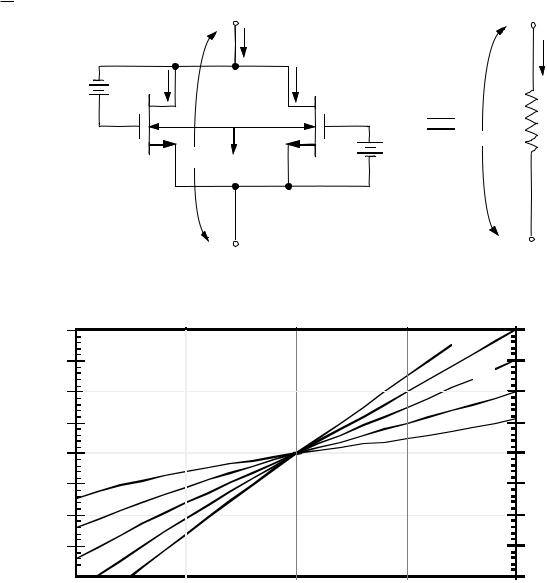

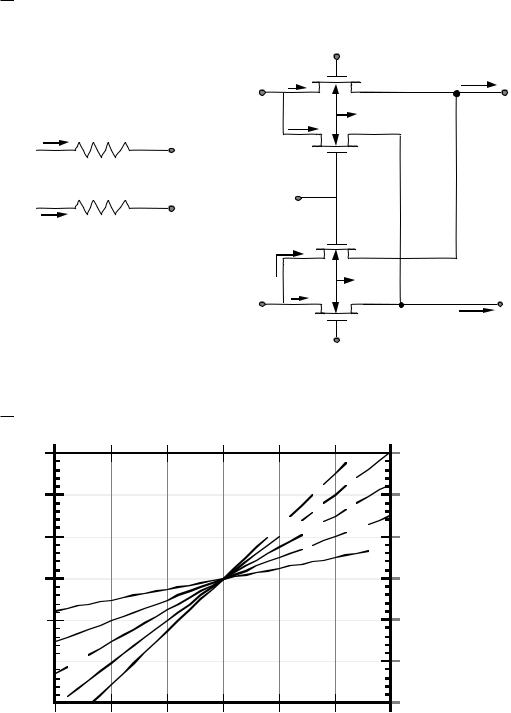

NMOS Parallel Transistor Realization : |

|

|

|||||

|

|

|

+ |

|

|

|

+ |

|

|

|

D1 |

i |

D2 |

|

i |

- |

|

|

|

|

|||

|

i |

|

|

i2 |

|

|

|

VC |

|

1 |

|

|

|

||

|

|

|

|

|

|

||

+ |

|

|

|

|

|

G2 + |

r ac |

G1 |

|

|

|

|

|

||

M1 |

|

|

|

|

VC |

v |

|

|

|

v VSS |

|

M2 |

|

||

|

|

|

|

- |

|

||

|

|

|

|

|

|

|

|

S1 |

S2 |

|

|

- |

_ |

|

|

Voltage-Current Characteristic : |

|

2mA

1mA

I(VSENSE) |

0 |

|

-1mA

-2mA

-2

Vc=7V 6V

6V

5V

W=15u |

4V |

|

|

L=3u |

3V |

VBS= 5.0V |

|

-1 |

0 |

1 |

2 |

VDS

NMOS parallel transistor realization M1 2 1 0 5 MNMOS W=15U L=3U M2 2 4 0 5 MNMOS W=15U L=3U

.MODEL MNMOS NMOS VTO=0.75, KP=25U, LAMBDA=0.01, GAMMA=0.8 PHI=0.6

VC 1 2

E1 4 0 1 2 1.0 VSENSE 10 2 DC 0 VDS 10 0

VSS 5 0 DC -5

.DC VDS -2.0 2.0 .2 VC 3 7 1

.PRINT DC I(VSENSE)

.PROBE

.END

Allen and Holberg - CMOS Analog Circuit Design |

Page V.2-6 |

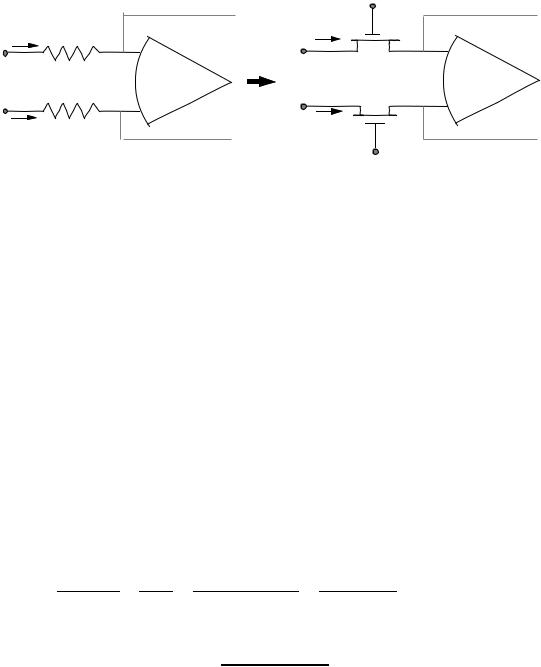

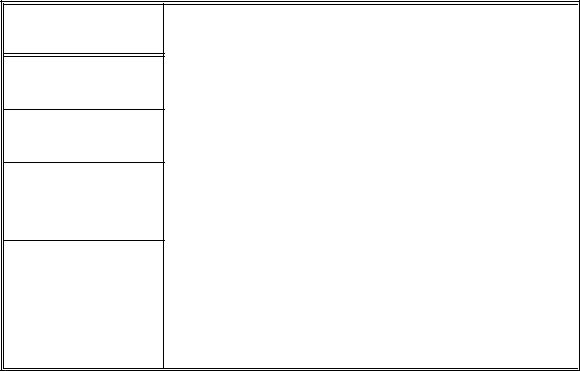

P-Channel Extended Range Active Resistor Circuit

|

vAB |

|

|

|

iAB |

|

VDD |

|

|

|

|

M2A |

|

|

M2B |

|

+ |

M1A |

+ |

|

V |

|

|

|

|

VC |

|

|

-C |

|

|

|

|

|

M1B |

|

|

|

- |

M3A |

+ |

|

M3B |

|

V |

|

|

|

- |

C |

|

VSS

Voltage Current Characteristics

100uA

4V

4V

5V

60uA

3V

20uA |

|

Vc=2V |

|

i AB |

|

|

|

- 20uA |

|

|

|

- 60uA |

|

|

|

-100uA |

|

|

|

-4 -3 -2 -1 |

0 1 |

2 |

3 |

|

VAB |

|

|

P-Channel Extended Range Active Resistor M1A 3 4 5 10 MPMOS W=3U L=3U

M1B 3 6 5 10 MPMOS W=3U L=3U

M2A 10 3 4 4 MNMOS W=3U L=3U

M2B 10 5 6 6 MNMOS W=3U L=3U M3A 4 7 0 0 MNMOS W=3U L=3U

M3B 6 7 0 0 MNMOS W=3U L=3U

VSENSE 1 3 DC 0V

VC 7 0 VAB 1 5

VDD 10 0 DC 5V

.MODEL MNMOS NMOS VTO=0.75, KP=25U

+ LAMBDA=0.01, GAMMA=0.8 PHI=0.6

.MODEL MPMOS PMOS VTO=-0.75 KP=8U +LAMBDA=0.02 GAMMA=0.4 PHI=0.6

.DC VAB -4.0 4.0 0.2 VC 2 5 1

.PRINT DC I(VSENSE)

.PROBE 4 .END

.PROBE 4 .END

Allen and Holberg - CMOS Analog Circuit Design |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Page V.2-7 |

||||||||||||||||||||||||||||||||

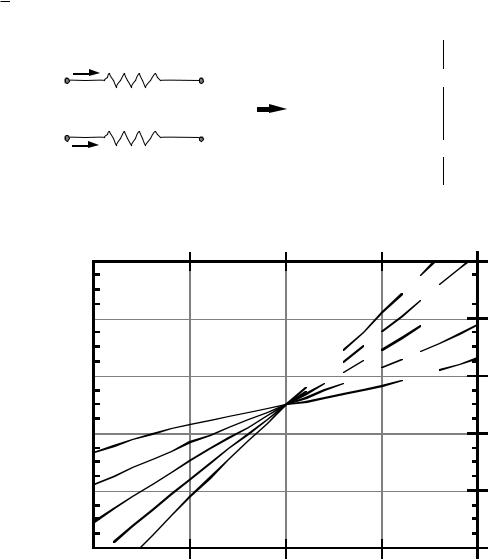

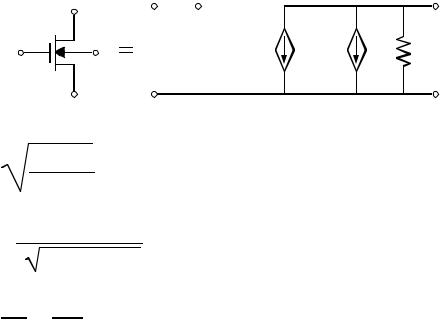

THE SINGLE MOSFET DIFFERENTIAL RESISTOR |

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VC |

|

|

|

|

|

|

|||

|

v1 |

|

i1 |

|

R |

|

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

v1 |

|

|

i1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

v2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

v2 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

- v1 |

|

|

|

|

|

|

|

|

|

|

|

v2 |

|

- |

|

|

|

|

|

|

|

|

|

|

|

|

|

- v1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

v2 |

|

- |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

i2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

i2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VC |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Assume the MOSFET's are in the non-saturation region |

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

i |

|

|

|

|

|

|

|

|

- v |

|

-V |

|

|

)(v |

|

|

|

- v |

|

|

|

|

1 |

|

(v |

|

|

|

|

- v |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

1 |

= β (V |

C |

2 |

T |

1 |

|

2 |

) - |

2 |

|

1 |

|

2 |

)2 |

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

i |

|

|

|

|

|

|

|

|

- v |

|

-V |

|

|

)(-v |

|

|

- v |

|

|

) - |

1 |

|

(-v |

|

- v |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

2 |

= β (V |

C |

2 |

T |

1 |

2 |

2 |

1 |

2 |

)2 |

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

Rewrite as |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

i |

|

|

|

|

|

|

|

|

- v |

|

-V |

|

|

)(v |

|

|

|

- v |

|

|

|

|

1 |

|

(v |

|

|

2 |

- 2v |

|

v |

|

|

+ v |

|

|

|

|||||||||||||||

|

|

|

|

1 |

= β (V |

C |

2 |

T |

1 |

|

2 |

) - |

2 |

|

1 |

1 |

2 |

2 |

2) |

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

i |

|

|

|

|

|

|

|

|

- v |

|

-V |

|

|

)(-v |

|

|

- v |

|

|

) - |

1 |

|

(v |

|

|

|

2 |

+ 2v |

|

v |

|

+ v |

|

|

||||||||||||||||||

|

|

|

|

2 |

= β (V |

C |

2 |

T |

1 |

2 |

2 |

1 |

1 |

2 |

2 |

2) |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

i |

|

- i |

|

|

|

|

|

|

-v |

|

-V |

|

|

)(2v |

|

) - |

1 |

(v |

2-2v |

|

v |

|

|

+v |

|

|

2-v |

|

2-2v |

|

v |

|

-v |

|

|

|||||||||||||||||||||

1 |

2 |

= β (V |

C |

2 |

T |

1 |

2 |

1 |

2 |

|

|

|

1 |

2 |

2) |

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

2 |

|

1 |

|

|

|

|

|

|

|

|

|

2 |

|

|

||||||||||||||||||

i1 - i2 = 2β [ (VC - VT)v1 - 2v1v2 + 2v1v2 ] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

v1-(-v1) 2v1 |

|

|

|

|

|

|

2v1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

2R = |

i1-i2 |

|

= i1-i2 = 2β(VC-VT)v1 = β(VC-VT) |

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

or |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R = |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

≤ V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2K L |

(VC-VT) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

v |

1 |

C |

|

- V |

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Allen and Holberg - CMOS Analog Circuit Design |

Page V.2-8 |

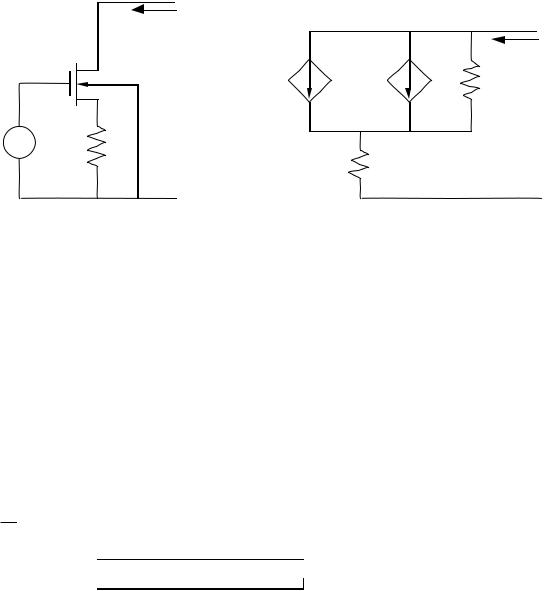

Single-MOSFET, Differential Resistor Realization

i1 |

r ac/2 |

v1 |

v2 |

|

r ac/2 |

- v1 |

v2 |

i2 |

R |

Voltage-Current Characteristics

1.0mA

0.6mA

0.2mA

ID(M1)

-0.2mA

-0.6mA

-1.0mA

VC i1

VC i1

v1

v2

v2

VCC

VCC

- v1

v2 i2

v2 i2

VC

VC

VC= 7V

6V

6V

5V

5V

4V

4V

3V

3V

-2 |

-1 |

0 |

1 |

2 |

V1

Single MOSFET Differential Resistor Realization M1 1 2 3 4 MNMOS1 W=15U L=3U

M2 5 2 3 4 MNMOS1 W=15U L=3U VC 2 0

VCC 4 0 DC -5V V1 1 0

E1 5 0 1 0 -1

.MODEL MNMOS1 NMOS VTO=0.75 KP=25U +LAMBDA=0.01 GAMMA=0.8 PHI=0.6

.DC V1 -2.0 2.0 0.2 VC 3 7 1

.PRINT DC ID(M1)

.PROBE

.END

Allen and Holberg - CMOS Analog Circuit Design Page V.2-9

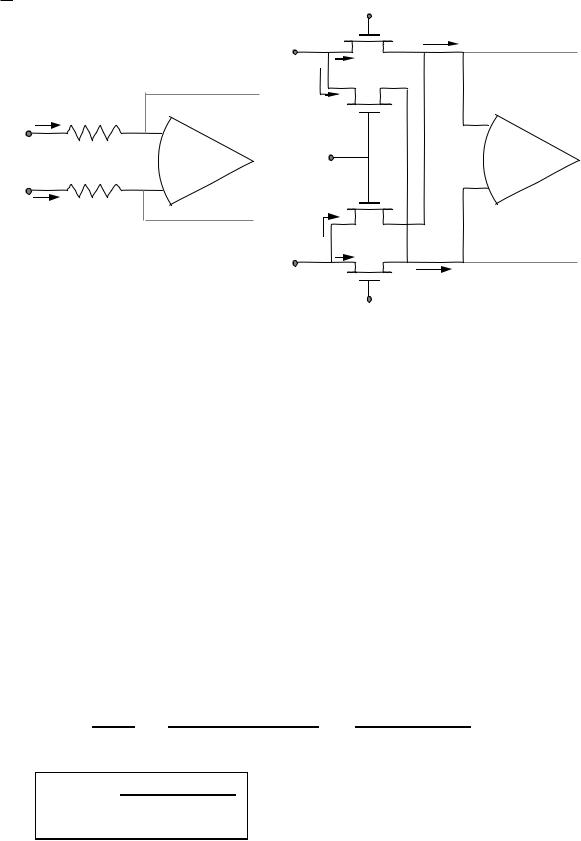

The Double MOSFET Differential Resistor

|

|

|

|

|

|

|

|

|

|

|

|

|

VC1 |

i1 |

|

|

|

|

|

|

|

|

|

|

v1 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

iD1 |

|

|

|

|

|

|

|

|

|

|

|

|

iD2 |

|

||

i1 |

|

R |

v |

+ |

|

|

|

|

|

|

|

|

v |

|

v1 |

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

VC2 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

v2 |

|

|

|

|

- |

|

|

|

|

|

|

|

|

- |

|

|

v |

|

|

|

|

|

|

|

|

|

v |

||

i2 |

|

R |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

iD3 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

v2 |

|

iD4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

VC1 |

i2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

i |

|

|

|

|

-v-V |

|

)(v |

|

-v) - |

1 |

(v |

|

|

|

D1 |

= β (V |

C1 |

T |

1 |

2 |

1 |

-v)2 |

|

||||||

|

|

|

|

|

|

|

|

|

||||||

i |

|

|

|

|

-v-V |

|

)(v |

|

-v) - |

1 |

(v |

|

|

|

D2 |

= β (V |

C2 |

T |

1 |

2 |

1 |

-v)2 |

|

||||||

|

|

|

|

|

|

|

|

|

||||||

i |

|

|

|

|

-v-V |

|

)(v |

|

-v) - |

1 |

(v |

|

|

|

D3 |

= β (V |

C1 |

T |

2 |

2 |

2 |

-v)2 |

|

||||||

|

|

|

|

|

|

|

|

|

||||||

i |

|

|

|

|

-v-V |

|

)(v |

|

-v) - |

1 |

(v |

|

|

|

D4 |

= β (V |

C2 |

T |

2 |

2 |

2 |

-v)2 |

|

||||||

|

|

|

|

|

|

|

|

|

||||||

i |

|

=i |

|

+i |

|

|

|

-v-V |

|

)(v |

|

-v)- |

1 |

(v |

|

-v)2+(V |

|

-v-V |

|

)(v |

|

-v)- |

1 |

(v |

|

|

|

|

||

1 |

D1 |

D3 |

=β (V |

C1 |

T |

1 |

2 |

1 |

C2 |

T |

2 |

2 |

2 |

-v)2 |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

i |

|

=i |

|

+i |

|

|

|

-v-V |

|

)(v |

|

-v)- |

1 |

(v |

|

-v)2+(V |

|

-v-V |

|

)(v |

|

-V)- |

1 |

(v |

|

|

|

|||

2 |

D2 |

D4 |

=β (V |

C2 |

T |

1 |

2 |

1 |

C1 |

T |

2 |

2 |

2 |

-v)2 |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

i1 |

- i2 = |

β[(VC1-v-VT)(v1-v) + (VC2-v-VT)(v2-v) |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

-(VC2-v-VT)(v1- v) - (VC1-v-VT)(v2-v)]

=β[v1(VC1-VC2) + v2(VC2-VC1)] = β(VC1-VC2)(v1-v2)

Rin = |

v1-v2 |

|

v1-v2 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

||

|

= |

β(VC1-VC2)(v1-v2) |

|

= |

KW |

|

|

|

|

|

|

|

|

|

||||

|

|

i1-i2 |

|

|

|

(VC1-VC2) |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

|||||

or R |

|

= |

|

|

1 |

,v |

|

≤ min [(V |

|

-V |

|

),(V |

|

-V |

|

)] |

||

i n |

KW |

|

v |

2 |

C1 |

T |

C2 |

T |

||||||||||

|

|

|

1 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

L |

(VC1-VC2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Allen and Holberg - CMOS Analog Circuit Design |

Page V.2-10 |

Double-MOSFET, Differential Resistor Realization

VC1

iD1 |

M1 |

i1 |

v1 |

|

v3 |

i

v1

v2

i

1 |

r ac/2 |

iD2 |

VSS |

v3 |

|

||

|

|

M2 |

|

|

r ac/2 |

VC2 |

|

|

|

v4 |

|

2 |

R |

iD3 |

M3 |

|

|

iD4 |

VSS |

|

v2 |

|

v4 |

|

M4 |

i2 |

VC1

Voltage-Current Characteristics

150uA |

|

|

|

100uA |

VBC |

=-5V |

|

|

|

||

|

|

V3 =0V |

|

50uA |

VC1 =7V |

||

|

|

||

I(VSENSE) |

0 |

|

|

|

|

|

|

- 50uA |

|

|

|

-100uA

-150uA

VC2 = 6V

5V

5V

4V

4V

3V

3V

2V

2V

Double MOSFET Differential Resistor Realization M1 1 2 3 4 MNMOS1 W=3U L=3U

M2 1 5 8 4 MNMOS1 W=3U L=3U

M3 6 5 3 4 MNMOS1 W=3U L=3U

M4 6 2 8 4 MNMOS1 W=3U L=3U VSENSE 3 8 DC 0

VC1 2 0 DC 7V VC2 5 0

VSS 4 0 DC -5V V12 1 6

.MODEL MNMOS1 NMOS VTO=0.75 KP=25U +LAMBDA=0.01 GAMMA=0.8 PHI=0.6

.DC V12 -3 3 0.2 VC2 2 6 1

.PRINT DC I(VSENSE))

.PROBE

.END

-3 |

-2 |

-1 |

0 |

1 |

2 |

3 |

V1-V2

Allen and Holberg - CMOS Analog Circuit Design |

Page V.2-11 |

SUMMARY OF ACTIVE RESISTOR REALIZATIONS

AC Resistance

Realization

Single MOSFET

Parallel MOSFET

Single-MOSFET, differential resistor

Double-MOSFET, differential resistor

Linearity |

How |

Restrictions |

|

Controlled |

|||

|

|

||

|

|

|

|

Poor |

VGS or W/L |

vBULK < Min (vS, vD) |

|

|

|

|

|

Good |

VC or W/L |

v ≤ (VC - VT) |

|

|

|

|

|

Good |

VC or W/L |

|v1| < VC - VT |

|

vBULK < -v1 |

|||

|

|

Differential around v1 |

|

|

VC1 - VC2 or |

v1, v2 < min(VC1-VT, |

|

Very Good |

VC2-VT) |

||

|

W/L |

vBULK < min(v1,v2) |

|

|

|

Transresistance only |

|

|

|

|

Allen and Holberg - CMOS Analog Circuit Design |

Page V.3-1 |

V.3 - CURRENT SINKS & SOURCES

CHARACTERIZATION OF SOURCES & SINKS

1). Minimum voltage (vMIN) across sink or source for which the current is no longer constant.

2). Output resistance which is a measure of the "flatness" of the current sink or source.

CMOS Current Sinks & Sources

VDD

iD +

+

v

VGG  -

-

VDD

VGG

iD

+ v

-

-

1 rOUT = λID

iD |

VG = VGG |

vMIN

vMIN

v

0

iD |

VG = VGG |

|

0 |

|

vMIN |

|

v |

|

|

|

|

|

0 |

VDD |

|

|

vMIN = vDS(SAT.) = vON |

where vON = vGS - VT |

Allen and Holberg - CMOS Analog Circuit Design |

|

|

|

|

Page V.3-2 |

||||

SMALL SIGNAL MODEL FOR THE MOSFET |

|

|

|

||||||

|

|

D |

G |

B |

|

|

|

|

D |

|

|

+ |

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

G |

B |

vgs |

vbs |

g v |

g |

v |

r |

ds |

|

|

|

m gs |

mbs bs |

|

||||

|

|

|

- |

- |

|

|

|

|

|

|

|

S |

S |

|

|

|

|

|

S |

gm = |

|

2K'WID |

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

gmbs |

= |

gmγ |

|

|

|

|

|

|

|

2φF + |VBS | |

|

|

|

|

|

|

|

||

|

2 |

|

|

|

|

|

|

|

|

rds ≈ |

1 |

= 1 |

|

|

|

|

|

|

|

|

gds |

λID |

|

|

|

|

|

|

|

Allen and Holberg - CMOS Analog Circuit Design |

Page V.3-3 |

INCREASING THE ROUT OF A CURRENT SOURCE

MOS

|

Circuit |

Small-Signal Model |

|

||

|

|

+ |

|

|

|

|

|

iOUT |

|

|

+ |

|

M2 |

|

|

iout |

|

|

|

|

|

r ds2 |

|

|

|

gm2vgs2 |

|

|

vout |

+ |

|

vOUT |

gmbs2vbs2 |

||

r |

|

+ |

|

|

|

- |

|

r |

|

||

|

VGG |

- |

vS2 |

- |

|

|

|

- |

|

|

|

Loop equation: |

|

|

|

||

|

vout = |

[iout - (gm2vgs2 + gmbs2vbs2)]rds2 + iout r |

|

||

But, vgs2 = -vs2 and vbs2 = - vs2. |

|

|

|

||

|

vout = [iout + gm2vs2 + gmbs2vs2]rds2 + iout r |

|

|||

Replace vs2 by ioutr- |

|

|

|

||

|

vout = |

iout [ rds2 + gm2rds2r + gmbs2rds2r + r ] |

|

||

Therefore,

rout = rds2 + r [1 + gm2rds2 + gmbs2rds2]

MOS Small Signal Simplifications

Normally,

gm ≈ 10gmbs ≈ 100gd s

gm ≈ 10gmbs ≈ 100gd s

Continuing

rout rgm2rds2

rout ≈ r x (voltage gain of M2 from source to drain)