- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

Триггер с динамическим управлением записью. Временная диаграмма.

Отличительной чертой триггеров с динамическим управлением записью является то, что информация в триггер поступает только в момент изменения сигнала на входе С или из 0 в 1 или из 1 в 0. В первом случае триггер имеет прямой динамический вход С, а во втором - инверсный динамический вход С.

Рассмотрим более подробно принцип действия синхронного триггера с динамическим управлением записью на примере RS-триггера (см. рис.).

Синхронный

![]() -триггер

с прямым динамическим управлением

записью

-триггер

с прямым динамическим управлением

записью

Временная диаграмма его работы приведена на рис. 3.13. Будем говорить, элемент ИНЕ закрыт, если хотя бы на одном из его входов находится сигнал 0 и открыт, если на всех его входах находится сигнал 1. В первом случае на выходе элемента будет сигнал 1, а во втором - сигнал 0.

Временная диаграмма работы D-триггера

Rs-триггер: функции, таблица и матрица переходов.

Синхронный RS-триггер со статическим управлением записью реализуется подключением двух элементов И-НЕ к ЗЯ. Смена сигналов на логических входах R и S разрешена между СИ.

Синхронный RS-триггер со статическим управлением записью, его условное графическое обозначение и таблица переходов (рис. ниже), где Q(t) - хранение предыдущего состояния.

Функция триггера – хранение информации.

|

Матрица переходов | ||

|

Q(t)=>Q(t) |

S |

R |

|

0-0 |

0 |

X |

|

0-1 |

1 |

0 |

|

1-0 |

0 |

1 |

|

1-1 |

X |

0 |

Таблица и матрица переходов: RS – триггер на эл-тах И-НЕ:

|

__ S |

__ R |

Q(t+1) |

|

Q(t) |

Q(t+1) |

__ S |

__ R |

|

0 |

0 |

Х |

|

0 |

0 |

1 |

Х |

|

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

Q(t) |

|

1 |

1 |

Х |

1 |

Временная

диаграмма работы синхронного RS-триггера

со статическим управлением записью

Временная

диаграмма работы синхронного RS-триггера

со статическим управлением записью

Схема синхронного RS-триггера

с дополнительными инверсными асинхронными

входами![]() и

и![]() (входами предварительной установки

триггера в 0 или 1) на элементах 2-2И-2ИЛИ-НЕ

показана на рис. ниже.

(входами предварительной установки

триггера в 0 или 1) на элементах 2-2И-2ИЛИ-НЕ

показана на рис. ниже.

Синхронный

RS-триггер

со статическим управлением записью и

асинхронными входами

![]() и

и

![]() и его условное графическое обозначение

и его условное графическое обозначение

Принцип

действия синхронного

RS-триггера

с динамическим управлением записью.

Синхронный

![]() -триггер

с прямым динамическим управлением

записью

-триггер

с прямым динамическим управлением

записью

Временная диаграмма его работы приведена на рис. выше. Будем говорить, элемент ИНЕ закрыт, если хотя бы на одном из его входов находится сигнал 0 и открыт, если на всех его входах находится сигнал 1. В первом случае на выходе элемента будет сигнал 1, а во втором - сигнал 0.

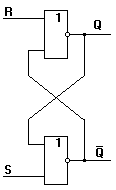

АСИНХРОННЫЙ RS - ТРИГГЕР

Асинхронный триггер имеет два входа S(et) - установка и R(eset) - сброс и два выхода прямой - Q и инверсный - ~Q. Триггер переходит из текущего состояния X на выходе к состоянию 0, при подаче на вход S нуля и на вход R единицы, а при поступлении на вход S единицы и на вход R нуля триггер переходит к состоянию 1. При нулевых значениях, когда S=R=0 триггер должен сохранять старое значение. Комбинация сигналов S=R=1 не определена. В соответствии с описанием составим таблицу состояний триггера (см. ниже).

Схема:

УГО:

Таблица переходов

|

S |

R |

Q(t+1) |

Название режима |

|

0 |

0 |

Q(t) |

Хранение инф-ии |

|

0 |

1 |

0 |

сброс |

|

1 |

0 |

1 |

Установка в 1 |

|

1 |

1 |

- |

Не определено |