- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

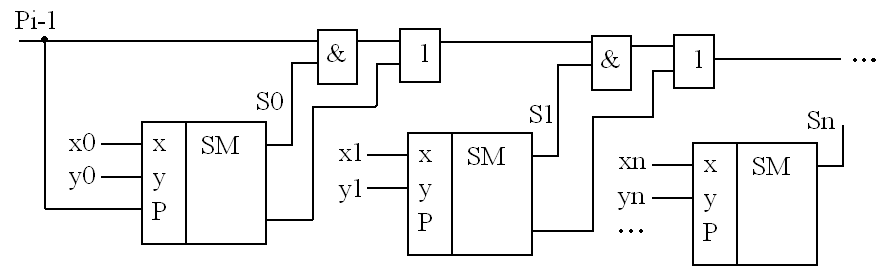

Многоразрядные сумматоры. Комбинационный сумматор.

Сумматор с параллельным переносом

Имеет смысл, если небольшая разрядность.

Параллельный комбинационный сумматор с последовательностным переносом

Преимущества: быстрый. Недостатки: не хранит результаты.

Многоразрядные сумматоры. Организация ускоренного переноса.

Рассказать о сумматоре:

Сумматор в центре вычислительной части большинства устройств (в интегральных микросхемах; накапливающие сумматоры - для формирования адреса ОЗУ);

для работы цифровых устройств важны его технические характеристики;

1+1=0, сдвиг;

Указать общие формулы для суммы и переноса.

Одним из важнейшими параметров сумматоров являются разрядность.

Три способа переноса:

Сквозной

Условный

Групповой

Сумматор со сквозным переносом

![]()

![]()

![]()

![]() - транзит переноса

- транзит переноса

tn = (n-1)(tзИ + tзИЛИ)

Перенос:

в текущем разряде (порождаемый)

из предыдущих разрядов

(транзитный)

(транзитный)

Схемы с групповым переносом

- разбиение многоразрядных чисел на группы (на основе статистического анализа), внутри группы – параллельный перенос, между группами – последовательный перенос.

Сумматор с условным переносом:

Переполнения:

00. 01. Положит.

11. 10. Отрицат.

a0

b0

s0

Зн. a

Зн. b

Зн. S

0

0

1

1

1

0

Перен. Знак + перенос старшего

Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

Память – устройство, предназначенное для хранения массива данных в двоичном виде. Или: память – способность сохранять данные во времени.

Время:

Физическое (из прошлого в будущее) непрерывно, используется при переходных процессах.

Абстракция – квантовое время – привязанное к некоторым события. Обеспечивается службой синхронизации. Порождается тактовым генератором.

По функциям любые ЗУ обязаны выполнять следующие операции:

Запись

Хранение

Считывание

В составе ЗУ обязательно должен быть механизм указания на местоположение обрабатываемой информации, называемый механизмом адресации (механизм выборки). В зависимости от порядка доступа к информации различают: адресные, безадресные, ассоциативные ЗУ.

Признаки – физические характеристики среды хранения информации. Изучаем только полупроводниковые ЗУ с произвольной выборкой (RAM) – используется в качестве оперативной.

Схема с памятью – это схема, в которой выходные сигналы определяются не только совокупностью входных сигналов, но и совокупностью состояний элементов памяти. Элемент памяти – элемент, для которого можно понять состояние, которое выражается как 1 или 0 и обладающего способностью сохранить это состояние в памяти при отсутствии входных воздействий.

Примерами схем с памятью являются всевозможные последовательные и параллельные регистры, счетчики и др.

Физическое время течет непрерывно и обычно используется в схемотехнике для измерения времени перехода элементов из одного состояния к другому.

Квантование времени – связывание некоторых событий в физическом времени с определенными дискретными значениями. Последовательная совокупность этих дискретных значений описывает дискретное время.

Тактовый генератор управляет последовательным переходом от одного момента дискретного времени к другому, с помощью сигналов.

Тактовый генератор производит импульсы:

![]()