- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

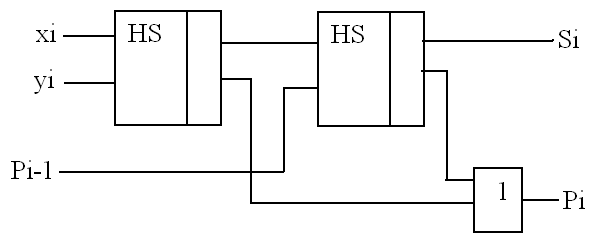

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

Микросхемы сумматоров (английское Adder), как следует из их названия, предназначены для суммирования двух входных двоичных кодов, то есть выходной код будет равен арифметической сумме двух входных кодов.

Построение полного сумматора из полусумматора

![]()

Комбинационный сумматор - это некоторое логическое устройство, обеспечивающее получение сигналов суммы и переноса при одновременной подаче кодов исходных слов.

Если говорить о сумматоре комбинационного типа: у нас имеется некоторая схема КС.

На её входы одновременно приходят данные: первый операнд X и второй операнд Y.

Отличительная особенность комбинационной схемы сумматора - одновременная подача первого и второго слагаемых.

Полный комбинационный сумматор

УГО:

![]()

![]()

S = 1 слагаемое + 2 слагаемое + перенос из предыдущего разряда

Таблица истинности:

|

|

xi |

yi |

|

si |

Pi |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

2 |

0 |

1 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

0 |

1 |

|

4 |

1 |

0 |

0 |

1 |

0 |

|

5 |

1 |

0 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

0 |

1 |

|

7 |

1 |

1 |

1 |

1 |

1 |

![]()

Полный комбинационный сумматор:

Сумматоры. Одноразрядный последовательностный сумматор.

Последовательностные схемы – логические схемы с запоминанием переменных (элементы с памятью) - схемы, выходные сигналы к-рых зависят не только от значения входных сигналов в данный момент времени, но и от последовательности значений входных сигналов в предшествующие моменты времени. Последовательностные схемы собираются из комбинационных путём введения в них обратных связей.

Микросхемы сумматоров (английское Adder), как следует из их названия, предназначены для суммирования двух входных двоичных кодов, то есть выходной код будет равен арифметической сумме двух входных кодов.

Сумма двух двоичных чисел с числом разрядов N может иметь число разрядов (N + 1). Этот дополнительный (старший) разряд называется выходом переноса.

Сумматоры

![]()

![]()

xi – первое слагаемое yi – второе слагаемое Pi-1 – перенос и предыдущего разряда

Si – разряд сумм q – основание системы счисления Pi – перенос в следующий разряд

Сложение и сдвиг – 2 операции, которыми можно заменить все остальные.

Сумматор на схеме с памятью:

Одноразрядный сумматор накапливающего типа (последовательностный сумматор):

Это сумматор с аккумулированием результата

Временная диаграмма:

Многоразрядные сумматоры. Накапливающий сумматор.

Если говорить о сумматоре накапливающего типа, передача слагаемых на вход происходит последовательно (а не одновременно).

Сумматор накапливающего типа - это схема с памятью. Сначала задаётся в какой-то момент времени t1 первое слагаемое X; оно запоминается в памяти сумматора. Затем, в момент времени t2 подаётся второе слагаемое Y. Через некоторое время t-задержки на выходе сумматора возникает S и сигнал переноса P.

В обычном сумматоре накапливающего типа используются триггерные схемы.

Кстати говоря, из сумматора комбинационного очень легко получается сумматор накапливающего типа: если выход сумматора комбинационного типа нагрузить на какой-нибудь регистр.

Вначале происходит обнуление этого регистра. Тогда вы можете в первый момент времени подать первое слагаемое и запомнить результат в регистре хранения. А затем, в момент времени t2 за счёт обратной связи, на второй вход комбинационного сумматора подаётся предыдущее слагаемое.

Такая комбинация - регистра хранения и комбинационного сумматора – позволяет реализовать сумматор накапливающего типа.

Схема многоразрядного последовательного сумматора:

Последовательные сумматоры преобразуют последовательные коды слагаемых в последовательный код суммы этих слагаемых. Сложение начинается с младшего разряда и выполняется поразрядно последовательно за столько тактов, сколько разрядов содержится в числе. В состав многоразрядного сумматора последовательного действия, кроме комбинационного одноразрядного сумматора, применяют три сдвигающих регистра для двух слагаемых x и y и для результата S, триггер переноса D и схемы управления вводов и выводов чисел.

Два

суммируемых числа загружаются в регистры

x

и y

по последовательным и параллельным

входам. Триггер переноса первоначально

установлен в 0, следовательно C=0.

сигнал суммы записывается в регистр

сдвига S.

Каждый сигнал переноса, вырабатываемый

сумматором, появляется на выходе P

и запоминается триггером переноса.

Тактовый импульс вводит бит суммы в

регистр S

и одновременно сдвигает на один разряд

регистры x

и y.

Кроме того, он вносит значение переноса

P

и D,

в результате чего на входе С

всегда действует значение разряда

переноса, имевшее место при сложении

двух предыдущих разрядов. Так суммируются

все разряды двоичных чисел и результат

записывается в регистр S.

Этот результат можно считать по

параллельным или последовательным

выходам. Основное достоинство такого

сумматора – малое количество оборудования;

к недостаткам относится малое

быстродействие, т.к. время суммирования

двух n-разрядных

чисел

![]() ,

где T

–

период следования тактовых импульсов.

,

где T

–

период следования тактовых импульсов.

Накапливающий сумматор:

Требования:

Хранение

Парал. прием

CLR-вход