- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

Комбинационные схемы — такие схемы, в которых значения сигналов на выходе определяется только входными переменными. Схемы такого рода, обычно, не имеют обратных связей. Памяти в таких схемах нет.

Полный

мультиплексор

Полный

мультиплексор

Сокращенный мультиплексор – когда информационных входов меньше, чем 2n.

Мультиплексор - коммутирующий элемент, который передает сигнал с одного из многих информационных входов на один единственный информационных выход под управлением селекторных (адресных, выбирающих) входов.

Логика работы - много в один.

Применение: коммутация, мультиплексирование.

Построим маленький мультиплексор:

![]() .

Если A0=0, то D0, если A0=1,

то D1

.

Если A0=0, то D0, если A0=1,

то D1

Дополнение: Входы разрешения работы позволяют управлять устройством.

![]()

Логическая схема 4-х разрядного мультиплексора:

С использованием дешифратора:

Мультиплексор является базисом, причем он не требует дополнительных элементов.

Предположим, есть мультиплексор с n-адресными входами.

n - кол-во переменных, от которых зависит ф-я. 2n - кол-во входных наборов.

С входным программируемым набором (хранится в памяти). Функция меняется:

|

|

a b c |

F(abc) |

|

0 |

0 0 0 |

1 |

|

1 |

0 0 1 |

0 |

|

2 |

0 1 0 |

1 |

|

3 |

0 1 1 |

0 |

|

4 |

1 0 0 |

1 |

|

5 |

1 0 1 |

1 |

|

6 |

1 1 0 |

1 |

|

7 |

1 1 1 |

0 |

Основные свойства:

1. Коммутация.

2. Реализуется простейшими наборами элементов (И, ИЛИ).

3. Базис – позволяет реализовать любую логическую функцию от n перемных = колучеству адресных входов).

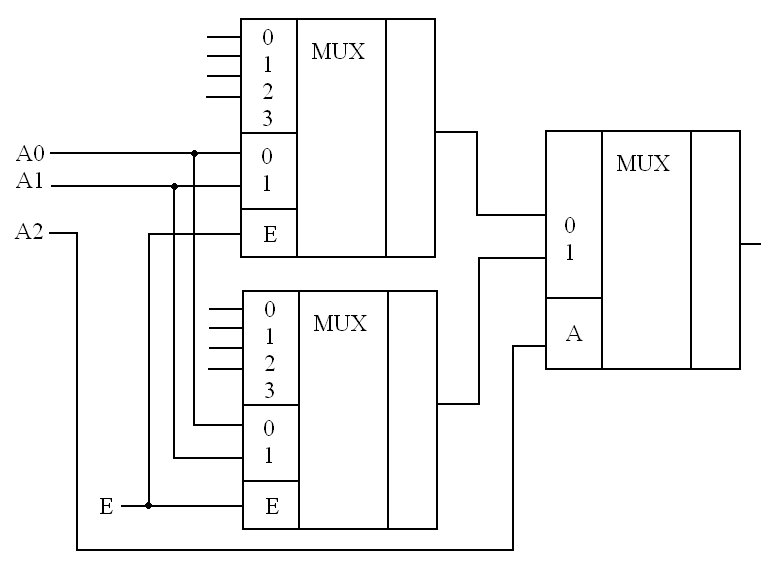

Увеличение разрядности мультиплексора

Используется каскадирование и основан он на использовании входа разрешения E

Пирамидальное каскадирование. С использованием только мультиплексора.

Демультиплексор - схема дешифратора, при организации "из одного в многое". Демультиплексирование – обеспечение коммутации из одного входа в несколько.

Входы дешифратора несут нагрузку информационную - т.е. адрес передачи. В демультиплексоре: входы - адресы входов.

Задача демультиплексирования сводится к обеспечению коммутации "один-ко-многим". Решается с помощью дешифратора с входом E.

Ai E

1 E = E – будет передано на тот выход, на котором единица

Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

Микросхемы сумматоров (английское Adder), как следует из их названия, предназначены для суммирования двух входных двоичных кодов, то есть выходной код будет равен арифметической сумме двух входных кодов.

Сумма двух двоичных чисел с числом разрядов N может иметь число разрядов (N + 1). Этот дополнительный (старший) разряд называется выходом переноса.

Помимо выходных разрядов суммы и выхода переноса, сумматоры имеют вход расширения (другое название - вход переноса) С для объединения нескольких сумматоров с целью увеличения разрядности. Если на этот вход приходит единица, то выходная сумма увеличивается на единицу, если же приходит нуль, то выходная сумма не увеличивается. Если используется одна микросхема сумматора, то на ее вход расширения С необходимо подать нуль.

Сумматоры

![]()

![]()

xi – первое слагаемое

yi – второе слагаемое

Pi-1 – перенос и предыдущего разряда

Si – разряд сумм

q – основание системы счисления

Pi – перенос в следующий разряд

Сложение и сдвиг – 2 операции, которыми можно заменить все остальные.

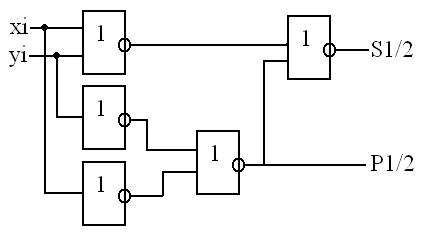

Полусумматорами называют устройства с двумя входами и двумя выходами, на которых вырабатываются сигналы суммы и переноса согласно формулам (см. формулы ниже для 3 случаев).

Сложение по модулю 2. Таблица истинности.

|

X |

Y |

S(x,y) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Одноразрядный комбинационный полусумматор

УГО полусумматора:

Схема 1:

![]()

![]()

Нет обработки предыдущего переноса.

Схема 2:

![]()

Схема 3:

Реализация на элементе «стрелка Пирса».

Параметры:

однозначность элементов

простота реализации

быстродействие

тепловыделение