- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

Природа большинства физических величин такова, что они могут принимать любые значения в каком-то диапазоне (температура, давление, скорость и т.д.) – аналоговые сигналы (непрерывные). Существуют также дискретные сообщения, параметры которых содержат фиксированный набор отдельных значений.

Технологически проще обрабатывать информацию в виде электрических сигналов.

Основные способы представления двоичных цифр:

Потенциальный

Разность потенциалов относительно уровня земли (0), 1 – положительная величина, больше заданного граничного значения. Уменьшив диапазон между двумя уровнями напряжения можно:

увеличить быстродействие

уменьшить потребление энергии

уменьшить выделение тепла

Запас помехоустойчивости - определяется как разница между входным и выходным уровнями логического нуля или логической единицы.

Задаются два уровня напряжения. Тут возможны различные подходы. Например, высокому уровню мы можем сопоставить значение "1", а низкому уровню - значение "0". Это будет так называемая положительная логика. Но можно сделать и наоборот. Можно сопоставить низкому уровню напряжения "1", а высокому "0". Это отрицательная логика. Поэтому соотносить "1" и "0" как числа - невозможно; это не числа - это символы алфавита. Возьмём два разных тактовых импульса - в один момент была "1", в другой "0"; а если мы возьмём какой-то промежуточный момент времени, то здесь получился бы уровень напряжения, который находится между уровнем "1" и уровнем "0". С точки зрения двоичной логики - это полная неопределённость. Поэтому при представлении информации в потенциальном виде, всегда нужно задавать коридор напряжений - нижний и верхний уровень напряжения, соответствующий символу "1" и символу "0". А все остальные уровни напряжения, которые выходят за рамки этого коридора, они считаются недопустимыми при использовании двоичного алфавита.

Импульсный

Импульс – переход из одного состояния в другое и обратно.

В тактовый момент времени возникает кратковременный импульс - либо импульс тока, либо импульс напряжения. Если в определённые моменты времени (такты) регистрируется импульс - это соответствует сигналу "1"; если импульса нет - это соответствует "0". Такое представление информации соответствует биполярному представлению импульсов - импульсы либо положительной полярности, либо вовсе отсутствуют.

Возможно ещё представление информации в импульсном виде с использованием двухполярных импульсов (импульсов различных полярности): импульс отрицательной полярности соответствует "0", положительной полярности - единице. Это импульсное представление информации при использовании двухполярных импульсов.

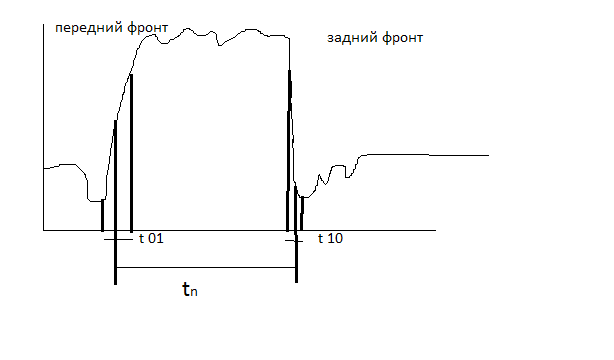

T 01 – время перехода из 0 в 1

T 10 – время перехода из 1 в 0

T n- время импульса

Декремент затухания - количественная характеристика быстроты затухания колебаний.

Модель логического элемента

Логический эл-т = функция + tзадержки

F(x0,…,xn) – относится к классу функций алгебры логики (переключательная функция, булева функция).

Технические характеристики:

Напряжение входное и выходное - определяется от 0 до 1.

Входные и выходные токи - определяют нагрузочные способности этого элемента через коэффициент объединения по входу (сколько элементов можно подключить) и коэффициент разветвления для выходов (сколько логических элементов можно подключить к выходу).

Запас помехоустойчивости – разность между потенциалом, определяющим логический сигнал (0/1) и реальным моментом переключения элемента.

Потребляемая мощность элемента (Вт).

Временные параметры (Т01 и Т10).

УГО элементов ГОСТ:

И

И

ИЛИ

ИЛИ

НЕ

НЕ

И-НЕ

(штрих Шеффера

И-НЕ

(штрих Шеффера

ИЛИ-НЕ

(Стрелка Пирса)

ИЛИ-НЕ

(Стрелка Пирса)

Искл

ИЛИ (XOR)

Искл

ИЛИ (XOR)

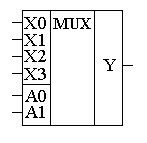

Мультиплексор

Мультиплексор

Дешифратор

Дешифратор

УГО элементов ISO:

And: Or: Not:

Примеры элементов, используемых в Xilinx:

И

с тремя входами, два из которых инверсные

И

с тремя входами, два из которых инверсные

ИЛИ

с двумя входами, один из которых инверсный

ИЛИ

с двумя входами, один из которых инверсный

И-НЕ

с двумя входами, один из которых инверсный

И-НЕ

с двумя входами, один из которых инверсный

ИЛИ-НЕ

ИЛИ-НЕ

2-2И-2ИЛИ

(SOP4)

2-2И-2ИЛИ

(SOP4)

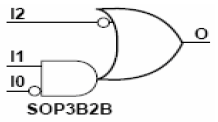

1-2И-2ИЛИ

(SOP3)

1-2И-2ИЛИ

(SOP3)