- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

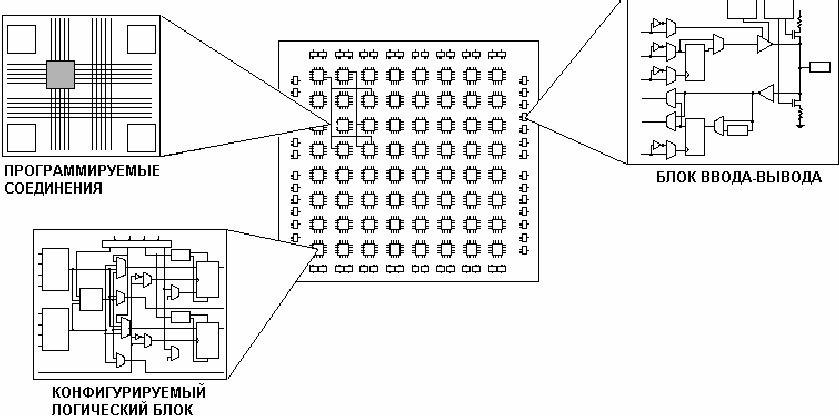

Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

В наиболее типичном варианте ПЛИС, выполненная по технологии FPGA, состоит из прямоугольной матрицы конфигурируемых логических блоков (Configurable Logic Blocks, CLB), окруженной блоками ввода-вывода (Input/Output Block, IOB). Между CLB располагаются программируемые трассировочные линии.

Между матрицей CLB и блоками ввода-вывода имеются отдельные межсоединения, которые и обеспечивают подключение внешних

сигналов.

Основным элементом ПЛИС FPGA фирмы Xilinx является кон-

фигурируемый логический блок (CLB)

В состав CLB входят:

• три таблицы преобразования LUT (Look-Up Table), которые используются как генераторы логических функций;

• два триггера;

• две группы А и В программируемых мультиплексоров, играющих роль средств конфигурирования CLB.

Блоки ввода/вывода (БВВ) обеспечивают интерфейс между выводамикорпуса ПЛИС FPGA и ее внутренними логическими схемами. Каждому выводу корпуса придается блок ввода/вывода БВВ, который может быть конфигурирован как вход, выход или двунаправленный вывод.

Логические блоки в ПЛИС FPGA окружены системой каналов, которые состоят из совокупности металлических сегментов («проводов»), соединяемых друг с другом программируемым элементом связи (ключом). Трассировочные каналы вокруг CLB состоят из трех типов соединительных проводов: одинарной длины, двойной длины и длинные сегменты, пересекающие кристалл по всей его длине или ширине

Линии одинарной длины осуществляют соединения соседних или близлежащих CLB. Линии двойной длины огибают переключательные блоки PSM, соседние по отношению к данному, и проходят к следующим, чем облегчается установление более длинных связей. Три длинные линии, пересекающие весь кристалл по длине

(ширине), предназначены на передачу сигналов на большие расстояния и при большой нагрузке.

Выводы логических блоков (CLB) пересекают горизонтальные и вертикальные каналы трассировки, проходящие непосредственно около них, и могут программируемыми элементами связи (ключами) подключаться к линиям каналов. Дальнейшее направление сигналов в нужные цепи осуществляется матрицей программируемых переключателей

Плис fpga. Назначение и устройство clb.

Интегральные схемы типа FPGA

Рис. 1. Обобщенная структура ПЛИС FPGA

В наиболее типичном варианте ПЛИС, выполненная по технологии FPGA, состоит из прямоугольной матрицы конфигурируемых логических блоков (Configurable Logic Blocks, CLB), окруженной блоками ввода-вывода (Input/Output Block, IOB). Между CLB располагаются программируемые трассировочные линии (рис. 1). Между матрицей CLB и блоками ввода-вывода имеются отдельные межсоединения, которые и обеспечивают подключение внешних сигналов.

Все части FPGA (конфигурируемые логические блоки, система межсоединений и блоки ввода/вывода) являются конфигурируемыми или реконфигурируемыми, причем средствами самих пользователей.

При конфигурировании FPGA логические блоки настраиваются на выполнение необходимых операций преобразования данных, а система межсоединений — на требуемые связи между логическими блоками. В результате во внутренней области FPGA реализуется схема нужной конфигурации. Расположенные по краям кристалла блоки ввода/вывода обеспечивают интерфейс FPGA с внешней средой. Блоки ввода/вывода современных FPGA можно программировать на выполнение требований множества стандартов передачи данных (число таких стандартов может доходить до 20).

Рис. 2. Структура CLB ПЛИС семейства Spartan

Конфигурирование — это процесс загрузки битовой последовательности, полученной с помощью программного обеспечения проектирования, во внутреннюю энергозависимую конфигурационную память кристалла FPGA. При выключении питания конфигурация в ПЛИС FPGA разрушается. Поэтому при включении питания необходим процесс программирования (инициализации, конфигурирования) кристалла FPGA — загрузка данных конфигурации. Для отладки спроектированной схемы используют специальный кабель для загрузки конфигурационных данных. Этот кабель соединяет персональный компьютер с микросхемой FPGA. В конечном устройстве отлаженные данные конфигурации хранятся в ПЗУ, которое непосредственно подключается к ПЛИС FPGA, и после включения питания они автоматически загружаются в ПЛИС. Процесс конфигурирования может производиться неограниченное число раз.

ПЕРЕСТРАИВАЕМЫЙ ЛОГИЧЕСКИЙ БЛОК

Основным элементом ПЛИС FPGA фирмы Xilinx является конфигурируемый логический блок (CLB). На рис. 2 показана упрощенная внутренняя структура логического блока ПЛИС семейства Spartan.

В состав CLB входят:

три таблицы преобразования LUT (Look-Up Table), которые используются как генераторы логических функций;

два триггера;

две группы А и В программируемых мультиплексоров, играющих роль средств конфигурирования CLB.