- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

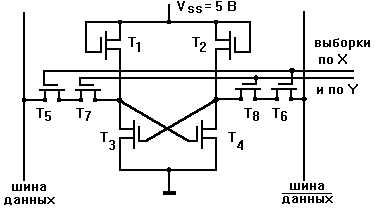

Запоминающая ячейка статического типа, устройство и принцип работы.

ЗЯ статического типа на полевых транзисторах(МОП/MOS)

|

Биполярные транзисторы |

Полевые транзисторы

|

|

2 n-p перехода, управление токами Особенности: большие токи и утечки, плавность переходов

|

Управление потенциалом Особенности:высокая емкость, малые токи утечки

|

Ячейка статического ОЗУ.

Недостатки: Энергопотребление, Термоотдача, Габариты

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до постоянного тока. Кроме того статические ОЗУ применяются для построения КЭШ-памяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ.

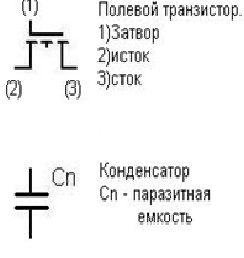

Запоминающая ячейка динамического типа, устройство и принцип работы.

Однотранзисторная ячейка динамического типа

Запоминающая ячейка Динамического типа.

Конденсатора на самом деле нет.

Это паразитная емкость, возникшая из параллельной емкости транзистора.

Полевой транзистор может хранить заряд емкости.

Значение хранится некоторое время и требует периодического восстановления информации - регенерация.

Обычно ячейки памяти динамического типа объединяют динамическую матрицу,

Что при любом обращении ячейки, находящейся в строке, выполняется цикл регенерации для всех ячеек в этой строке.

Реализация фал на микросхеме памяти. Программируемая логика.

Функции алгебры логики можно также реализовать с помощью ячеек памяти. Для этого мы создаем таблицу истинности для нашей функции и записываем ее в память, после чего просто работаем с этим элементом.

Таким образом, получается свойство, что с помощью одной микросхемы можно реализовать 2^n логических схем.

цикл разработки устройств на ПЛИС занимает значительно меньшее время и неизмеримо дешевле (благодаря тому, что изменение принципиальной электрической схемы выполняется путем перепрограммирования одного и того же экземпляра микросхемы)

2 технологии

1 – Программируемые логические матрицы(ПЛМ)

Достоинства: быстродействие

Недостатки:невозможномсть построить полноценное электронное устройство

2 – ПЛИС

Основные этапы проектирования схемы на ПЛИС

1разрабатывается сигнал устр-ва и вводится в среду проектирования

2 выключается операция имплементации

3 программирование. Перенос конфиг. Файла в теневую память.

Программируемые логические интегральные схемы. Основные принципы построения плм.

Микросхемы программируемой логики или ПЛИС (программируемые логические интегральные схемы) — одно из наиболее динамично развивающихся направлений современной цифровой электроники. Привлекательность данной технологии заключается в предоставляемой конечному пользователю возможности быстрого создания цифровых устройств с произвольной внутренней структурой. По сравнению со специализированными цифровыми микросхемами (Application Specific Integral Circuit, ASIC), цикл разработки устройств на ПЛИС занимает значительно меньшее время и неизмеримо дешевле (благодаря тому, что изменение принципиальной электрической схемы выполняется путем перепрограммирования одного и того же экземпляра микросхемы). Таким образом, вместо металлических соединений, реализуемых в процессе производства ASIC, в ПЛИС используются соединения, коммутируемые программируемыми ключами.

Наша картинка

Базовая структура ПЛМ(не наша картинка)

Основой служат 2-х уровневые матрицы эл-тов «И» «ИЛИ».Программируются только связи между этими элементами.

Основные параметры:

Число входов - m

Число термов - l

Число выходов – n

ПЛМ способна реализов. N логич. функцийй от M аргументов, содержащих L функций

Вход.буферы - преобр однофазные вход сигналы в парафазные(прямые и инвернсые), и формируют сигналы необх мощности для питания элементов матр И