- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

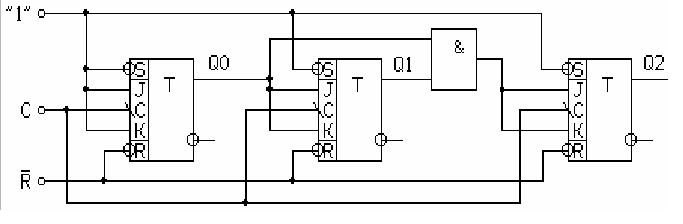

Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

Счетчиком называют последовательностную схему, предназначенную для увеличения / уменьшения хранимого кода на единицу или заданную константу. Счетчик часто имеет цепи предварительной установки заданной величины, в частности нуля. Число разрешенных устойчивых состояний счетчика называют его периодом или модулем М. Сигналы, поступающие на вход счетчика, называют считаемыми. Вход счетчика, на который поступает сигнал, увеличивающий состояние счетчика на 1, обозначают как «+1»; вход, на который поступает сигнал, уменьшающий состояние счетчика на 1, обозначают как «-1». Из любого i-го состояния под воздействием сигнала «+1» счетчик переходит в состояние (i+1)mod M, а под действием сигнала «-1» — в состояние (i-1)mod M.

Если для проектирования синхронных счетчиков существуют отработанные методы, то для проектирования асинхронных счетчиков удобных систематизированных методов нет.

Синхронный двоичный счетчик:

Обобщенная схема логической структуры счетчика:

Сигналы с выходов триггеров поступают на входы комбинационной

схемы, которая преобразует поступившую информацию. Сигналы с выходов комбинационной схемы подаются на логические входы триггеров. Преобразованная информация не воспринимается триггерами до тех пор, пока на синхронизирующие входы триггеров не поступит считаемый сигнал. Информация, находящаяся на входах каждого триггера, так сформирована комбинационной схемой, чтобы с приходом очередного считаемого сигнала осуществить переход счетчика из текущего состояния в следующее. Функции возбуждения входов i-го триггера можно записать в виде:

Значения всех переменных в этих выражениях определены для одного и того же момента времени t. Поэтому функции возбуждения триггеров являются переключательными функциями, которым соответствуют комбинационные схемы, формирующие входные сигналы для триггеров.

Следовательно, если задан тип триггера, то задача синтеза счетчика заключается в составлении функций возбуждения каждого триггера и минимизации найденных функций в заданном базисе.

Далее см. лабораторный практикум с. 98 (проще разобрать JK)

Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

В асинхронном счетчике отсутствует общая шина, на которую поступает считаемый сигнал. На вход С триггеров асинхронного счетчика сигналы могут поступать как с выхода другого триггера, так и от схем, непосредственно не связанных с синхронизирующи ми импульсами

Схема двоичного асинхронного счетчика:

Асинхронные счетчики произвольной разрядности могут быть созданы путем объединения нескольких разрядов следующим образом:

Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом. (Неточно!!)

Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

УГО микросхемы памяти:

Разрядность памяти – разрядность ячейки памяти, т.е. разрядность минимальной адресуемой единицы памяти..

Слово памяти – адресуемая единица.

Количество слов = 2^n входов.

Цикл чтения/записи ПП запоминающего ус-ва.

Память имеет 3 режима работы: запись чтение и хранение.

Цикл записи:

Перестановка нужна чтобы к моменту осущ. Записи все переходные процессы закончились и установилось стабильное значение

Смотри лекции

Цикл чтения:

Мультиплексирование адреса – вместо последовательно передачи эта информация передается последовательно, по частям.

Мультиплексирование адреса в микросхеме памяти.

При мультиплексировании адреса адрес ячейки представляется двумя компонентами: адрес строки и адрес столбца. Для этого внутри микросхемы вводят 2 регистра адреса: регистр адреса строки и столбца.

Для уменьшения числа контактов микросхемы адреса строки и столбца в большинстве микросхем подаются через одни и те же контакты последовательно во времени (мультиплексируются) и запоминаются, соответственно, в регистре адреса строки и регистре адреса столбца микросхемы.

Мультиплексирование обычно реализуется внешней логикой. Для синхронизации процессов фиксации и обработки адресной информации адрес строки (RA) сопровождается сигналом RAS (Row Address Strobe - строб строки), а адрес столбца (СА) - сигналом CAS (Column Address Strobe - строб столбца). Чтобы стробирование было надежным, эти сигналы подаются с задержкой, достаточной для завершения переходных процессов на шине адресаj/I в адресных цепях микросхемы. Сигнал выбора микросхемы CS (Crystal Select) разрешает работу схемы и используется для выбора определенной микросхемы в системах, состоящих из нескольких микросхем. Вход WE (Write Enable - разрешение записи) определяет вид выыполняемой операции (считывание или запись). На все время, пока микросхемы памяти не использует шину данных, информационные выходы микросхемы переводятся в третье (высокоимпедансное) состояние. Управление переключением в третье состояние о6еспечивается сигналом ОЕ (Output Enable - разрешение выдачи выходных сигналов). Этот сигнал активизируется при выполнении операции чтения. На рисунке (см. рисунок ниже) представлено изображение ОЗУ на принципиальных схемах.

Условное изображение ОЗУ