- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

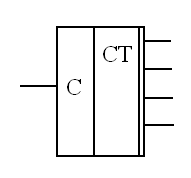

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

Регистры хранения и регистры сдвига. Реверсивный регистр.

1)Хранения — только хранит слов.

2)Сдвиговые — то же + сдвиг вправо/влево. Сдвиг происходит во время синхросигнала.

Регистр сдвига всегда синхронный, тк данный принимаются всегда последовательно.

3)Реверсивные — то же + возможность указать направление сдвига.

см. вопрос 30.

Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

см. вопрос 30.

На логические входы триггеров регистра информация может поступать как с внешних входов, так и по обратной связи с выходов триггеров через комбинационную схему КС1. С ее помощью можно реализовать широкий набор микроопераций (логические и арифметические сдвиги, получение обратного кода и т.п.). Выбор требуемой микрооперации осуществляется с помощью управляющих входов У. Исполнение выбранной микрооперации происходит с поступлением импульса на синхронизирующий вход С при наличии разрешающего сигнала СЕ.

Комбинационная схема КС2 реализует приоритет среди управляющих и установочных входов. Синхронная установка в «0» реализуется подачей импульса на синхровход С при R = 1. При проектировании регистра с требуемым набором микроопераций прежде всего необходимо определить число управляющих входов и задать их приоритет. Число управляющих входов находят по следующей формуле: k = [log2M] + 1, где М — число микроопераций. Далее задача логического проектирования схемы регистра заключается в составлении функций возбуждения каждого триггера. Поскольку структура регистра регулярна, то достаточно получить выражения только для одного триггера.

далее см лабораторный практикум с. 119

Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Выполняют ф-ии счета и делителя частоты.

Счетчиком – называется последовательная схема (схема с памятью), предназначенная для подсчета приходящих на его вход импульсов и отображения результата в каком-либо коде.

Счетчики:

способ пересчета: синхронный, асинхронный

система счисления: двоичные, десятичные, прочие

направление счета: суммирующие, вычитающие, реверсивные

способ переноса: последовательный, параллельный, сквозной

Характеристики

Модуль пересчета – представляет собой кол-во неповторяющихся состояний счетчика

Система кодирования – система счисления, в которой работает счетчик. Самая простая – двоичная. Можно связать разрядность счетчика и его модуль пересчета.

Величиной инкремента/декремента.

Одна из функций счетчика – делитель частоты.

Счетчик зависит только от своего предыдущего состояния.

C – счетный вход

Суммирующие и вычитающие счетчики. Временные параметры.

Двоичный счетчик:

Схема суммирующего синхронного счетчика с параллельным переносом, реализованного на триггерах с управлением фронтом:

Схема вычитающего счетчика: То же самое, только используются инвертированные выходы

Основными временными характеристиками счетчиков являются: - максимальная частота поступления счетных сигналов; - время перехода счетчика из одного состояния в другое.

Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

Реверсивный счетчик:

Реверсивные счётчики - это счётчики, которые могут перестраиваться. Т.е. может работать в режиме суммирующего счётчика, и с помощью некоторых управляющих сигналов переходить в режим вычитающего.

Увеличение количества разрядов в счетчике:

Чтобы получить один восьмиразрядный счётчик, необходимо либо на вход C+, либо на вход C- первого счётчика подавать входные счётные сигналы - в зависимости от направления счёта. Т.е. необходимо реализовать некоторую комбинационную схему, которая будет подавать счётный сигнал на нужный вход в зависимости от выбранного направления счёта.

Входы переполнения/заёма первого счётчика являются непосредственно счётными сигналами для второго счётчика (который реализует старшие разряды - ?).

Выходы Q1, Q2, Q3, Q4 - это выходы младших разрядов полученного числа; а выходы Q5,Q6 Q7, Q8 - выходы старших разрядов.

Выходы >15 и <0 второго счётчика будут соответствовать переполнению нашего общего счётчика или займу - то есть коду >255 - в случае переполнения; или коду <0 - в случае займа.

Как правило, стандартные счётчики имеют дополнительные входы и выходы, которые позволяют нам достаточно гибко их комбинировать - для повышения разрядности этой схемы.

Функция параллельной загрузки

Осуществляет установку каждого триггера счётчика в заданное положение. Реализована за счёт дополнительных входов в схеме счётчика управляющих непосредственно триггерами. При этом каждый из входов воздействует на свой триггер, придавая ему заданное значение. Таким образом, можно присвоить счётчику начальное значение и начать отсчёт от него.