- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

Функция – инвертирование сигнала. Каждая пришедшая на вход 1 изменяет выходное значение.

|

t |

Q(t+1) |

|

0 |

Q(t) |

|

1 |

nQ(t) |

Матрица переходов:

|

T |

Q(t) |

Q(t+1) |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

Временная диаграмма:

Одноступенчатый асинхронный T – триггер.

Одноступенчатый синхронный T – триггер.

Способы снятия ограничения по длительности сигнала:

Использование двухступенчатого триггера

Использование триггеров с динамическим управлением записью.

Двухступенчатый Т-триггер:

D-триггер: функции, таблица переходов.

Функция – задержка.

|

D |

Q(t+1) |

|

0 |

0 |

|

1 |

1 |

На практике наибольшее распространение получила схема синхронного D-триггера со статическим управлением записью.D-триггер имеет один логический входD(Delay- задержка), состояние которого с каждым СИ передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы. СхемуD-триггера можно получить изRS-триггера, если на входRподать инвертированный сигнал входаS.Однако целесообразно использовать для инвертирования уже имеющиеся элементы (рис. ниже).

Синхронный D-триггер со статическим управлением записью (пунктиром показан вход V для DV-триггера):

а) логическая схема; б) условное графическое обозначение D-триггера и его таблица переходов; в) условное графическое обозначение DV-триггера и его таблица переходов

Dv-триггер: функции, таблица и матрица переходов.

Если к D-триггеру добавить еще один входV(Vorentscheidung- предварительное разрешение) для блокирования СИ (пунктирная линия на рис. вопросе 26), то получим синхронныйDV-триггер со статическим управлением записью. Легко заметить, что входы С иVможно поменять местами без нарушения логики работы триггера.

Таблица переходов и матрица состояний DV-триггера:

|

D |

V |

Q(t+1) |

|

Q(t) |

Q(t+1) |

D |

V |

|

0 |

0 |

Q(t) |

|

0 |

0 |

A1 |

____ A1В1 |

|

1 |

0 |

Q(t) |

|

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

|

1 |

1 |

А2 |

А2В2 |

схема см. 26 вопрос

Jk-триггер: функции, таблица и матрица переходов.

Хранение.

В отличие от RS-триггера, JK-триггер не имеет запрещенных комбинаций входных сигналов.

JK – триггер может быть одноступенчатым и двухступенчатым, со статическим и динамическим переключением.

Таблица и матрица переходов:

JK– триггер:

|

J |

K |

Q(t+1) |

|

Q(t) |

Q(t+1) |

J |

K |

|

0 |

0 |

Q(t) |

|

0 |

0 |

0 |

А1 |

|

0 |

1 |

0 |

|

0 |

1 |

1 |

А2 |

|

1 |

0 |

1 |

|

1 |

0 |

А3 |

1 |

|

1 |

1 |

____ Q(t) |

|

1 |

1 |

А4 |

0 |

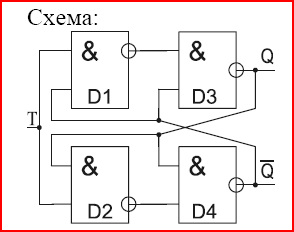

На практике широкое распространение получил синхронный двухступенчатый JK-триггер. Данный триггер имеет два входа J и К. Если J = K = 1, то триггер с приходом синхроимпульса изменяет

свое состояние на противоположное. При остальных значениях входов J и К триггер повторяет таблицу переходов RS-триггера.

Синхронный двухступенчатый RS-триггер, который имеет не- сколько S и R входов, объединенных функцией конъюнкции, легко преобразуется в синхронный JK-триггер. Для этого необходимо

завести обратную связь с выходов триггера на его входы как пока-

зано на рис. 3.8.

Другой пример JK-триггера показан на рис. 3.10. Здесь элемен- ты D5 и D6, отделяющие вторую ступень от первой, управляются не отдельным инвертором, а схемой управления первой ступени (элементы D1 и D2).

Рис. 3.10. Синхронный двухступенчатый JK-триггер с асинхронными входами R и S , его условное графическое обозначение и таблица переходов Если С = 0, то элементы D1 и D2 закрыты и изменения сигналов на входах J и К не влияют на состояние триггера. Передний фронт синхроимпульса (фронт 0/1) переключает в «0» элемент D1 или элемент D2 в зависимости от входных сигналов и состояния триггера второй ступени. Этот нулевой сигнал вначале отсоединяет вторую ступень от первой, а затем устанавливает ЗЯ первой ступени в требуемое состояние. Задний фронт синхроимпульса (фронт 1/0) сначала отделяет первую ступень от входной информации, а затем открывает эле- менты D5 и D6, разрешая ЗЯ второй ступени скопировать состоя- ние первой ступени. Более детально логику работы данного триггера иллюстрирует временная диаграмма, приведенная на рис. 3.11.

УГО JK-триггера: