- •Построение памяти повышенной надежности Корректирующие коды

- •Аппаратура кода Хэмминга

- •Аппаратурная реализация системы контроля по коду ко-од

- •Самоконтролируемая система контроля по коду Хэмминга

- •Методы исправления двойных ошибок Последовательная коррекция

- •Методы обеспечения отказоустойчивости памяти

- •Лабораторные работы № 1, 2 Исследование методов построения высоконадежных зу Цель работы

- •Домашняя подготовка

- •Постановка заданий для проведения лабораторных работ

- •Экспериментальные исследования

- •Выполнение лабораторной работы № 2

Методы обеспечения отказоустойчивости памяти

К методам обеспечения отказоустойчивости ОЗУ относятся:

разнесение неисправимых двойных ошибок путем логической перестановки адресов неисправных БИС памяти:

постоянная (ручная) логическая перестановка адресов;

управляемая логическая перестановка адресов;

автоматическая логическая перестановка адресов;

подключение резервных ТЭЗ памяти;

алгоритмическая коррекция неисправимых ошибок.

Использование метода разнесения двойных неисправимых ошибок путем логической перестановки адресов неисправных БИС памяти основано на использовании кода КО-ОД путем замены одной двойной ошибки двумя одиночными исправимыми ошибками.

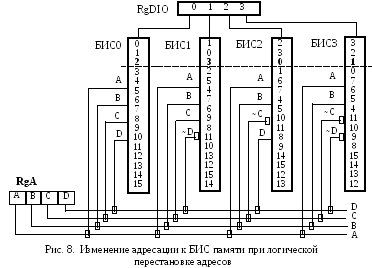

На рис. 8 показано размещение адресов БИС памяти при инверсии некоторых бит адреса, поступающих на адресные входы этих БИС. При такой организации имеет место измененный порядок выборки ячеек ОЗУ в каждой БИС памяти. Например, при RgA=0010 в БИС0 выбирается ячейка с физическим адресом 0010, в БИС1 - 0011, БИС2 - 0000, БИС3 - 0001 и т.д.

Таким образом, если на ТЭЗе памяти для каждого адресного входа предусмотреть переключатель с инвертором адресного бита, то при обнаружении двойной ошибки обслуживающий персонал, выполнив переключение адресного входа неисправной БИС памяти, фактически выполнит разнесение двойной ошибки на две одиночные (ручная перестановка). Этот метод наиболее эффективно работает только при использовании однобитных БИС памяти. После ручного переключения адреса обязательно выполняется прогон тестов памяти для определения правильности разнесения всех двойных ошибок, выполняется перезагрузка ОС и прикладных программ, после чего ЭВМ может продолжить работу.

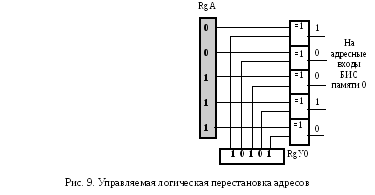

Управляемая логическая перестановка адресов позволяет несколько автоматизировать процедуру переключения (инверсии) адресных бит путем инверсии адресных бит через схему сложения по модулю два (рис. 9), на вторые входы которых подается информация из регистра управления. В зависимости от состояния RgУ на адресные входы БИС памяти информация поступает в прямом или обратном коде. Если в БИС ОЗУ имеется несколько неисправимых ошибок, то возникает задача подбора таких состояний RgУ, которые обеспечили бы разнесение всех неисправимых ошибок.

Для этих целей существуют алгоритмы вычисления значений RgУ.

Начальное значение всех RgУi и множества неисправных адресов FP равно нулю (i=1).

Формируется множество неисправных адресов:

FPi = FPi-1 (RgAi RgУi).

3. i := i+1. При обнаружении двойной ошибки формируется список запрещенных значений RgУi путем сложения по mod 2 всех изменяемых адресов из множества FPi с очередным адресом неисправной БИС: В=FPi-1 RgAi. В качестве значения RgУi выбирается один из кодов, не содержащихся в множестве В.

4. Переход к пункту 2 до тех пор, пока в множестве В не будет неиспользованных кодов для всех RgУi.

|

RgA ОЗУ (ЛА) |

Номер БИС ОЗУ |

Состо-яние RgУi |

Физический адрес на входах БИС ОЗУ |

|

|

0 |

10101 |

10010 |

|

00111 |

1 |

11011 |

11100 |

|

|

2 |

00100 |

00011 |

|

|

3 |

00110 |

00001 |