- •1. TABLE OF CONTENTS

- •2. OVERVIEW

- •3. PROCESS CONTROL

- •3.1 INTRODUCTION

- •3.2 CONTROL SYSTEM CHARACTERISTICS

- •3.3 CONTROLLER TYPES

- •3.4 PROCESS DIAGRAMS AND SYMBOLS

- •3.5 PRACTICE QUESTIONS

- •4. DISCRETE CONTROLLER DESIGN

- •4.1 POSITIONING CONTROLLERS

- •4.1.1 Dead Beat Control

- •4.1.2 Programming Examples

- •4.1.2.1 - BASIC

- •4.1.2.3 - Pascal

- •4.1.2.4 - 6811 Assembler

- •4.1.3 First Order Response

- •4.2 TRACKING

- •4.2.1 Minimum Error

- •4.3 DISTURBANCE RESISTANT

- •4.3.1 Disturbance Minimization

- •4.4 MULTI-CONTROLLER SYSTEMS

- •4.4.1 Disturbance Feedforward

- •4.4.2 Command Feedforward

- •4.4.3 Cascade

- •4.5 SAMPLE TIME

- •4.6 SUMMARY

- •4.7 PRACTICE PROBLEMS

- •5. DISCRETE SYSTEMS

- •5.1 DISCRETE SYSTEM MODELLING WITH EQUATIONS

- •5.1.1 Getting a Discrete Equation

- •5.1.2 First Order System Example

- •5.1.3 Second Order System Example

- •5.1.4 Example of Dead (Delay) Time

- •5.2 DISCRETE CONTROLLERS

- •5.2.1 A Proportional Controller

- •5.2.2 Integral Control

- •5.2.3 Differential Control

- •5.2.4 Proportional, Integral, Derivative (PID) Control

- •5.3 BLOCK DIAGRAMS AND TRANSFER FUNCTIONS

- •5.3.1 The Backward-Shift ‘B’ Operator

- •5.3.2 Reducing Block Diagrams

- •5.3.3 Back-Shift Transform Table

- •5.3.3.1 - A Summary of Differential Equation Solutions

- •5.3.4 Stability

- •5.4 SAMPLING FUNCTIONS

- •5.5 SYSTEM RESPONSE

- •5.6 STEADY STATE ERROR

- •5.7 PRACTICE PROBLEMS

- •6. PETRI NETS

- •6.1 INTRODUCTION

- •6.2 IMPLEMENTATION FOR A PLC

- •6.3 PRACTICE PROBLEMS

- •7. CONTINUOUS CONTROL SYSTEMS

- •7.1 CONTROL SYSTEMS

- •7.1.1 PID Control Systems

- •7.1.2 Analysis of PID Controlled Systems With Laplace Transforms

- •7.1.3 Manipulating Block Diagrams

- •7.1.3.1 - Commercial PID Tuners

- •7.1.4 Finding The System Response To An Input

- •7.1.5 System Response

- •7.1.6 A Motor Control System Example

- •7.1.7 System Error

- •7.1.8 Controller Transfer Functions

- •7.2 ROOT-LOCUS PLOTS

- •7.2.1 Approximate Plotting Techniques

- •7.2.2 State Variable Control Systems

- •7.3 DESIGN OF CONTINUOUS CONTROLLERS

- •7.4 PRACTICE PROBLEMS

- •8. FUZZY LOGIC

- •8.1 COMMERCIAL CONTROLLERS

- •8.2 REFERENCES

- •8.3 PRACTICE PROBLEMS

- •9. MECHATRONICS CIRCUITS

- •9.1 POWER SWITCHING

- •9.2 USER INPUT/OUTPUT

- •9.2.1 Multiplexing

- •10. HARDWARE BASED CONTROLLERS

- •10.1 CIRCUITS

- •10.2 FLUIDICS

- •10.3 PNEUMATICS

- •10.4 PRACTICE PROBLEMS

- •11. EMBEDDED CONTROLLERS

- •11.1 TYPES

- •11.1.1 Micro Controllers

- •11.1.2 DSPs

- •11.1.3 CPUs

- •11.2 CONTROLLER DESIGN EXAMPLE

- •11.3 PRACTICE PROBLEMS

- •12. DISCRETE SENSORS

- •12.1 INTRODUCTION

- •12.2 SENSOR WIRING

- •12.2.1 Switches

- •12.2.2 Transistor Transistor Logic (TTL)

- •12.2.3 Sinking/Sourcing

- •12.2.4 Solid State Relays

- •12.3 CONTACT DETECTION

- •12.3.1 Contact Switches

- •12.3.2 Reed Switches

- •12.4 PROXIMITY DETECTION

- •12.4.1 Optical (Photoelectric) Sensors

- •12.4.2 Capacitive Sensors

- •12.4.3 Inductive Sensors

- •12.4.4 Ultrasonic

- •12.4.5 Hall Effect

- •12.4.6 Fluid Flow

- •12.4.7 Other Types

- •12.5 PRACTICE PROBLEMS

- •13. CONTINUOUS SENSORS

- •13.1 INPUT ISSUES

- •13.2 SENSOR TYPES

- •13.3 ANGULAR POSITION

- •13.3.1 Potentiometers

- •13.3.2 Encoders

- •13.3.3 Resolvers

- •13.3.4 Practice Problems

- •13.4 LINEAR POSITION

- •13.4.1 Potentiometers

- •13.4.2 Linear Variable Differential Transformers (LVDT)

- •13.4.3 Moire Fringes

- •13.4.4 Interferometers

- •13.5 VELOCITY

- •13.5.1 Velocity Pickups

- •13.5.2 Tachometers

- •13.6 ACCELERATION

- •13.6.1 Accelerometers

- •13.7 FORCE/MOMENT

- •13.7.1 Strain Gages

- •13.7.2 Piezoelectric

- •13.8 FLOW RATE

- •13.8.1 Venturi

- •13.9 TEMPERATURE

- •13.9.1 Resistive Temperature Detectors (RTDs)

- •13.9.2 Thermocouples

- •13.9.3 Thermistors

- •13.10 SOUND

- •13.10.1 Microphones

- •13.11 LIGHT INTENSITY

- •13.11.1 Light Dependant Resistors (LDR)

- •13.12 PRESSURE

- •13.12.1 Bourdon Tubes

- •13.13 PRACTICE PROBLEMS

- •13.14 REFERENCES

- •14. ACTUATORS

- •14.1 ACTUATOR TYPES

- •15. DISCRETE ACTUATORS

- •15.1 INTRODUCTION

- •15.1.1 Interfacing

- •15.1.1.1 - Relays

- •15.1.1.2 - Transistors

- •15.1.1.3 - Triacs

- •15.2 TYPES

- •15.2.1 Solenoids

- •15.2.2 Hydraulic

- •15.2.3 Hydraulics

- •15.2.4 Electric

- •15.2.5 Pneumatic

- •15.2.6 Others

- •15.3 PRACTICE PROBLEMS

- •16. CONTINUOUS ACTUATORS

- •16.1 ACTUATOR CONTROL

- •16.1.1 Block Diagrams

- •16.1.2 Linear Control Systems

- •16.1.3 Motor Controllers

- •16.1.3.1 - DC Motors

- •16.1.3.2 - Stepper Motors

- •16.1.3.3 - Separately Excited DC Motor

- •16.1.3.4 - AC Motors

- •16.1.3.4.1 - Synchronous

- •16.1.4 Hydraulic

- •16.2 PRACTICE PROBLEMS

- •17. PROGRAMMABLE LOGIC CONTROLLERS

- •17.1 BASIC PLCs

- •17.1.1 PLC Connections

- •17.1.2 Ladder Logic

- •17.1.3 Ladder Logic Outputs

- •17.1.4 Ladder Logic Inputs

- •17.2 A SIMPLE EXAMPLE

- •17.3 PRACTICE PROBLEMS

- •18. PLC CONNECTION

- •18.1 SWITCHED INPUTS AND OUTPUTS

- •18.1.1 Input Modules

- •18.1.2 Output Modules

- •18.1.2.1 - Relays

- •18.2 PRACTICE PROBLEMS

- •19. PLC OPERATION

- •19.1 PLC ORGANIZATION

- •19.2 PLC STATUS

- •19.3 MEMORY TYPES

- •19.4 SOFTWARE BASED PLCS

- •19.5 PROGRAMMING STANDARDS

- •19.5.2 The Future of Open Architecture Controllers

- •19.6 PRACTICE PROBLEMS

- •20. SWITCHING LOGIC

- •20.1 BOOLEAN ALGEBRA

- •20.2 DISCRETE LOGIC

- •20.2.1 Boolean Algebra for Circuit and Ladder Logic Design

- •20.2.2 Boolean Forms

- •20.3 SIMPLIFYING BOOLEAN EQUATIONS

- •20.3.1 Karnaugh Maps for Combinatorial Design

- •20.4 ADDITIONAL TOPICS

- •20.4.1 Negative Logic

- •20.4.2 Common Logic Forms

- •20.4.2.1 - NAND/NOR Forms

- •20.4.2.2 - Multiplexers

- •20.4.2.3 - Seal-in Circuits

- •20.5 DESIGN CASES

- •20.5.1 Logic Functions

- •20.5.2 Car Safety System

- •20.5.3 Motor Forward/Reverse

- •20.6 PRACTICE PROBLEMS

- •21. NUMBERING

- •21.1 INTRODUCTION

- •21.2 DATA VALUES

- •21.2.1 Binary

- •21.2.2 Boolean Operations

- •21.2.3 Binary Mathematics

- •21.2.4 BCD (Binary Coded Decimal)

- •21.2.5 Number Conversions

- •21.2.6 ASCII (American Standard Code for Information Interchange)

- •21.3 DATA CHARACTERIZATION

- •21.3.1 Parity

- •21.3.2 Gray Code

- •21.3.3 Checksums

- •21.4 PRACTICE PROBLEMS

- •22. EVENT BASED LOGIC

- •22.1 INTRODUCTION

- •22.2 TIMERS, COUNTERS, FLIP-FLOPS, LATCHES

- •22.2.1 Latches

- •22.2.2 Flip-Flops

- •22.2.3 Timers

- •22.2.4 Counters

- •22.3 PROGRAM DESIGN METHODS

- •22.3.1 Process Sequence Bits

- •22.3.2 Timing Diagrams

- •22.4 DESIGN CASES

- •22.4.1 Counters And Timers

- •22.4.2 More Timers And Counters

- •22.4.3 Oscillator

- •22.4.4 More Timers

- •22.4.5 Cascaded Timers

- •22.4.6 Deadman Switch

- •22.4.7 Conveyor

- •22.4.8 Accept/Reject Sorting

- •22.4.9 Shear Press

- •22.4.10 Actuator Failure

- •22.4.11 Palm Button Detection

- •22.5 PRACTICE PROBLEMS

- •23. SEQUENTIAL LOGIC DESIGN

- •23.1 SCRIPTS

- •23.2 FLOW CHARTS

- •23.3 STATE BASED MODELLING

- •23.3.1 State Diagrams Example

- •23.3.1.1 - Block Logic Conversion

- •23.3.1.2 - Single State Equations

- •23.3.1.3 - Entry and Exit State Equations

- •23.3.1.4 - State Transition Equations

- •23.4 PARALLEL PROCESS FLOWCHARTS

- •23.4.1 Implementation with Microcontroller

- •23.5 SEQUENTIAL LOGIC CIRCUITS

- •23.5.1 Latches and Seal-in

- •23.5.2 Shift Registers

- •23.6 PRACTICE PROBLEMS

- •24. ADVANCED LADDER LOGIC FUNCTIONS

- •24.1 ADDRESSING

- •24.1.1 Data Files

- •24.1.1.1 - Inputs and Outputs

- •24.1.1.2 - User Bit Memory

- •24.1.1.3 - Timer Counter Memory

- •24.1.1.4 - PLC Status Bits (for PLC-5s and Micrologix)

- •24.1.1.5 - User Function Control Memory

- •24.1.1.6 - Integer Memory

- •24.1.1.7 - Floating Point Memory

- •24.2 INSTRUCTION TYPES

- •24.2.1 Basic Data Handling

- •24.2.1.1 - Move Functions

- •24.2.1.2 - Mathematical Functions

- •24.2.2 Logical Functions

- •24.2.2.1 - Comparison of Values

- •24.2.2.2 - Binary Functions

- •24.2.3 Boolean Operations

- •24.2.4 Binary Mathematics

- •24.2.5 BCD (Binary Coded Decimal)

- •24.2.6 Advanced Data Handling

- •24.2.6.1 - Multiple Data Value Functions

- •24.2.7 Complex Functions

- •24.2.7.1 - Shift Registers

- •24.2.7.2 - Stacks

- •24.2.7.3 - Sequencers

- •24.2.8 Program Control Structures

- •24.2.8.1 - Branching and Looping

- •24.2.8.2 - Immediate I/O Instructions

- •24.2.8.3 - Fault Detection and Interrupts

- •24.2.9 Block Transfer Functions

- •24.3 DESIGN TECHNIQUES

- •24.3.1 State Diagrams

- •24.4 DESIGN CASES

- •24.4.1 If-Then

- •24.4.2 For-Next

- •24.4.3 Conveyor

- •24.5 FUNCTION REFERENCE

- •24.6 PRACTICE PROBLEMS

- •25. PLC PROGRAMMING

- •25.1 PROGRAMMING STANDARDS

- •25.1.2 The Future of Open Architecture Controllers

- •25.2 PRACTICE PROBLEMS

- •26. STRUCTURED TEXT PROGRAMMING

- •26.1 INTRODUCTION

- •26.2 THE LANGUAGE

- •26.3 PRACTICE PROBLEMS

- •27. INSTRUCTION LIST PROGRAMMING

- •27.1 INTRODUCTION

- •27.2 PRACTICE PROBLEMS

- •28. FUNCTION BLOCK PROGRAMMING

- •28.1 INTRODUCTION

- •28.2 PRACTICE PROBLEMS

- •29. ANALOG INPUTS AND OUTPUTS

- •29.1 ANALOG INPUTS

- •29.1.1 Analog To Digital Conversions

- •29.1.2 Analog Inputs With a PLC

- •29.2 ANALOG OUTPUTS

- •29.2.1 Analog Outputs With A PLC

- •29.3 DESIGN CASES

- •29.3.1 Oven Temperature Control

- •29.3.2 Statistical Process Control (SPC)

- •29.4 PRACTICE PROBLEMS

- •30. CONTINUOUS CONTROL

- •30.1 CONTROLLING CONTINUOUS SYSTEMS

- •30.2 CONTROLLING DISCRETE SYSTEMS

- •30.3 CONTROL SYSTEMS

- •30.3.1 PID Control Systems

- •30.3.1.1 - PID Control With a PLC

- •30.4 DESIGN CASES

- •30.4.1 Temperature Controller

- •30.5 PRACTICE PROBLEMS

- •31. PLC DATA COMMUNICATION

- •31.1 COMPUTER COMMUNICATIONS CATEGORIES

- •31.2 THE HISTORY

- •31.3 WITH PLCs

- •31.4 SERIAL COMMUNICATIONS

- •31.4.1.1 - ASCII Functions

- •31.4.2 ASCII (American Standard Code for Information Interchange)

- •31.5 PARALLEL

- •31.6 NETWORKS

- •31.6.1 Introduction

- •31.6.2 OSI Network Model

- •31.6.2.1 - Physical Layer

- •31.6.2.2 - Data Link Layer

- •31.6.2.3 - Network Layer

- •31.6.2.4 - Transport Layer

- •31.6.2.5 - Session Layer

- •31.6.2.6 - Presentation Layer

- •31.6.2.7 - Application Layer

- •31.6.2.8 - Open Systems

- •31.6.2.9 - Networking Hardware

- •31.7 BUS TYPES

- •31.7.1 Devicenet

- •31.7.2 CANbus

- •31.7.3 Controlnet

- •31.7.4 Profibus

- •31.7.5 Ethernet

- •31.7.6 Proprietary Networks

- •31.7.6.1 - Data Highway

- •31.7.7 Other Network Types

- •31.8 DESIGN CASES

- •31.8.1 PLC Interface To Robots And NC Machines

- •31.9 PRACTICE PROBLEMS

- •32. HUMAN MACHINE INTERFACES (HMI)

- •32.1 INTRODUCTION

- •32.2 HMI/MMI DESIGN

- •32.3 DESIGN CASES

- •32.4 PRACTICE PROBLEMS

- •33. DESIGNING LARGE SYSTEMS

- •33.1 PROGRAMMING

- •33.2 DOCUMENTATION

- •33.3 PLC PROGRAM DESIGN FORMS

- •33.4 PRACTICE PROBLEMS

- •34. IMPLEMENTATION

- •34.1 ELECTRICAL

- •34.1.1 Electrical Wiring Diagrams

- •34.1.1.1 - JIC Wiring Symbols

- •34.1.2 Wiring

- •34.1.3 Shielding and Grounding

- •34.2 SAFETY

- •34.2.1 Troubleshooting

- •34.2.2 Forcing Outputs

- •34.2.3 PLC Environment

- •34.2.3.1 - Enclosures

- •35. PROCESS MODELLING

- •35.1 REFERENCES

- •35.2 PRACTICE PROBLEMS

- •36. SELECTING A PLC

- •36.1 SPECIAL I/O MODULES

- •36.2 PLC PROGRAMMING LANGUAGES

- •36.3 ISSUES

- •36.4 PRACTICE PROBLEMS

- •37. PLC REFERENCES

- •37.1 SUPPLIERS

- •37.2 PROFESSIONAL INTEREST GROUPS

- •37.3 PLC/DISCRETE CONTROL REFERENCES

- •38. USING THE OMRON DEMO PACKAGE

- •38.1 OVERVIEW

- •38.1.1 Installation

- •38.1.2 Basic Use

- •38.1.3 Connecting to the PLC

- •38.2 REFERENCE GUIDE FOR OMRON PLC DEMO SOFTWARE

- •39. INDUSTRIAL ROBOTICS

- •39.1 INTRODUCTION

- •39.1.1 Basic Terms

- •39.1.2 Positioning Concepts

- •39.1.2.1 - Accuracy and Repeatability

- •39.1.2.2 - Control Resolution

- •39.1.2.3 - Payload

- •39.2 ROBOT TYPES

- •39.2.1 Basic Robotic Systems

- •39.2.2 Types of Robots

- •39.2.2.1 - Robotic Arms

- •39.2.2.2 - Autonomous/Mobile Robots

- •39.2.2.2.1 - Automatic Guided Vehicles (AGVs)

- •39.2.3 Commercial Robots

- •39.2.3.1 - Seiko RT 3000 Manipulator

- •39.2.3.2 - DARL Programs

- •39.2.3.2.1 - Language Examples

- •39.2.3.2.2 - Commands Summary

- •39.2.3.3 - Mitsubishi RV-M1 Manipulator

- •39.2.3.4 - Movemaster Programs

- •39.2.3.4.1 - Language Examples

- •39.2.3.4.2 - Command Summary

- •39.2.3.5 - IBM 7535 Manipulator

- •39.2.3.6 - AML Programs

- •39.2.3.7 - ASEA IRB-1000

- •39.2.4 Unimation Puma (360, 550, 560 Series)

- •39.3 ROBOT APPLICATIONS

- •39.3.1 Overview

- •39.3.2 Spray Painting and Finishing

- •39.3.3 Welding

- •39.3.4 Assembly

- •39.3.5 Belt Based Material Transfer

- •39.4 END OF ARM TOOLING (EOAT)

- •39.4.1 EOAT Design

- •39.4.2 Gripper Mechanisms

- •39.4.2.1 - Vacuum grippers

- •39.4.3 Magnetic Grippers

- •39.4.3.1 - Adhesive Grippers

- •39.4.4 Expanding Grippers

- •39.4.5 Other Types Of Grippers

- •39.5 ADVANCED TOPICS

- •39.5.1 Simulation/Off-line Programming

- •39.6 PRACTICE PROBLEMS

- •40. ROBOTIC PATH PLANNING METHODS

- •40.1 INTRODUCTION:

- •40.1.1 ROBOT APPLICATIONS

- •40.1.2 ROBOTIC CONSTRAINTS

- •40.1.3 THE OPTIMIZATION PROBLEM OF PATH PLANNERS

- •40.1.4 EVALUATION OF PATH PLANNERS

- •40.2 GENERAL REQUIREMENTS

- •40.2.1 PROBLEM DIMENSIONALITY

- •40.2.2 2D MOBILITY PROBLEM

- •40.2.2.1 - 2.5D HEIGHT PROBLEM

- •40.2.2.2 - 3D SPACE PROBLEM

- •40.2.3 COLLISION AVOIDANCE

- •40.2.4 MULTILINK

- •40.2.5 ROTATIONS

- •40.2.6 OBSTACLE MOTION PROBLEM

- •40.2.7 ROBOT COORDINATION

- •40.2.8 INTERACTIVE PROGRAMMING

- •40.3 SETUP EVALUATION CRITERIA

- •40.3.1 INFORMATION SOURCE

- •40.3.1.1 - KNOWLEDGE BASED PLANNING (A PRIORI)

- •40.3.1.2 - SENSOR BASED PLANNING (A POSTIERI)

- •40.3.2 WORLD MODELLING

- •40.4 METHOD EVALUATION CRITERIA

- •40.4.1 PATH PLANNING STRATEGIES

- •40.4.1.1 - BASIC PATH PLANNERS (A PRIORI)

- •40.4.1.2 - HYBRID PATH PLANNERS (A PRIORI)

- •40.4.1.3 - TRAJECTORY PATH PLANNING (A POSTIERI)

- •40.4.1.4 - HIERARCHICAL PLANNERS (A PRIORI & A POSTIERI)

- •40.4.1.5 - DYNAMIC PLANNERS (A PRIORI & A POSTIERI)

- •40.4.1.6 - OFF-LINE PROGRAMMING

- •40.4.1.7 - ON-LINE PROGRAMMING

- •40.4.2 PATH PLANNING METHODS

- •40.4.3 OPTIMIZATION TECHNIQUES

- •40.4.3.1 - SPATIAL PLANNING

- •40.4.3.2 - TRANSFORMED SPACE

- •40.4.3.3 - FIELD METHODS

- •40.4.3.4 - NEW AND ADVANCED TOPICS

- •40.4.4 INTERNAL REPRESENTATIONS

- •40.4.5 MINIMIZATION OF PATH COSTS

- •40.4.6 LIMITATIONS IN PATH PLANNING

- •40.4.7 RESULTS FROM PATH PLANNERS

- •40.5 IMPLEMENTATION EVALUATION CRITERIA

- •40.5.1 COMPUTATIONAL TIME

- •40.5.2 TESTING OF PATH PLANNERS

- •40.6 OTHER AREAS OF INTEREST

- •40.6.1 ERRORS

- •40.6.2 RESOLUTION OF ENVIRONMENT REPRESENTAION

- •40.7 COMPARISONS

- •40.8 CONCLUSIONS

- •40.9 APPENDIX A - OPTIMIZATION TECHNIQUES

- •40.9.1 OPTIMIZATION : VELOCITY

- •40.9.2 OPTIMIZATION : GEOMETRICAL

- •40.9.3 OPTIMIZATION : PATH REFINEMENT

- •40.9.4 OPTIMIZATION : MOVING OBSTACLES

- •40.9.5 OPTIMIZATION : SENSOR BASED

- •40.9.6 OPTIMIZATION : ENERGY

- •40.10 APPENDIX B - SPATIAL PLANNING

- •40.10.1 SPATIAL PLANNING : SWEPT VOLUME

- •40.10.2 SPATIAL PLANNING : OPTIMIZATION

- •40.10.3 SPATIAL PLANNING : GENERALIZED CONES

- •40.10.4 SPATIAL PLANNING : FREEWAYS

- •40.10.5 SPATIAL PLANNING : OCT-TREE

- •40.10.6 SPATIAL PLANNING : VORONOI DIAGRAMS

- •40.10.7 SPATIAL PLANNING : GENERAL INTEREST

- •40.10.8 SPATIAL PLANNING - VGRAPHS

- •40.11 APPENDIX C - TRANSFORMED SPACE

- •40.11.1 TRANSFORMED SPACE : CARTESIAN CONFIGURATION SPACE

- •40.11.1.1 - TRANSFORMED SPACE :

- •40.11.2 TRANSFORMED SPACE : JOINT CONFIGURATION SPACE

- •40.11.3 TRANSFORMED SPACE : OCT-TREES

- •40.11.4 TRANSFORMED SPACE : CONSTRAINT SPACE

- •40.11.5 TRANSFORMED SPACE : VISION BASED

- •40.11.6 TRANSFORMED SPACE : GENERAL INTEREST

- •40.12 APPENDIX D - FIELD METHODS

- •40.12.1 SPATIAL PLANNING : STEEPEST DESCENT

- •40.12.2 SPATIAL PLANNING : POTENTIAL FIELD METHOD

- •40.13 APPENDIX E - NEW AND ADVANCED TOPICS

- •40.13.1 ADVANCED TOPICS : DUAL MANIPULATOR COOPERATION

- •40.13.2 ADVANCED TOPICS : A POSTIERI PATH PLANNER

- •40.13.3 NEW TOPICS - SLACK VARIABLES

- •40.14 REFERENCES:

- •41. ROBOTIC MECHANISMS

- •41.1 KINEMATICS

- •41.1.1 Basic Terms

- •41.1.2 Kinematics

- •41.1.2.1 - Geometry Methods for Forward Kinematics

- •41.1.2.2 - Geometry Methods for Inverse Kinematics

- •41.2 MECHANISMS

- •41.3 ACTUATORS

- •41.3.1 Modeling the Robot

- •41.4 PATH PLANNING

- •41.4.1 Slew Motion

- •41.4.1.1 - Joint Interpolated Motion

- •41.4.1.2 - Straight-line motion

- •41.4.2 Computer Control of Robot Paths (Incremental Interpolation)

- •41.5 PRACTICE PROBLEMS

- •42. MOTION PLANNING AND TRAJECTORY CONTROL

- •42.1 TRAJECTORY CONTROL

- •42.1.1 Resolved Rate Motion Control

- •42.1.2 Cartesian Motion System

- •42.1.3 Model Reference Adaptive Control (MRAC)

- •42.1.4 Digital Control System

- •42.2 PATH PLANNING

- •42.2.1 Slew Motion

- •42.2.1.1 - Joint Interpolated Motion

- •42.2.1.2 - Straight-line motion

- •42.3 MOTION CONTROLLERS

- •42.3.1 Computer Control of Robot Paths (Incremental Interpolation)

- •42.4 SPECIAL ISSUES

- •42.4.1 Optimal Motion

- •42.4.2 Singularities

- •42.5 PRACTICE PROBLEMS

- •42.6 MICROBOT OVERVIEW

- •42.7 CRS PLUS ROBOT OVERVIEW

- •42.8 BASIC DEMONSTRATION STEPS

- •43. CNC MACHINES

- •43.1 MACHINE AXES

- •43.2 NUMERICAL CONTROL (NC)

- •43.2.1 NC Tapes

- •43.2.2 Computer Numerical Control (CNC)

- •43.2.3 Direct/Distributed Numerical Control (DNC)

- •43.3 EXAMPLES OF EQUIPMENT

- •43.3.1 EMCO PC Turn 50

- •43.3.2 Light Machines Corp. proLIGHT Mill

- •43.4 PRACTICE PROBLEMS

- •44. CNC PROGRAMMING

- •44.1 G-CODES

- •44.3 PROPRIETARY NC CODES

- •44.4 GRAPHICAL PART PROGRAMMING

- •44.5 NC CUTTER PATHS

- •44.6 NC CONTROLLERS

- •44.7 PRACTICE PROBLEMS

page 445

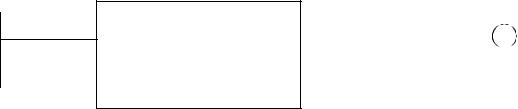

24.5 FUNCTION REFERENCE

•The following function descriptions are for both the micrologix (500/1000) and PLC-5 processor families.

•Note that floating point operations are not available on the micrologix.

•Some of the flags referred to functions are:

S2:0/0 carry in math operation

S2:0/1 overflow in math operation

S2:0/2 zero in math operation

S2:0/3 sign in math operation

GENERAL FUNCTIONS

AFI - Always False Instruction

|

|

|

|

|

AFI |

|

|

|

|

||

|

|

|

|

|

|

|

|

Description: |

Putting this instruction in a line will force the line to be false. This is prima- |

||

|

rily designed for debugging programs. |

||

Status Bits: |

none |

||

Registers: |

none |

||

Available on: Micrologix, PLC-5

page 446

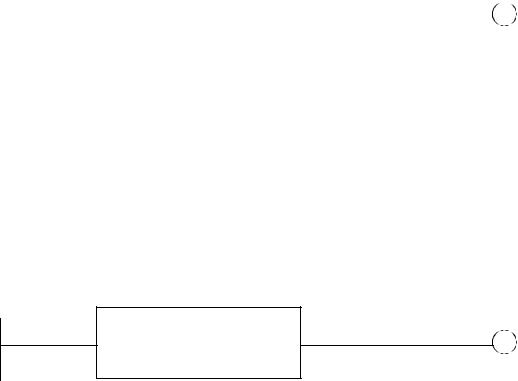

MCR - Master Control Relay

|

A |

|

|

|

|

MCR |

||

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

MCR |

|

|

|

|

|

|

|

|

||

|

Description: |

MCR instructions need to be used in pairs. If the first MCR line is true the |

||||||

|

|

|

instructions up to the next MCR will be examined normally. If the first |

|||||

|

|

|

MCR line is not true the outputs on the lines after will be FORCED |

|||||

|

|

|

OFF. Be careful when using normal outputs in these blocks. |

|||||

|

Status Bits: |

none |

|

|

|

|

|

|

|

Registers: |

none |

|

|

|

|

|

|

|

Available on: Micrologix, PLC-5 |

|

|

|

||||

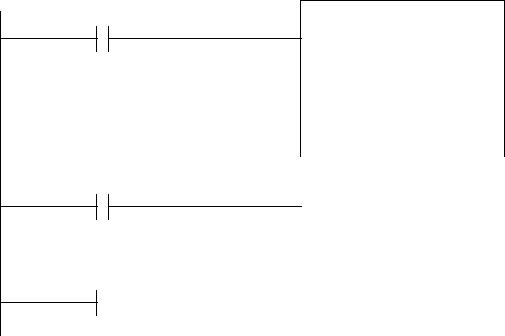

TIMERS |

|

|

|

|

|

|

||

|

TON - Timer ON |

|

|

|

|

|

||

|

|

A |

|

|

TON |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

TIMER ON DELAY |

|

||

|

|

|

|

|||||

|

|

|

|

|

Timer |

T4:0 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

Time Base |

1.0 |

|

|

|

|

|

|

|

Preset |

10 |

|

|

|

|

|

|

|||||

|

|

|

|

|

Accum. |

0 |

|

|

|

Description: |

This timer will delay turning on, but will turn off immediately. Once the |

||||||

|

|

|

input turns on the accumulated value (ACC) will start to increase from |

|||||

|

|

|

zero. When the preset (PRE) value is reached the DN bit is set. The done |

|||||

|

|

|

bit will turn off and the accumulator will reset to zero if the input goes |

|||||

|

|

|

false. |

|

|

|

|

|

|

Status Bits: |

EN |

This bit is true while the input to the timer is true |

|||||

|

|

|

TT |

This bit is true while the accumulator value is increasing |

||||

|

|

|

DN |

This bit is true when the accumulator value is equal to the preset |

||||

|

|

|

|

value |

|

|

|

|

|

Registers: |

ACC |

The time that has passed since the input went true |

|||||

|

|

|

PRE |

The maximum time delay before the timer goes on |

||||

Available on: Micrologix, PLC-5

page 447

TOF - Timer OFf |

|

|

|||

|

|

A |

TOF |

|

|

|

|

||||

|

|

|

|

TIMER OFF DELAY |

|

|

|

|

|

||

|

|

|

|

Timer |

T4:0 |

|

|

|

|

||

|

|

|

|

Time Base |

1.0 |

|

|

|

|

Preset |

10 |

|

|

|

|

||

|

|

|

|

Accum. |

0 |

Description: |

This timer will delay turning off (the done bit, DN, will turn on immedi- |

|

|

ately). Once the input turns off the accumulated value (ACC) will start |

|

|

to increase from zero. When the preset (PRE) value is reached the DN |

|

|

bit is turned off and the accumulator will reset to zero. If the input turns |

|

|

on before the off delay is complete the accumulator will reset to zero. |

|

Status Bits: |

EN |

This bit is true while the input to the timer is true |

|

TT |

This bit is true while the accumulator value is increasing |

|

DN |

This bit is true when the accumulator value is less than the preset |

|

|

value and the input is true, or the accumulator is changing |

Registers: |

ACC |

The time that has passed since the input went false |

|

PRE |

The maximum time delay before the timer goes off |

Available on: Micrologix, PLC-5

page 448

RTO - RetentiveTimer On |

|

|

|||

|

|

A |

RTO |

|

|

|

|

||||

|

|

|

|

RETENTIVE TIMER ON |

|

|

|

|

|

||

|

|

|

|

Timer |

T4:0 |

|

|

|

|

||

|

|

|

|

Time Base |

1.0 |

|

|

|

|

Preset |

10 |

|

|

|

|

||

|

|

|

|

Accum. |

0 |

Description: |

This timer will delay turning on. When the input turns on the accumulated |

|

|

value (ACC) will start to increase from zero. When the preset (PRE) |

|

|

value is reached the DN bit is set. If the input goes false the accumulator |

|

|

value is not reset to zero. To reset the timer and turn off the timer the |

|

|

RES instruction should be used. |

|

Status Bits: |

EN |

This bit is true while the input to the timer is true |

|

TT |

This bit is true while the accumulator value is increasing |

|

DN |

This bit is true when the accumulator value is less than the preset |

|

|

value |

Registers: |

ACC |

The time that has passed since the input went true |

|

PRE |

The maximum time delay before the timer goes on |

Available on: Micrologix, PLC-5

COUNTERS

• Counter memory instructions can share the same memory location, so some redundant bits are mentioned here.

page 449

CTU - CounT Up |

|

|

|||

|

|

A |

CTU |

|

|

|

|

||||

|

|

|

|

COUNT UP |

|

|

|

|

|

|

|

|

|

|

|

Counter |

C5:0 |

|

|

|

|

||

|

|

|

|

Preset |

50 |

|

|

|

|

Accum. |

0 |

|

|

|

|

||

|

|

|

|

|

|

Description: |

The counter accumulator will increase once each time the input goes from |

|

|

false to true. If the accumulator value reaches the preset the done bit, |

|

|

DN, will be set. The accumulator value will still increase even when the |

|

|

done bit is set |

|

Status Bits: |

CU |

Will be true when the input is true |

|

CD |

Not used for this instruction |

|

DN |

Will be set when ACC >= PRE |

|

OV |

Will be set if the counter value has gone above 32,767 |

|

UN |

Not used for this instruction |

Registers: |

ACC |

The total count |

|

PRE |

The maximum count before the counter goes on |

Available on: Micrologix, PLC-5

page 450

CTD - CounT Down |

|

|

|||

|

|

A |

CTD |

|

|

|

|

||||

|

|

|

|

COUNT DOWN |

|

|

|

|

|

|

|

|

|

|

|

Counter |

C5:0 |

|

|

|

|

||

|

|

|

|

Preset |

50 |

|

|

|

|

Accum. |

0 |

|

|

|

|

||

|

|

|

|

|

|

Description: |

The counter accumulator will decrease once each time the input goes from |

|

|

false to true. If the accumulator value reaches the preset the done bit, |

|

|

DN, will be set. The accumulator value will still decrease even when the |

|

|

done bit is set |

|

Status Bits: |

CU |

Not used for this instruction |

|

CD |

Will be true when the input is true |

|

DN |

Will be set when ACC < PRE |

|

OV |

Not used for this instruction |

|

UN |

Will be set if the counter value has gone below -32,768 |

Registers: |

ACC |

The time that has passed since the input went true |

|

PRE |

The maximum time delay before the timer goes on |

Available on: Micrologix, PLC-5

COMPARE

LIM - LIMit

LIM |

|

|

|

LIMIT TEST (CIRC) |

|

A |

|

Low limit |

N7:0 |

|

|

|

|

||

Test |

N7:1 |

|

|

High Limit |

N7:2 |

|

|

Description:

Status Bits:

This function will check to see if a value is between two limits. If the high limit is larger than the low limit and the test value is >= low limit or <= high limit, then the output is true. If the low limit is higher than the high limit, then a value not between the low and high limits will be true.

none

Registers: none

Available on: Micrologix, PLC-5

page 451

MEQ - Masked EQual

|

MEQ |

|

|

A |

|

|

|

||

|

MASKED EQUAL |

|

||

|

Source |

N7:0 |

|

|

|

|

|

||

|

Mask |

N7:1 |

|

|

|

Compare |

N7:2 |

|

|

|

|

|

||

|

|

|

|

|

Description:

Status Bits:

Registers:

The Source and Mask values are ANDed together. This will screenout bits not on in the mask. The value is then compared to the ‘Compare’ value. If the values are equal, the output is true.

none

none

Available on: Micrologix, PLC-5

CMP - CoMPare

CMP

COMPARE A Expression

“(N7:0 + 8) > N7:1”

Description: |

This function uses a free form expression to compare the two values. The |

|

comparison values that are allowed include =, >, >=, <>, <, <=. The |

|

expression must not be more than 80 characters long. |

Status Bits: |

none |

Registers: |

none |

Available on: PLC-5

page 452

EQU, GEQ, GRT, LEQ, LES, NEQ

|

EQU |

|

|

A |

|

|

|

||

|

EQUALS |

|

|

|

|

Source A |

N7:0 |

|

|

|

|

|||

|

Source B |

N7:1 |

|

|

|

|

|

|

|

|

|

|

|

|

Description: |

The basic compare has six variations. Each of these will look at the val- |

|

ues in source A and B and check for the comparison case. If the com- |

|

parison case is true, the output will be true. The types are, |

|

EQU - Equals |

|

GEQ - Greater than or equals |

|

GRT - Greater than |

|

LEQ - Less than or equals |

|

LES - Less than |

|

NEQ - Not equal |

Status Bits: |

none |

Registers: none

Available on: Micrologix, PLC-5

CALCULATION

page 453

ACS, ASN, ATN, COS, LN, LOG, NEG, SIN, SQR, TAN |

|

||||

|

|

|

|

|

|

|

|

A |

|

ACS |

|

|

|

||||

|

|

|

|

ARCCOSINE |

|

|

|

|

|

||

|

|

|

|

Source |

N7:0 |

|

|

|

|

||

|

|

|

|

Dest |

N7:1 |

|

|

|

|

|

|

Description: |

These are unary math functions that will load a value from the source, do |

|

|

|

the calculation indicated, and store the results in the destination. Func- |

|

|

tions possible include |

|

ACS - Arccosine (inverse cosine) in radians |

|

|

ASN - Arcsine (inverse sine) in radians |

|

|

ATN - Arctangent (inverse tangent) in radians |

|

|

COS - Cosine using radians |

|

|

LN - Natural Logarithm |

|

|

LOG - Base 10 logarithm |

|

|

NEG - Sign change from positive to negative, or reverse |

|

|

SIN - Sine using radians |

|

|

SQR - Square root |

|

|

TAN - Tangent using radians |

|

Status Bits: |

C |

Carry - set if a carry is generated |

|

V |

Overflow - only set if value exceeds maximum for number type |

|

Z |

Zero - sets if the result is zero. |

|

S |

Sign - set if result is negative |

Registers: none

Available on: Micrologix, PLC-5

page 454

ADD, DIV, MUL, SUB, XPY |

|

|

|||

|

|

|

|

|

|

|

|

A |

ADD |

|

|

|

|

||||

|

|

|

|

ADD |

|

|

|

|

|

|

|

|

|

|

|

Source A |

N7:0 |

|

|

|

|

||

|

|

|

|

Source B |

N7:1 |

|

|

|

|

Dest |

N7:2 |

|

|

|

|

||

|

|

|

|

|

|

Description: |

These are binary math functions that will load two values from sources A |

|

|

|

and B, do the calculation indicated, and store the results in the destina- |

|

|

tion. Functions possible include |

|

ADD - Add two numbers |

|

|

DIV - Divide source A by source B |

|

|

MUL - Multiply A and B |

|

|

SUB - Subtract B from A |

|

|

XPY - Raise X to the power of Y |

|

Status Bits: |

C |

Carry - sets if a carry is generated |

|

V |

Overflow - only set if value exceeds maximum for number type |

|

Z |

Zero - sets if the result is zero. |

|

S |

Sign - sets if the result is negative |

Registers: none

Available on: Micrologix, PLC-5

AVE, STD

Description:

page 455

A |

|

AVE |

|

|

|

AVERAGE FILE |

|

|

|||

|

|

File |

#N7:0 |

|

|

||

|

|

Dest |

N7:10 |

|

|

Control |

R6:0 |

|

|

Length |

10 |

|

|

Postion |

0 |

|

|

|

|

These functions do the basic statistical calculations, average (AVE) and standard deviation (STD). When the input goes from false to true the calculation is begun. The values to be used for the calculation are taken from the memory starting at the start of the file location, for the length indicated. The final result is stored in the Dest. The control file is used for the calculation to keep track of position, and indicate when the calculation is done (it may take more than one PLC scan).

Status Bits: |

C |

Carry - always 0 |

|

V |

Overflow - only set if value exceeds maximum for number type |

|

Z |

Zero - sets if the result is zero. |

|

S |

Sign - sets if the result is negative |

|

EN |

Enable - on when the instruction input is on |

|

DN |

Done - set when the calculation is complete |

|

ER |

Error - set if an error was encountered during calculation |

Registers: none

Available on: Micrologix, PLC-5

SRT - SoRT

Description:

page 456

A |

|

SRT |

|

|

|

SORT |

|

|

|

||

|

|

File |

#N7:0 |

|

|

||

|

|

Control |

R6:0 |

|

|

Length |

10 |

|

|

Position |

0 |

This functions sort the values in memory from lowest value in the first location to the highest value. When the input goes from false to true the calculation is begun. The values to be used for the calculation are sorted in the memory starting at the start of the file location, for the length indicated. The control file is used for the calculation to keep track of position, and indicate when the calculation is done (it may take more than one PLC scan).

Status Bits: |

EN |

Enable - on when the instruction input is on |

|

DN |

Done - set when the calculation is complete |

|

ER |

Error - set if an error was encountered during calculation |

Registers: |

none |

|

Available on: Micrologix, PLC-5

CLR - CLeaR |

|

|

|

||

|

|

|

|

|

|

|

|

A |

|

CLR |

|

|

|

||||

|

|

|

|

CLR |

|

|

|

|

|

||

|

|

|

|

Dest |

N7:0 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Description: |

This value will clear a memory location by putting a zero in it when the |

|

input to the function is true. |

Status Bits: |

none |

Registers: |

none |

Available on: Micrologix, PLC-5

page 457

CPT - ComPuTe |

|

|

|

||

|

|

A |

|

CPT |

|

|

|

||||

|

|

|

|

COMPUTE |

|

|

|

|

|

||

|

|

|

|

Dest |

N7:0 |

|

|

|

|

||

|

|

|

|

Expression |

|

|

|

|

|

“N7:1 - N7:3” |

|

|

|

|

|

||

|

|

|

|

|

|

|

Description: |

This expression allows free-form entry of equations. A maximum of 80 |

|||||

|

|

|

|

characters is permitted. Operations allowed include +, -, | (divide), *, |

|||

|

|

|

|

FRD, BCD, SQR, AND, OR, NOT, XOR, ** (x**y = x to power y), |

|||

|

|

|

|

RAD, DEG, LOG, LN, SIN, COS, TAN, ASN, ACS, ATN |

|||

|

Status Bits: |

none |

|

|

|||

|

Registers: |

none |

|

|

|||

|

Available on: PLC-5 |

|

|

||||

LOGICAL |

|

|

|

|

|

||

|

AND, OR, XOR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

AND |

|

|

|

|

|

|

||||

|

|

|

|

|

BITWISE AND |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Source A |

N7:0 |

|

|

|

|

|

|

|||

|

|

|

|

|

Source B |

N7:1 |

|

|

|

|

|

|

Dest |

N7:2 |

|

|

Description: |

|

|||||

|

|

|

|

||||

|

These functions do basic boolean operations to the numbers in locations |

||||||

|

|

|

|

A and B. The results of the operation are stored in Dest. These calcu- |

|||

|

|

|

|

lations will be perform whenever the input is true. The functions are, |

|||

|

|

|

AND - Bitwise and |

|

|

||

|

|

|

OR - Bitwise or |

|

|

||

|

|

|

XOR - Bitwise exclusive or |

|

|

||

|

Status Bits: |

C |

Carry - always 0 |

|

|

||

|

|

|

V |

Overflow - always 0 |

|

|

|

|

|

|

Z |

Zero - sets if the result is zero. |

|

|

|

|

|

|

S |

Sign - sets if the MSB of the result is set |

|||

Registers: none

Available on: Micrologix, PLC-5

page 458

NOT

Description:

A |

|

NOT |

|

|

|

NOT |

|

|

|

||

|

|

Source |

N7:0 |

|

|

||

|

|

Dest |

N7:1 |

This function will invert all of the bits in a word in memory whenever the input is true.

Status Bits: |

C |

Carry - always 0 |

|

V |

Overflow - always 0 |

|

Z |

Zero - sets if the result is zero. |

|

S |

Sign - sets if the MSB of the result is set |

Registers: none

Available on: Micrologix, PLC-5

CONVERSION

FRD, TOD, DEG, RAD |

|

|

|||

|

|

|

|

|

|

|

|

A |

FRD |

|

|

|

|

||||

|

|

|

|

FROM BCD |

|

|

|

|

|

|

|

|

|

|

|

Source |

N7:0 |

|

|

|

|

||

|

|

|

|

Dest |

N7:1 |

Description: |

This function will convert the value in the source location and store the |

|

|

|

result in the Dest location. The functions possible include, |

|

FRD - From BCD to a 2s compliment integer number |

|

|

TOD - From 2s compliment integer number to BCD |

|

|

DEG - Convert from radians to degrees |

|

|

RAD - Convert from degrees to radians |

|

Status Bits: |

C |

Carry - always 0 |

|

V |

Overflow - sets if an overflow as generated during conversion |

|

Z |

Zero - sets if the result is zero. |

|

S |

Sign - sets if the MSB of the result is set |

Registers: none

Available on: Micrologix, PLC-5

MOVE

page 459

BTD - BiT Distribute |

|

|

|||

|

|

|

|

|

|

|

|

A |

BTD |

|

|

|

|

||||

|

|

|

|

BIT FIELD DISTRIB |

|

|

|

|

|

||

|

|

|

|

Source |

N7:0 |

|

|

|

|

||

|

|

|

|

Source bit |

0 |

|

|

|

|

Dest |

N7:1 |

|

|

|

|

||

|

|

|

|

Dest bit |

4 |

|

|

|

|

Length |

5 |

|

|

|

|

|

|

Description:

Status Bits:

Registers:

This function will copy the bits starting at N7:0/0 to N7:1/4 for a length of 5 bits.

none

none

Available on: Micrologix, PLC-5

MOV

Description:

A |

|

MOV |

|

|

|

MOVE |

|

|

|

||

|

|

Source |

N7:0 |

|

|

||

|

|

Dest |

N7:1 |

This instruction will move values from one location to another, and if necessary change value types, such as integer and floating point.

Status Bits: |

C |

Carry - always 0 |

|

V |

Overflow - Sets if an overflow occurred during conversion |

|

Z |

Zero - sets if the result is zero. |

|

S |

Sign - sets if the MSB of the result is set |

Registers: none

Available on: Micrologix, PLC-5

page 460

MVM - MoVe Masked

Description:

Status Bits:

A |

|

MVM |

|

|

|

MAKSED MOVE |

|

|

|||

|

|

Source |

N7:0 |

|

|

||

|

|

Mask |

N7:1 |

|

|

Dest |

N7:2 |

|

|

|

|

This function will retrieve the values from the source and mask memory and AND them together. Only the bits that are true in the mask will be copied to the new location.

C Carry - always 0

V Overflow - always 0

Z Zero - sets if the result is zero.

S Sign - sets if the MSB of the result is set

Registers: none

Available on: Micrologix, PLC-5

FILE

page 461

TON - Timer ON |

|

|

|||

|

|

A |

|

TON |

|

|

|

||||

|

|

|

|

TIMER ON DELAY |

|

|

|

|

|||

|

|

|

|

Timer |

T4:0 |

|

|

|

|

||

|

|

|

|

Time Base |

1.0 |

|

|

|

|

Preset |

10 |

|

|

|

|||

Description: |

|

Accum. |

0 |

||

cfvgfdg |

|

||||

Status Bits: |

cf |

cfvgfdg |

Registers: |

cf |

cfvgfdg |

Available on: Micrologix, PLC-5

DIAGNOSTIC

page 462

DTR - Data TRansition |

|

|

|

||

|

|

|

|

|

|

|

|

DTR |

|

|

|

|

|

|

|

||

|

|

DATA TRANSITION |

|

A |

|

|

|

Source |

N7:0 |

|

|

|

|

Mask |

00FF |

|

|

|

|

Reference |

N7:1 |

|

|

|

|

|

|||

|

|

|

|

|

|

Description: |

This function will examine the source value and mask out bits using the |

|

mask. The value will be compared to the Reference value, and if the |

|

values agree, then the function will be true for one scan, after that it ill |

|

be false. |

Status Bits: |

none |

Registers: none

Available on: Micrologix, PLC-5

SHIFT REGISTER

BSL, BSR |

|

|

|

||

|

|

A |

|

BSL |

|

|

|

||||

|

|

|

|

BIT SHIFT LEFT |

|

|

|

|

|||

|

|

|

|

File |

#B3:0 |

|

|

|

|

||

|

|

|

|

Control |

R6:0 |

|

|

|

|

Bit Address |

I:0.0/0 |

|

|

|

|||

|

|

|

|

Length |

6 |

Description: |

These functions will shift bits through left or right through a string of bits |

|

|

starting at #B3:0 with a length of 6 in the example above. As the bits |

|

|

shift the bit shifted out will be put in the UL bit. A new bit will be |

|

|

shifted into the vacant spot from the Bit Address. When the bits are |

|

|

shifted they are moved in the memory locations starting at file #B3:0. |

|

|

The two options available are: |

|

|

BSR - Bit Shift Right |

|

|

BSL - Bit Shift Left |

|

Status Bits: |

EN |

Enable - is on when the input to the function is on |

|

DN |

Done - is on when the shift operation is complete |

|

ER |

Error - indicates when an error has occurred |

|

UL |

Unload - the unloaded value is stored in this bit |

Registers: |

none |

|

Available on: Micrologix, PLC-5

page 463

FFL, FFU, LFL, LFU |

|

|

|||

|

|

A |

FFL |

|

|

|

|

||||

|

|

|

|

FIFO LOAD |

|

|

|

|

|

|

|

|

|

|

|

Source |

N7:0 |

|

|

|

|

||

|

|

|

|

FIFO |

N7:10 |

|

|

|

|

Control |

R6:0 |

|

|

|

|

Length |

10 |

|

|

|

|

Position |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

FFU |

|

|

|

|

|

|

FIFO UNLOAD |

|

|

|

|

|

|

|

|

|

|

|

FIFO |

N7:10 |

|

|

|

|

Dest |

N7:11 |

|

|

|

|

Control |

R6:0 |

|

|

|

|

Length |

10 |

|

|

|

|

||

|

|

|

|

Position |

0 |

|

|

|

|

|

|

Description: |

Stack instructions will take integer words and store them, and then allow |

|

|

later retrieval. The load instructions will store a value on the stack on a |

|

|

false to true input change. The Unload instructions will remove a |

|

|

value from that stack and store it in the Dest location. A Last On First |

|

|

Off stack will return the last value pushed on. A First On First Off |

|

|

stack will give the oldest value on the stack. If an attempt to load more |

|

|

than the stack length, the values will be ignored. The instructions |

|

|

available are: |

|

|

FFL - FIFO stack load |

|

|

FFU - FIFO stack unload |

|

|

LFL - LIFO stack load |

|

|

LFU - LIFO stack unload |

|

Status Bits: |

EN |

Enable - is on when the input to the function is on |

|

DN |

Done - is on when the shift operation is complete |

|

ER |

Error - indicates when an error has occurred |

|

UL |

Unload - the unloaded value is stored in this bit |

Registers: |

none |

|

Available on: Micrologix, PLC-5

SEQUENCERS

page 464

SQI - Sequencer Input |

|

|

|

|||

|

|

A |

|

SQI |

|

|

|

|

|

||||

|

|

|

|

SEQUENCER INPUT |

|

|

|

|

|

||||

|

|

|

|

File |

#N7:10 |

|

|

|

|

|

|||

|

|

|

|

Mask |

FF00 |

|

|

|

|

|

Source |

N7:0 |

|

|

|

|

||||

|

|

|

|

Control |

R6:0 |

|

|

|

|

|

Length |

7 |

|

|

|

|

|

Position |

0 |

|

Description: |

This will compare a source value to a set of values in a sequencer table. |

|||||

Status Bits: |

none |

Registers: none none

Available on: Micrologix, PLC-5

SQL - SeQuencer Load |

|

|

|||

|

|

A |

SQL |

|

|

|

|

||||

|

|

|

|

SEQUENCER LOAD |

|

|

|

|

|

||

|

|

|

|

File |

#N7:10 |

|

|

|

|

||

|

|

|

|

Source |

N7:0 |

|

|

|

|

Control |

R6:0 |

|

|

|

|

||

|

|

|

|

Length |

6 |

|

|

|

|

Position |

0 |

|

|

|

|

|

|

Description: |

When the input goes from false to true the value at the source will be |

|

|

loaded into the sequencer. After the position has reached the length |

|

|

the following values will be ignored, and the done bit will be set. |

|

Status Bits: |

EN |

Enable - will be true when the input to the function is true |

|

DN |

Done - will be set when the sequencer is fully loaded |

|

ER |

Error - will be set when there has been an error |

Registers: |

none |

|

Available on: Micrologix, PLC-5

page 465

SQO - SeQuencer Output |

|

|

|||

|

|

A |

SQO |

|

|

|

|

||||

|

|

|

|

SEQUENCER OUTPUT |

|

|

|

|

|

||

|

|

|

|

File |

#N7:10 |

|

|

|

|

||

|

|

|

|

Mask |

FF00 |

|

|

|

|

Dest |

N7:0 |

|

|

|

|

||

|

|

|

|

Control |

R6:0 |

|

|

|

|

Length |

6 |

|

|

|

|

Position |

0 |

|

|

|

|

|

|

Description: |

When the input goes from false to true the sequencer will output a value |

|

|

from a new position in the sequencer table. After the position has |

|

|

reached the length the sequencer will reset to position 1. Note that the |

|

|

first entry in the sequencer table will only be output the first time the |

|

|

function is un, or if reset has been used. |

|

Status Bits: |

EN |

Enable - will be true when the input to the function is true |

|

DN |

Done - will be set when the sequencer is fully loaded |

|

ER |

Error - will be set when there has been an error |

Registers: |

none |

|

Available on: Micrologix, PLC-5

PROGRAM CONTROL

page 466

FOR/NXTBRK |

|

|

|

|

|

|

A |

|

FOR |

|

|

|

|

|

|

||

|

|

|

FOR |

|

|

|

|

|

|

||

|

|

|

Label Number |

0 |

|

|

|

|

|||

|

|

|

Index |

N7:0 |

|

|

|

|

Initial Value |

0 |

|

|

|

|

Terminal Value |

10 |

|

|

|

|

Step Size |

2 |

|

|

B |

|

|

|

|

|

|

|

|

BRK |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

NXT |

|

|

|

|

|

NEXT |

|

|

|

|

|

|

|

|

|

|

|

Label Number |

0 |

|

|

|

|

|

|

|

Description:

Status Bits:

Registers:

This instruction will create a loop like traditional programming languages with a start and end value with a step size for each loop. Instructions between the FOR and NXT will be repeated. If the line with the BRK statement becomes true, the NXT command will be ignored.

none

none

Available on: Micrologix, PLC-5

JSR/SBR/RET

A

B

page 467

JSR

JUMP TO SUBROUTINE

Program File |

3 |

Input par |

N7:0 |

Input par |

N7:1 |

Return par |

N7:10 |

Return par |

N7:11 |

Return par |

N7:12 |

|

|

|

|

SBR |

|

SUBROUTINE |

|

Input par |

N7:20 |

Input par |

N7:21 |

|

|

C |

|

RET |

|

|

|

RETURN() |

|

|

|

||

|

|

Return par |

N7:22 |

|

|

||

|

|

Return par |

N7:23 |

|

|

Return par |

N7:24 |

|

|

|

|

Description: |

The JSR will jump to another program file and pass a list of arguments |

|

that can be a variable length. The first statement in the subroutine pro- |

|

gram file should be SBR to retrieve the arguments passed. The sub- |

|

routine will end with the RET command that will go back to where the |

|

JSR function was encountered. The RET function can return a vari- |

|

able number of arguments. |

Status Bits: |

none |

Registers: |

none |

Available on: Micrologix, PLC-5

PROCESS CONTROL AND MESSAGES

page 468

PID - |

|

|

|

||

|

|

A |

|

TON |

|

|

|

||||

|

|

|

|

TIMER ON DELAY |

|

|

|

|

|||

|

|

|

|

Timer |

T4:0 |

|

|

|

|

||

|

|

|

|

Time Base |

1.0 |

|

|

|

|

Preset |

10 |

|

|

|

|||

Description: |

|

Accum. |

0 |

||

cfvgfdg |

|

||||

Status Bits: |

cf |

cfvgfdg |

Registers: cf cfvgfdg

Available on: Micrologix, PLC-5

BLOCK TRANSFER

page 469

BTW |

|

|

|

||

|

|

A |

|

TON |

|

|

|

||||

|

|

|

|

TIMER ON DELAY |

|

|

|

|

|||

|

|

|

|

Timer |

T4:0 |

|

|

|

|

||

|

|

|

|

Time Base |

1.0 |

|

|

|

|

Preset |

10 |

|

|

|

|||

Description: |

|

Accum. |

0 |

||

cfvgfdg |

|

||||

Status Bits: |

cf |

cfvgfdg |

Registers: cf cfvgfdg

Available on: Micrologix, PLC-5

ASCII

page 470

AWT - |

|

|

|

||

|

|

A |

|

TON |

|

|

|

||||

|

|

|

|

TIMER ON DELAY |

|

|

|

|

|||

|

|

|

|

Timer |

T4:0 |

|

|

|

|

||

|

|

|

|

Time Base |

1.0 |

|

|

|

|

Preset |

10 |

|

|

|

|||

Description: |

|

Accum. |

0 |

||

cfvgfdg |

|

||||

Status Bits: |

cf |

cfvgfdg |

Registers: cf cfvgfdg

Available on: Micrologix, PLC-5