TsOS / Analog Devices / 03-АЦП

.pdf

a

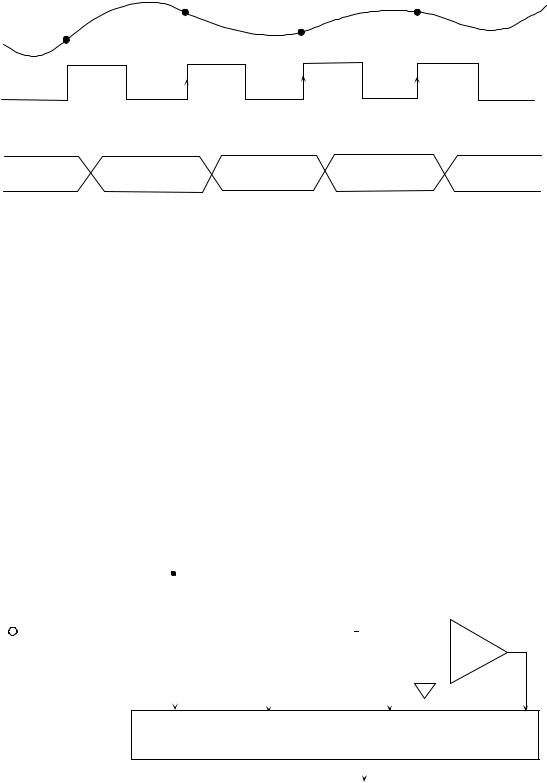

КОНВЕЙЕРНАЯ ЗАДЕРЖКА АЦП AD9220/9221/9223

АНАЛОГОВЫЙ

ВХОД

N |

N + 1 |

N + 2 |

N + 3 |

СИНХРОИМПУЛЬСЫ

ВЫХОДНЫЕ |

N - 3 |

N - 2 |

N - 1 |

N |

ДАННЫЕ |

Рис. 3.27

КАСКАДНЫЕ АЦП (BIT-PER-STAGE, ПОСЛЕДОВАТЕЛЬНЫЕ)

Для выполнения аналого-цифрового преобразования существуют различные архитектуры, использующие принципы последовательного преобразования. В действительности, конвейерный АЦП с одним разрядом на ступень и без коррекции ошибок может рассматриваться как АЦП последовательного счета. На рис.3.28 представлена общая концепция. УВХ хранит значение входного сигнала в течение цикла

преобразования. Существует N ступеней, каждая из которых имеет одноразрядный цифровой выход и выход остаточного сигнала. Остаточный сигнал каждой ступени является входным сигналом для следующей ступени. Как показано на рисунке, последний разряд является просто выходным сигналом компаратора.

ПОСЛЕДОВАТЕЛЬНЫЕ АЦП (BIT-PER-STAGE)

АНАЛОГОВЫЙ |

VREF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

ВХОД |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

УВХ |

|

|

КАСКАД |

R1 |

КАСКАД |

R2 |

|

|

|

|

|

|

КАСКАД |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

1 |

|

2 |

|

|

|

|

|

|

|

|

N–1 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

|

|

|

|

|

|

РАЗРЯД 1 |

|

РАЗРЯД 2 |

|

|

|

РАЗРЯД N-1 |

|

|

|

|

РАЗРЯД N |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЛОГИКА ДЕКОДИРОВАНИЯ И ВЫХОДНЫЕ РЕГИСТРЫ

N

N

Рис. 3.28

31

a

ОДИН КАСКАД ПОСЛЕДОВАТЕЛЬНОГО АЦП

|

|

|

+V R |

ВХОД |

ОСТАТОК |

|

ВХОД |

G = 2 |

Σ |

0 |

t |

|

|

||

+ |

|

-VR |

|

|

|

|

|

- |

|

|

+VR |

|

|

|

|

+VR |

-V R |

ОСТАТОК |

|

ПОЛОЖЕНИЕ КЛЮЧА |

|

|

|

ПОКАЗАНО ДЛЯ |

|

0 |

t |

ОТРИЦАТЕЛЬНОГО |

|

||

ВХОДНОГО СИГНАЛА |

|

|

|

ВЫХОД РАЗРЯДА |

-V R |

|

|

(ДВОИЧНЫЙ КОД) |

|

||

Рис. 3.29

На рис.3.29 показан каскад для выполнения одного однобитового преобразования. Каскад состоит из усилителя с коэффициентом усиления 2, компаратора и одноразрядного ЦАП. Предположим, что данный каскад являет собой первую ступень АЦП. Старший значащий разряд (MSB) – это разряд полярности входного сигнала, определяемой компаратором, который также управляет одноразрядным ЦАП. Выходной сигнал одноразрядного ЦАП суммируется с сигналом на выходе усилителя, который имеет коэффициент усиления 2. Результирующий остаточный сигнал подается на следующую ступень. Для лучшего понимания работы схемы на графике показан остаточный сигнал для случая входного линейно нарастающего пилообразного напряжения, размах которого соответствует полному диапазону АЦП от –VR до +VR. Обратите внимание, что полярность остаточного сигнала определяет значение выхода двоичного разряда следующей ступени.

Упрощенный 3-разрядный последовательный двоичный АЦП представлен на рис.3.30 Графики остаточных сигналов, соответствующие выходам различных ступеней, представлены на рис.3.31. Как и в предыдущем случае, рассматривается вариант входного линейного пилообразного напряжения, размах которого соответствует диапазону от –VR до +VR. Каждый остаточный выходной сигнал имеет разрывы, которые соответствуют точкам смены состояния компараторов и переключения ЦАП. Основной проблемой такой архитектуры является наличие разрывов (скачкообразных изменений) формы выходных остаточных сигналов различных ступеней. Необходимо предусмотреть адекватное время установки для окончания соответствующих переходных процессов во всех промежуточных ступенях и на входе компаратора последней ступени. Поэтому перспективы использования этой архитектуры для работы на высоких частотах дискретизации весьма неутешительны.

32

a

3-РАЗРЯДНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ АЦП С ДВОИЧНЫМ ВЫХОДОМ

|

|

±V R |

|

|

АНАЛОГОВЫЙ |

|

|

R1 КАСКАД |

R2 |

ВХОД |

УВХ |

КАСКАД |

||

|

|

1 |

2 |

+ |

|

|

РАЗРЯД 1 |

РАЗРЯД 2 |

- РАЗРЯД 3 |

|

|

|

ВЫХОДНОЙ РЕГИСТР |

|

3

3

Рис. 3.30

ФОРМА ВХОДНОГО И ОСТАТОЧНОГО СИГНАЛОВ 3-РАЗРЯДНОГО ПОСЛЕДОВАТЕЛЬНОГО АЦП

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VR |

||

ВХОД |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

-VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

R1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

-VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

R2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

-VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

ДВОИЧНЫЙ |

000 |

|

|

001 |

|

010 |

|

|

011 |

100 |

|

|

|

|

101 |

|

|

110 |

|

|

111 |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

КОД |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.31

Намного более совершенная архитектура АЦП последовательного счета, основанная на усилителях абсолютной величины (усилители модуля (magnitude amplifiers) или просто MagAmps™), была разработана Ф. Д. Вальдхауэром (F.D.Waldhauer), Приложение 21. Эта схема часто упоминается, как последовательная схема Грея (serial-Gray) (так как выходное кодирование осуществляется кодом Грея) или поворачивающий (folding) преобразователь (Приложения 22, 23, 24). Функциональная схема основной ступени вместе с ее передаточной функцией представлены на рис.3.32. Принимается, что входной сигнал ступени является линейным пилообразным напряжением, размах которого соответствует диапазону от –VR до +VR. Компаратор выявляет полярность входного сигнала и

33

a

формирует выходной разряд для данной ступени в виде кода Грея. Компаратор также определяет, должно ли общее усиление ступени быть равным +2 или -2. Опорное напряжение VR суммируется с выходом коммутатора для генерации остаточного сигнала, который подается на следующую ступень. Полярность остаточного сигнала определяет выходной разряд следующей ступени вновь в виде кода Грея. Передаточная функция поворачивающей (folding) ступени также представлена на рис.3.32.

ЭКВИВАЛЕНТНАЯ СХЕМА КАСКАДА MAGAMP

ВХОД |

VR |

ВХОД |

+VR |

G = +2 |

|

||

|

|

||

|

Σ ОСТАТОК |

0 |

t |

G = -2 |

ПОЛОЖЕНИЕ |

|

|

|

КОММУТАТОРА |

-VR |

|

|

ПОКАЗАНО ДЛЯ |

|

|

|

ОТРИЦАТЕЛЬНОГО |

|

+VR |

+ |

ВХОДНОГО |

|

|

|

СИГНАЛА |

ОСТАТОК |

|

- |

|

|

|

|

|

|

|

ВЫХОД РАЗРЯДА |

0 |

t |

|

|

|

||

|

(КОД ГРЭЯ) |

|

|

|

|

-VR |

|

Рис. 3.32

3-разрядный поворачивающий (folding) MagAmp АЦП представлен на рис.3.33, а диаграммы соответствующих остаточных сигналов изображены на рис.3.34. Как и в случае двоичного АЦП с пилообразной формой остаточных сигналов, значение кода Грея для следующей ступени определяется полярностью выходного остаточного сигнала предыдущей ступени. Полярность входного сигнала первой ступени определяет старший значащий разряд кода Грея; полярность выхода R1 — второй разряд кода Грея, полярность выхода R2 — третий разряд кода Грея. Обратите внимание, что, в отличие от двоичного импульсного АЦП, ни одна из ступеней данной архитектуры не дает перепада значения остаточного сигнала. Это делает данную архитектуру перспективной для работы на высоких частотах дискретизации.

Основой функционирования этой архитектуры на высоких скоростях является применение поворачивающей (folding) ступени. Ранние применения данной архитектуры (см. Приложения 22, 23, 24) для генерации поворачивающей функции передачи использовали дискретные операционные усилители с диодами в контуре обратной связи. Современные интегральные схемы реализуют требуемую функцию передачи, управляя коэффициентом усиления по току при разомкнутой обратной связи, что может быть реализовано с более высоким быстродействием. Полностью дифференциальные ступени (включая УВХ) также обеспечивают высокую скорость, более низкие искажения и дают поворачивающие (folding) ступени, обладающие 8-разрядной точностью, не требуя лазерной подстройки тонкопленочного резистора (см. Приложения 25, 26, 27).

34

a

БЛОК-СХЕМА 3-РАЗРЯДНОГО АЦП MagAmp™

|

±VR |

|

|

|

АНАЛОГОВЫЙ |

|

|

|

|

ВХОД |

КАСКАД 1 |

КАСКАД 2 |

|

|

УВХ |

|

|||

MAGAMP |

MAGAMP |

+ |

||

|

||||

|

РАЗРЯД 1 |

РАЗРЯД 2 |

- РАЗРЯД 3 |

РЕГИСТР КОДА ГРЕЯ

3

ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ДВОИЧНЫЙ КОД

3

3

ВЫХОДНОЙ РЕГИСТР

3

Рис. 3.33

ФОРМА ВХОДНОГО И ОСТАТОЧНЫХ СИГНАЛОВ 3-РАЗРЯДНОГО АЦП MAGAMP

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VR |

||

Вход 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

- VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

R1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

- VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

R2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- VR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

КОД |

000 |

001 |

011 |

|

010 |

|

|

110 |

|

|

111 |

101 |

100 |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ГРЭЯ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Рис. 3.34

Использование архитектура MagAmp может быть расширено до скоростей дискретизации, в которых ранее доминировали параллельные (flash) преобразователи. Двойной 8-

35

a

разрядный АЦП AD9288-100 с быстродействием 100 MSPS представлен на рис.3.35. Первые пять разрядов (код Грея) получены из пяти дифференциальных MagAmp ступеней. Дифференциальный остаточный выход пятой ступени MagAmp управляет 3- разрядным параллельным преобразователем вместо одиночного компаратора. Выходной код Грея пяти ступеней, построенных по архитектуре MagAmps, и выходной двоичный код 3-разрядного параллельного АЦП хранятся в регистре, затем все данные преобразуются в двоичный код и помещаются в выходной регистр.

ФУНКЦИОНАЛЬНАЯ СХЕМА ДВОЙНОГО 8-РАЗРЯДНОГО

100 MSPS АЦП AD9288-100

АНАЛОГ. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ВХОД |

УВХ |

|

MAGAMP |

|

MAGAMP |

|

MAGAMP |

|

MAGAMP |

|

MAGAMP |

|

3-РАЗР. |

|

|

|

|

|

|

|

|

|

ПАРАЛ. |

||||||

|

|

|||||||||||||

|

|

|

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

АЦП |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

РАЗР. |

РАЗР. |

РАЗР. |

РАЗР. |

РАЗР. |

3 |

|

1 |

2 |

3 |

4 |

5 |

|

ДИФФЕРЕН- |

ГРЕЯ |

ГРЕЯ |

ГРЕЯ |

ГРЕЯ |

ГРЕЯ |

ДВОИЧНЫЙ |

ЦИАЛЬНЫЕ |

|

|

РЕГИСТР |

|

|

|

ВЫХОДЫ |

|

|

5 |

|

|

|

РАЗРЯДОВ 1-5 |

|

|

|

|

|

|

ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ДВОИЧНЫЙ КОД |

|

|||||

|

3 |

|||||

|

|

|

5 |

|

|

|

|

|

|

ВЫХОДНОЙ РЕГИСТР |

|

|

|

8

Рис. 3.35

36

a

СПИСОК ЛИТЕРАТУРЫ

1.S. A. Jantzi, M. Snelgrove & P. F. Ferguson Jr., A 4th-Order Bandpass Sigma-Delta Modulator, IEEE Journal of Solid State Circuits,

Vol. 38, No. 3, March 1993, pp.282-291.

2.System Applications Guide, Analog Devices, Inc., 1993, Section 14.

3.Mixed Signal Design Seminar, Analog Devices, Inc., 1991, Section 6.

4.AD77XX-Series Data Sheets, Analog Devices, http://www.analog.com.

5.Linear Design Seminar, Analog Devices, Inc., 1995, Section 8.

6.J. Dattorro, A. Charpentier, D. Andreas, The Implementation of a One-

Stage Multirate 64:1 FIR Decimator for use in One-Bit Sigma-Delta A/D Applications,

AES 7th International Conference, May 1989.

7.W.L. Lee and C.G. Sodini, A Topology for Higher-Order Interpolative Coders, ISCAS PROC. 1987.

8.P.F. Ferguson, Jr., A. Ganesan and R. W. Adams, One Bit Higher Order Sigma-Delta A/D Converters, ISCAS PROC. 1990, Vol. 2, pp. 890-893.

9.R. Koch, B. Heise, F. Eckbauer, E. Engelhardt, J. Fisher, and F. Parzefall,

A 12-bit Sigma-Delta Analog-to-Digital Converter with a 15MHz Clock Rate, IEEE Journal of Solid-State Circuits, Vol. SC-21, No. 6, December 1986.

10.Wai Laing Lee, A Novel Higher Order Interpolative Modulator Topology for High Resolution Oversampling A/D Converters, MIT Masters Thesis, June 1987.

11.D. R. Welland, B. P. Del Signore and E. J. Swanson, A Stereo 16-Bit Delta-Sigma A/D Converter for Digital Audio, J. Audio Engineering Society, Vol. 37, No. 6, June 1989, pp. 476-485.

12.R. W. Adams, Design and Implementation of an Audio 18-Bit Analog- to-Digital Converter Using Oversampling Techniques, J. Audio Engineering Society, Vol. 34, March 1986, pp. 153-166.

13.B. Boser and Bruce Wooley, The Design of Sigma-Delta Modulation Analog-to-Digital Converters, IEEE Journal of Solid-State Circuits, Vol. 23, No. 6, December 1988, pp. 1298-1308.

14.Y. Matsuya, et. al., A 16-Bit Oversampling A/D Conversion Technology Using Triple-Integration Noise Shaping, IEEE Journal of Solid-State Circuits, Vol. SC-22, No. 6, December 1987, pp. 921-929.

15.Y. Matsuya, et. al., A 17-Bit Oversampling D/A Conversion Technology Using Multistage Noise Shaping, IEEE Journal of Solid-State Circuits, Vol. 24, No. 4, August 1989, pp. 969-975.

37

a

16.P. Ferguson, Jr., A. Ganesan, R. Adams, et. al., An 18-Bit 20-kHz Dual Sigma-Delta A/D Converter, ISSCC Digest of Technical Papers, February 1991.

17.Steven Harris, The Effects of Sampling Clock Jitter on Nyquist Sampling

Analog-to-Digital Converters and on Oversampling Delta Sigma ADCs,

Audio Engineering Society Reprint 2844 (F-4), October, 1989.

18.Max W. Hauser, Principles of Oversampling A/D Conversion, Journal Audio Engineering Society, Vol. 39, No. 1/2, January/February 1991, pp. 3-26.

19.Daniel H. Sheingold, Analog-Digital Conversion Handbook, Third Edition, Prentice-Hall, 1986.

20.Chuck Lane, A 10-bit 60MSPS Flash ADC, Proceedings of the 1989 Bipolar Circuits and Technology Meeting, IEEE Catalog No. 89CH2771-4, September 1989, pp. 44-47.

21.F.D. Waldhauer, Analog to Digital Converter, U.S. Patent 3-187-325, 1965.

22.J.O. Edson and H.H. Henning, Broadband Codecs for an Experimental 224Mb/s PCM Terminal, Bell System Technical Journal, 44, November 1965, pp. 1887-1940.

23.J.S. Mayo, Experimental 224Mb/s PCM Terminals, Bell System Technical Journal, 44, November 1965, pp. 1813-1941.

24.Hermann Schmid, Electronic Analog/Digital Conversions, Van Nostrand Reinhold Company, New York, 1970.

25.Carl Moreland, An 8-bit 150MSPS Serial ADC, 1995 ISSCC Digest of Technical Papers, Vol. 38, p. 272.

26.Roy Gosser and Frank Murden, A 12-bit 50MSPS Two-Stage A/D Converter, 1995 ISSCC Digest of Technical Papers, p. 278.

27.Carl Moreland, An Analog-to-Digital Converter Using SerialRipple Architecture, Masters' Thesis, Florida State University College of Engineering, Department of Electrical Engineering, 1995.

28.Practical Analog Design Techniques, Analog Devices, 1995, Chapter 4, 5, and 8.

29.Linear Design Seminar, Analog Devices, 1995, Chapter 4, 5.

30.System Applications Guide, Analog Devices, 1993, Chapter 12, 13, 15,16.

31.Amplifier Applications Guide, Analog Devices, 1992, Chapter 7.

38

a

32.Walt Kester, Drive Circuitry is Critical to High-Speed Sampling ADCs,

Electronic Design Special Analog Issue, Nov. 7, 1994, pp. 43-50.

33.Walt Kester, Basic Characteristics Distinguish Sampling A/D Converters,

EDN, Sept. 3, 1992, pp. 135-144.

34.Walt Kester, Peripheral Circuits Can Make or Break Sampling ADC Systems, EDN, Oct. 1, 1992, pp. 97-105.

35.Walt Kester, Layout, Grounding, and Filtering Complete Sampling ADC System, EDN, Oct. 15, 1992, pp. 127-134.

36.High Speed Design Techniques, Analog Devices, 1996, Chapter 4, 5.

39