- •5. Последовательностные цифровые устройства

- •5.1.1. Rs –триггер

- •5.1.2. D –триггер

- •5.1.3. Jk –триггер

- •5.1.4. T –триггер

- •5.1.5. Триггер Шмитта

- •5.2. Цифровые счетчики импульсов и делители частоты следования

- •5.2.1. Двоичные счетчики

- •5.2.2. Недвоичные счетчики

- •5.3. Регистры

- •Контрольные вопросы и задания

5.1.5. Триггер Шмитта

При передаче цифровых сигналов по линии связи из-за ограниченной полосы пропускания происходит затягивание фронтов импульсов, что может сделать их непригодными для нормального восприятия логическими элементами. С целью улучшения формы импульсов широко используются специальные формирователи – триггеры Шмитта. В них вводится положительная обратная связь, за счет которой такой элемент обладает гистерезисом – зоной нечувствительности.

На рис. 5.14,а приведена типовая переходная характеристика триггера Шмитта, на которой показаны границы зоны нечувствительности – пороговые напряжения UП1 и UП2. На этом же рисунке приведен график, объясняющий восстановление формы сигнала.

Когда входной

сигнал в момент времени

![]() станетUвх(t1)UП1

триггер

переключится из 1(

станетUвх(t1)UП1

триггер

переключится из 1(![]() )

в 0(

)

в 0(![]() ).

Обратное переключение произойдет приUвх(t2)UП2.

).

Обратное переключение произойдет приUвх(t2)UП2.

Обозначение триггера Шмита на схемах приведено на рис. 5.14,б.

а б

Рис. 5.14. Триггер Шмитта:

а– переходные характеристики триггера Шмитта; б– условное изображение

5.2. Цифровые счетчики импульсов и делители частоты следования

5.2.1. Двоичные счетчики

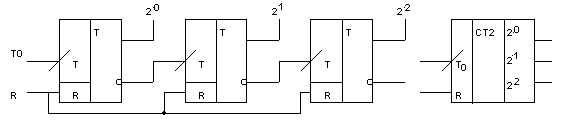

Двоичные счетчики –это последовательностные устройства, отображающие в выходном двоичном коде число поступивших на его вход импульсов. Двоичные счетчики строятся на n последовательно соединенных Т-триггерах, поэтому число всевозможных сочетаний состояний триггеров составит K=2n. Это значит, что счетчик может “сосчитать” 2n - 1 входных сигналов. Число K отражает информационную емкость двоичного счетчика и называется модулем счета. Первый импульс, пришедший после “заполнения” счетчика (когда исчерпаны все возможные состояния), автоматически сбрасывает счетчик в исходное нулевое состояние. Рассмотрим работу трехразрядного двоичного счетчика с помощью временных диаграмм (см. рис. 5.15).

При рассмотрении диаграммы необходимо обратить внимание на то, что счетный вход каждого последующего триггера подключен к инвертирующему выходу предыдущего. Это означает, что положительный перепад на входе триггера, по которому он срабатывает, происходит при отрицательном перепаде по основному выходу предыдущего триггера. В диаграммах учтены задержки t3 (для простоты принятые одинаковыми), вызванные конечным временем переходного процесса триггера. По диаграммам легко убедиться, что значение двоичного кода на основных

а б

в

Рис. 5.15. Схема трехразрядного асинхронного суммирующего двоичного счетчика:

а, б – условное обозначение; в– временные диаграммы

выходах

триггеров соответствует числу пришедших

импульсов (см. на диаграммном состоянии

после 5-го и 7-го импульсов). С приходом

7-го импульса информационная емкость

счетчика исчерпывается и 8-й импульс

приводит к последовательному сбросу в

нулевое состояние всех триггеров,

который заканчивается через время

![]() ,

равное сумме времен задержки каждого

триггера. Это обстоятельство ограничивает

частоту импульсов, т. е. скорость счета,

т. к. необходимо выполнить условие

,

равное сумме времен задержки каждого

триггера. Это обстоятельство ограничивает

частоту импульсов, т. е. скорость счета,

т. к. необходимо выполнить условие

![]() .

.

Такой счетчик называется асинхронным. С приходом каждого импульса число, отображаемое двоичным кодом, увеличивается на единицу, поэтому такой счетчик называется суммирующим.

Хорошо видно, что период следования импульсов с прямого выхода каждого последующего триггера в 2 раза больше, чем у предыдущего. Если снимать информацию, например, с выхода второго триггера, то частота следования импульса здесь будет в 4 раза ниже, чем у входных импульсов, т. е. счетчик может выполнять роль делителя частоты входных импульсов.

Ограничение скорости счета, вызванного у асинхронного счетчика последовательным переключением триггеров можно устранить, если осуществлять одновременное переключение триггеров, которое реализуется в счетчиках с параллельным переносом (рис. 5.16).

В это схеме входы J и K объединены и когда J=K=1 JK-триггер работает как Т-триггер, а когда J=K=0 – находится в режиме хранения. С помощью элемента И осуществляется перенос информации в старший разряд. Быстродействие повышается за счет того, что с приходом входного импульса одновременно срабатывают все триггеры.

Рис. 5.16. Счетчик с параллельным переносом

Если вход последующего триггера (см. рис. 5.15) соединить с прямым выходом предыдущего, то такой счетчик становится вычитающим: число, записанное в виде исходного кода, будет с приходом каждого входного импульса уменьшаться на 1. Возможна реализация реверсивного счетчика, работающего по внешней команде , или в режиме суммирования, или в режиме вычитания.