ТСвИС / книга.(уч.пособие) Архитектура компьютера. Э.Танненбаум

.pdf

Память 163

соединить полученный сигнал с изначальным сигналом с помощью логической функции И (см. рис. 3.20, в, сигнал С),

Память

Память является необходимым компонентом любого компьютера. Без памяти не было бы компьютеров, по крайней мере таких, какие есть сейчас. Память используется как для хранения команд, которые нужно выполнить, так и данных. В следующих разделах мы рассмотрим основные компоненты памяти, начиная с уровня вентилей. Мы увидим, как они работают и как из них можно получить память большой емкости.

Защелки

Чтобы создать один бит памяти, нам нужна схема, которая каким-то образом «запоминает» предыдущие входные значения. Такую схему можно сконструировать из двух вентилей НЕ-ИЛИ, как показано на рис. 3.21, а. Аналогичные схемы можно построить из вентилей НЕ-И. Мы не будем упоминать эти схемы в дальнейшем, поскольку они, по существу, идентичны схемам с вентилями НЕ-ИЛИ.

А |

В |

НЕ- |

|

ИЛИ |

|||

|

|

||

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Q

Рис. 3 . 21 . Защелка НЕ-ИЛИ в состоянии 0 (а); защелка НЕ-ИЛИ в состоянии 1 (б); таблица истинности для функции НЕ-ИЛИ (Й)

Схема, изображенная на рис. 3.21, а, называется SR-защелкой. У нее есть два входа: S (setting — установка) и R (resetting — сброс). У нее также есть два комплементарных1 (дополнительных) выхода: Q и Q. В отличие от комбинационной схемы, выходные сигналы защелки не определяются текущими входными сигналами.

Чтобы увидеть, как это осуществляется, предположим, что S=0 и R=0 (вообще они равны 0 большую часть времени). Чтобы провести доказательство, предположим также, что Q=0. Так как Q возвращается в верхний вентиль НЕ-ИЛИ и оба входа этого вентиля равны 0, то его выход, Q, равен 1. Единица возвращается в нижний вентиль, у которого в итоге один вход равен 0, адругой — 1, а на выходе получается Q=0. Такое положение вещей, по крайней мере, состоятельно (рис. 3.21, а).

От англ. complementary — дополняющий. — Примеч. пер.

1 6 4 Глава 3. Цифровой логический уровень

Атеперь давайте представим, что Q=l, a R и S все еще равны 0. Верхний вентиль имеет входы 0 и 1 и выход Q (то есть 0), который возвращается в нижний вентиль. Такое положение вещей, изображенное на рис. 3.21, б, также состоятельно. Положение, когда оба выхода равны 0, несостоятельно, поскольку в этом случае оба вентиля имели бы на входе два нуля, что привело бы к единице на выходе,

ане к нулю. Точно так же невозможно иметь оба выхода равных 1, поскольку это привело бы к входным сигналам 0 и 1, что вызывает на выходе 0, ане 1. Наш вывод прост: при R=S=0 защелка имеет два стабильных состояния, которые мы будем называть 0 и 1 в зависимости от Q.

Асейчас давайте рассмотрим действие входных сигналов на состояние защелки. Предположим, что S принимает значение 1, в то время как Q=0. Тогда входные сигналы верхнего вентиля будут 1 и 0, что приведет к выходному сигналу Q=0. Это изменение делает оба входа в нижний вентиль равными 0 и, следовательно, выходной сигнал равным 1. Таким образом, установка S на значение 1 переключает состояние с 0 на 1. Установка R на значение 1, когда защелка находится в состоянии 0, не вызывается изменений, поскольку выход нижнего вентиля НЕ-ИЛИ равен 0 и для входов 10, и для входов 11.

Используя подобную аргументацию, легко увидеть, что установка S на значение 1 при состоянии защелки 1 (то есть при Q=l) не вызывает изменений, но установка R на значение 1 приводит к изменению состояния защелки. Таким образом, если S принимает значение 1, то Q будет равно 1 независимо от предыдущего состояния защелки. Сходным образом переход R на значение 1 вызывает Q=0. Схема «запоминает», какой сигнал был в последний раз: S или R. Используя это свойство, мы можем конструировать компьютерную память.

Синхронные SR-защелки

Часто бывает удобно сделать так, чтобы защелка меняла состояние только в определенные моменты. Чтобы достичь этой цели, мы немного изменили основную схему и получили синхронную SR-защелку (рис. 3.22).

Тактовый п генератор

Рис. 3.22. Синхронная SR-защелка

Эта схема имеет дополнительный синхронизирующий вход, который обычно равен 0. Если этот вход равен 0, то оба выхода вентилей И равны 0 независимо от S и R, и защелка не меняет состояние. Когда значение синхронизирующего входа равно 1, действие вентилей И исчезает и состояние защелки становится зависимым от S и R. Для обозначения того факта, что синхронизирующий вход равен 1

Память 165

(то есть состояние схемы зависит от значений S и R), часто используется термин

стробировать.

До сих пор мы скрывали, что происходит, если S=R=1. И по понятным причинам: когда и R, и S в конце концов возвращаются к 0, схема становится недетерминированной. Единственное состоятельное положение при S=R=1 — это Q=Q=0, но как только оба входа возвращаются к 0, защелка должна перейти в одно из двух стабильных состояний. Если один из входов принимает значение 0 раньше, чем другой, оставшийся в состоянии 1 «побеждает», потому что когда один из входов равен 1, он управляет состоянием защелки. Если оба входа переходят к 0 одновременно (что маловероятно), защелка переходит в одно из своих состояний наугад.

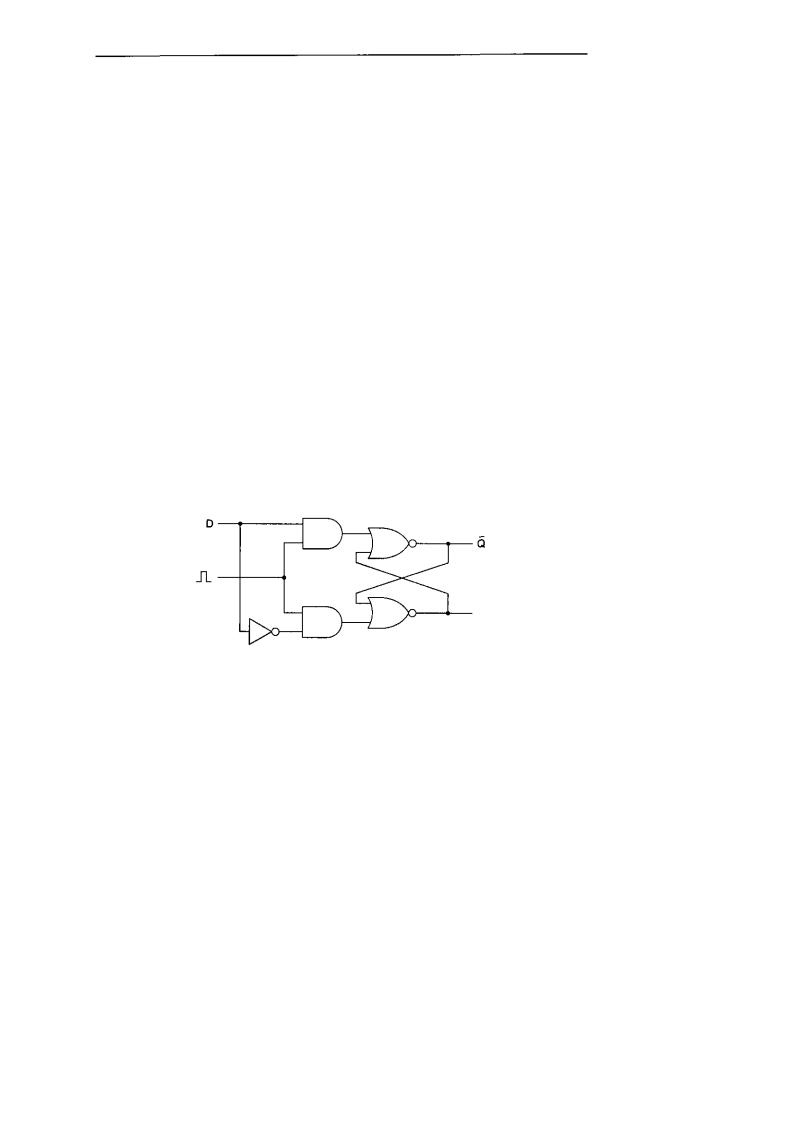

СинхронныеD-защелки

Чтобы разрешить неопределенность SR-защелки (неопределенность возникает

вслучае, если S=R=1), нужно предотвратить появление подобной неопределенности. На рис. 3.23 изображена схема защелки только с одним входом D. Так как входной сигнал в нижний вентиль И всегда является обратным кодом входного сигнала в верхний вентиль И, ситуация, когда оба входа равны 1, никогда не возникает. Когда D=l и синхронизирующий вход равен 1, защелка переходит в состояние Q,= l. Когда D=0 и синхронизирующий вход равен 1, защелка переходит

всостояние Q=0. Другими словами, когда синхронизирующий вход равен 1, текущее значение D отбирается и сохраняется в защелке. Такая схема, которая называется синхронной D-защелкой, представляет собой память объемом 1 бит. Значение, которое было сохранено, всегда доступно на выходе Q. Чтобы загрузить в память текущее значение D, нужно пустить положительный импульс по линии синхронизирующего сигнала.

Q

Рис.3.23.СинхроннаяD-защелка

Такая схема требует наличия 11 транзисторов. Более сложные схемы могут хранить 1 бит, имея всего 6 транзисторов. На практике обычно используются последние.

Триггеры (flip-flops)

Многие схемы выбирают значение на определенной линии в определенный момент времени и запоминают его. В такой схеме, которая называется триггером,

166 |

Глава 3. Цифровой логический уровень |

переход состояния происходит не тогда, когда синхронизирующий сигнал равен 1, а во время перехода синхронизирующего сигнала с 0 на 1 (нарастающий фронт) или с 1 на 0 (задний фронт). Следовательно, длина синхронизирующего импульса не имеет значения, поскольку переходы происходят быстро.

Подчеркнем еще раз различие между триггером и защелкой. Триггер запускается фронтом сигнала, а защелка запускается уровнем сигнала. Обратите внимание, что в литературе эти термины часто путаются. Многие авторы используют термин «триггер», когда речь идет о защелке, и наоборот1.

Существует несколько подходов к разработке триггеров. Например, если бы существовал способ генерирования очень короткого импульса на нарастающем фронте синхронизирующего сигнала, этот импульс можно было бы подавать в D-за- щелку. В действительности такой способ существует. Соответствующая схема показана на рис. 3.24, а.

ЬИс

Время

Рис. 3.24. Генератор импульса (а); временная диаграмма для четырехточекнасхеме(б)

На первый взгляд может показаться, что выход вентиля И всегда будет нулевым, поскольку функция И от любого сигнала с его инверсией дает 0, но на самом деле ситуация несколько более тонкая. При прохождении сигнала через инвертор происходит небольшая, но все-таки не нулевая задержка. Данная схема работает именно благодаря этой задержке. Предположим, что мы измеряем напряжение в четырех точках а, Ь, с и d. Входовый сигнал в точке а представляет собой длинный синхронизирующий импульс (см. нижний график на рис. 3.24, б). Сигнал в точке b показан над ним. Отметим, что этот сигнал инвертирован и подается с некоторой

1 В отечественной литературе термин «защелка* (latch) не используется, i оворят о триггерах, Однако при этом вводится понятие Т-триггера, который здесь называется настоящим триггером. — Примеч. научн.ред

Память 167

задержкой. Время задержки зависит от типа инвертора и обычно составляет несколько наносекунд.

Сигнал в точке с тоже подается с задержкой, но эта задержка обусловлена только временем прохождения сигнала (со скоростью света). Если физическое расстояние между а и с, например, 20 микрон, тогда задержка на распространение сигнала составляет 0,0001 не, что, конечно, незначительно по сравнению со временем, которое требуется на прохождение сигнала через инвертор. Таким образом, сигнал в точке с практически идентичен сигналу в точке а.

Когда входные сигналы b и с подвергаются операции И, в результате получается короткий импульс, длина которого (Д) равна вентильной задержке инвертора (обычно 5 не и меньше). Выходной сигнал вентиля И — данный импульс, сдвинутый из-за задержки вентиля И (см. верхний график на рис. 3 24, б). Этот временной сдвиг означает только то, что D-защелка активизируется с определенной задержкой после нарастающего фронта синхронизирующего импульса Он никак не влияет на длину импульса. В памяти со временем цикла в 50 не импульс в 5 не (который сообщает, когда нужно выбирать линию D) достаточно короткий, и в этом случае полная схема может быть такой, какая изображена на рис. 3.25. Следует упомянуть, что такая схема триггера проста для понимания, но на практике обычно используются более сложные триггеры.

Q

Рис. 3.25. D-триггер

Стандартные изображения защелок и триггеров показаны на рис 3 26 На рис.3 26, а изображена защелка, состояние которой загружается тогда, когда синхронизирующий сигнал СК (от слова clock) равен 1, в противоположность защелке, изображенной на рис. 3 26,6, у которой синхронизирующий сигнал обычно равен 1, но переходит на 0, чтобы загрузить состояние из D. На рис. 3.26, виг изображены триггеры. То, что это триггеры, а не защелки, показано с помощью уголка при синхронизирующем входе. Триггер на рис. 3.26, в изменяет состояние на возрастающем фронте синхронизирующего импульса (переход от 0 к 1), тогда как триггер на рис 3 26, г изменяет состояние на заднем фронте (переход от 0 к 1). Многие (хотя не все) защелки и триггеры также имеют выход £У, а у некоторых есть два дополнительных входа. Set (установка) или Preset (предварительная установка) и Reset (сброс) или Clear (очистка). Первый вход (Set или Preset) устанавливает Q=l, а второй

(Reset или Clear) — Q=0.

168 Глава3. Цифровойлогическийуровень

б |

в |

Рис.3.26.D-защелкииD-триггеры

Регистры

Существуют различные конфигурации триггеров. На рисунке 3.27, а изображена схема, содержащая два независимых D-триггера с сигналами предварительной установки и очистки. Хотя эти два триггера находятся на одной микросхеме с 14 выводами, они не связаны между собой. Совершенно по-другому устроен восьмиразрядный триггер, изображенный на рис. 3.27, б. Здесь, в отличие от предыдущей схемы, у восьми триггеров нет выхода (J и линий предварительной установки и все синхронизирующие линии связаны вместе и управляются выводом 11. Сами триггеры того же типа, что на рис. 3.26, г, но инвертирующие входы аннулируются инвертором, связанным с выводом 11, поэтому триггеры запускаются при переходе от 0 к 1. Все восемь сигналов очистки также объединены, поэтому когда вывод 1 переходит в состояние 0, все триггеры также переходят в состояние 0. Если вам не понятно, почему вывод 11 инвертируется на входе, а затем инвертируется снова при каждом сигнале СК, то ответ прост: входной сигнал не имеет достаточной мощности, чтобы запустить все восемь триггеров; входной инвертор на самом деле используется в качестве усилителя.

Одна из причин объединения линий синхронизации и линий очистки в микросхеме на рис. 3.27, б ~ экономия выводов. С другой стороны, микросхема данной конфигурации несколько отличается от восьми несвязанных триггеров. Эта микросхема используется в качестве одного 8-разрядного регистра. Две такие микросхемы могут работать параллельно, образуя 16-разрядный регистр. Для этого нужно связать соответствующие выводы 1 и 11. Регистры и их применение мы рассмотрим более подробно в главе 4.

Организация памяти

Хотя мы и совершили переход от простой памяти в 1 бит (см. рис. 3.23) к 8-разряд- ной памяти (см. рис. 3.27, б), чтобы построить память большого объема, требуется другой способ организации, при котором можно обращаться к отдельным словам. Пример организации памяти, которая удовлетворяет этому критерию, показан на рис. 3.28. Эта память содержит четыре 3-битных слова. Каждая операция считывает или записывает целое 3-битное слово. Хотя общий объем памяти (12 битов) ненамного больше, чем у нашего 8-разрядного триггера, такая память требует меньшего количества выводов, и, что особенно важно, подобная организация применима при построении памяти большого объема.

|

|

|

|

|

|

Память |

169 |

v;с |

|

1:i |

|

10 |

9 |

8 |

|

14 |

13 |

11 |

|

||||

|

|

|

|

|

I |

|

|

|

CLR |

|

|

CLR |

|

|

|

|

D |

Q |

|

D |

Q |

|

|

|

>СК |

Q |

|

>CK |

Q |

|

|

|

PRY |

|

|

PRf |

|

|

|

|

~l |

3 |

|

|

|

|

|

1 |

2 |

4 |

5 |

6 |

7 |

|

GND

GND

Рис. 3.27. Два D-триггера (а); восьмиразрядный триггер (б)

Хотя структура памяти, изображенная на рис. 3.28, может на первый взгляд показаться сложной, на самом деле она очень проста благодаря своей регулярной структуре. Она содержит 8 входных линий (3 входа для данных — 10, Ь и 12; 2 входа

170 |

Глава3. Цифровойлогическийуровень |

для адресов — Ао и А,; 3 входадля управления — CS (Chip Select — выбор элемента памяти), RD (для различия между считыванием и записью) и ОЕ (Output Enable — разрешение выдачи выходных сигналов)) и 3 выходные линии для данных — Оо, Ot и ОгТакую память в принципе можно поместить в корпус с 14 выводами (включая питание и «землю»), а 8-разрядный триггер требует наличия 20 выводов.

Входныеданные

Вентиль |—

|

записи |

Слово 0 |

|

|

|

|

Линия |

|

|

выборки |

|

|

слова О |

Слово 1 |

|

|

|

|

-7 |

|

i |

Линия |

|

выборки |

|

|

Ао |

слова 1 |

|

|

Линия |

|

|

выборки |

|

|

слова 2 |

|

|

CS-RD |

|

CS |

|

|

RD |

|

|

ОЕ

Разрешение выхода = CS • RD • ОЕ

Рис.3.28.Логическаяблок-схемадляпамяти4X3. Каждыйрядпредставляетодно из 3-битных слов. При операции считывания и записи всегда считывается

или записывается целое слово

Чтобы выбрать микросхему памяти, внешняя логика должна установить CS на 1, а также установить RD на 1 для чтения и на 0 для записи. Две адресные линии должны указывать, какое из четырех 3-битных слов нужно считывать или записывать. При операции считывания входные линии для данных не используются.

Память 171

Выбирается слово и помещается на выходные линии для данных. При операции записи биты, находящиеся на входных линиях для данных, загружаются в выбранное слово памяти; выходные линии при этом не используются.

А теперь давайте посмотрим, как работает память, изображенная на рис. 3.28. Четыре вентиля И для выбора слов в левой части схемы формируют декодер. Входные инверторы расположены так, что каждый вентиль запускается определенным адресом. Каждый вентиль приводит в действие линию выбора слов (для слов 0, 1, 2 и 3). Когдамикросхемадолжна производитьзапись, вертикальнаялиния CS•1Ш получает значение 1, запуская один из 4 вентилей записи. Выбор вентиля зависит от того, какая именно линия выбора слов равна 1. Выходной сигнал вентиля записи приводит в действие все сигналы СК для выбранного слова, загружая входные данные в триггеры для этого слова. Запись производится только в том случае, если CS равно 1, a RD равно 0, при этом записывается только слово, выбранное адресами Ао и Аь остальные слова не меняются

Процесс считывания сходен с процессом записи. Декодирование адреса происходит точно так же, как и при записи. Но в данном случае линия CS • RD принимает значение 0, поэтому все вентили записи блокируются и ни один из триггеров не меняется. Вместо этого линия выбора слов запускает вентили И, связанные с битами Q выбранного слова Таким образом, выбранное слово передает свои данные в четырехвходовые вентили ИЛИ, расположенные в нижней части схемы, а остальные три слова выдают 0. Следовательно, выход вентилей ИЛИ идентичен значению, сохраненному в данном слове. Остальные три слова никак не влияют на выходные данные.

Мы могли бы разработать схему, в которой три вентиля ИЛИ соединялись бы с тремя линиями вывода данных, но это вызвало бы некоторые проблемы. Мы рассматривали линии ввода данных и линии вывода данных как разные линии На практике же используются одни и те же линии. Если бы мы связали вентили ИЛИ с линиями вывода данных, микросхема пыталась бы выводить данные (то есть задавать каждой линии определенную величину) даже в процессе записи, мешая нормальному вводу данных. По этой причине желательно каким-то образом соединять вентили ИЛИ с линиями вывода данных при считывании и полностью разъединять их при записи. Все, что нам нужно, — электронный переключатель, который может устанавливать и разрушать связь за несколько наносекунд.

К счастью, такие переключатели существуют На рис. 3 29, а показано символическое изображение так называемого буферного элемента без инверсии. Он содержит вход для данных, выход для данных и вход управления. Когда вход управления равен 1, буферный элемент работает как провод (см. рис. 3.29, б). Когда вход управления равен 0, буферный элемент работает как разомкнутая цепь (см рис. 3.29, б), как будто кто-то отрезал выход для данных от остальной части схемы кусачками. Соединение может быть восстановлено за несколько наносекунд, если сделать сигнал управления равным 1.

На рис. 3.29, г показан буферный элемент с инверсией, который действует как обычный инвертор, когда сигнал управления равен 1, и отделяет выход от остальной части схемы, когда сигнал управления равен 0. Оба буферных элемента представляют собой устройства с тремя состояниями, поскольку они могут выдавать 0,1 или вообще не выдавать сигнала (в случае с разомкнутой цепью). Буфер-

172 Глава 3. Цифровой логический уровень

ные элементы, кроме того, усиливают сигналы, поэтому они могут справляться с большим количеством сигналов одновременно. Иногда они используются в схемах именно по этой причине, даже если их свойства переключателя не нужны.

Зходные Выходные данные [\ данные

И>-—

Управление

а |

б |

Рис. 3.29. Буферный элемент без инверсии (а); действие буферного элемента без инверсии, когда сигнал управления равен 1 (б); действие буферного элемента без инверсии, когда сигнал управления равен 0 {s); буферный элемент с инверсией (г)

Сейчас уже должно быть понятно, для чего нужны три буферных элемента без инверсии на линиях вывода данных. Когда CS, RD и ОЕ все равны 1, то сигнал разрешения выдачи выходных данных также равен 1, в результате чего запускаются буферные элементы и слово помещается на выходные линии. Когда один из сигналов CS, RD и ОЕ равен 0, выходы отсоединяются от остальной части схемы.

Микросхемы памяти

Преимущество памяти, изображенной на рис. 3.28, состоит в том, что подобная структура применима при разработке памяти большого объема. Мы нарисовали схему 4x3 (для 4 слов по 3 бита каждое). Чтобы расширить ее до размеров 4x8, нужно добавить еще 5 колонок триггеров по 4 триггера в каждой, а также 5 входных и 5 выходных линий. Чтобы перейти от размера 4x3 к размеру 8x3, мы должны добавить еще четыре ряда триггеров по три триггера в каждом, а также адресную линию А2. При такой структуре число слов в памяти должно быть степенью двойки для максимальной эффективности, а число битов в слове может быть любым.

Поскольку технология изготовления интегральных схем хорошо подходит для производства микросхем с внутренней структурой повторяемой плоской поверхности, микросхемы памяти являются идеальным применением для этого. С развитием технологии число битов, которое можно вместить в одной микросхеме, постоянно увеличивается, обычно в два раза каждые 18 месяцев (закон Мура). С появлением больших микросхем маленькие микросхемы не всегда устаревают из-за компромиссовмеждупреимуществамиемкости,скорости,мощности, ценыисопряжения. Обычно самые большие современные микросхемы пользуются огромным спросом и, следовательно, стоят гораздо дороже за 1 бит, чем микросхемы небольшого размера.

При любом объеме памяти существует несколько различных способов организации микросхемы. На рис. 3.30 показаны две возможные структуры микросхемы в 4 Мбит: 512 Кх8 и 4096 Kxl. (Размеры микросхем памяти обычно даются в битах, а не в байтах, поэтому здесь мы будем придерживаться этого соглашения.) На рис. 3.30, а можно видеть 19 адресных линий для обращения к одному из 219 байтов и 8 линий данных для загрузки или хранения выбранного байта.