Масленников Основы шемотехники електронных цепей

.pdf

Рис. 4.1. Схема ЛЭ серии 564

В ИМС, выполненных по технологии КМОП, в качестве базового элемента используются ключевые схемы, построенные на комплементарных МОП-транзисторах. На рис. 4.1 приведена схема логического элемента И-НЕ. Эта схема состоит из двух пар ключей на МДП транзисторах с индуцированным каналом разной проводимости VT1, VT3 и VT2, VT4. При подаче сигналов X1 X 2 1

ключи на транзисторах VT1 и VT2 закрываются, а ключи на транзисторах VT3 и VT4 открываются, т.е. в них возникают каналы с малым сопротивлением. В результате на выходе микросхемы устанавливается логический «0». При подаче на какой-нибудь вход (например, X 2 ) низкого уровня потенциала X 2 0 – VT1 откры-

вается, а VT3 закрывается и на выходе – логическая «1». Таким образом, этот элемент выполняет логическую операцию И-НЕ. В работе исследуется ЛЭ 564 серии.

Параметры ЛЭ, выполненные на КМОП-структурах, близки к идеальным: в статическом режиме они практически не потребляют электрическую энергию, имеют очень большое входное и малое выходное сопротивления, высокую помехозащищенность, большую нагрузочную способность, довольно высокое быстродействие,

хорошую температурную стабильность. Выходной сигнал Uвых1

практически равен напряжению питания. Высокая плотность компановки обеспечивает преимущественное использование КМОП ЛЭ в больших интегральных схемах. Устойчивая работа КМОПструктур в широком диапазоне питающих напряжений (от 3 до 15 В) позволяет использовать разные источники питания, а также

71

сопрягать ЛЭ по входам и выходам с микросхемами ТТЛ и операционными усилителями.

Недостаток серийных КМОП-устройств по сравнению с ТТЛ – несколько меньшее быстродействие ( FP 3 5 МГц).

Характеристики и параметры логических элементов

При разработке цифровых устройств необходимо знать основные статические и динамические параметры используемых логических интегральных микросхем (ИМС): выходные напряжения «0» и

«1» Uвых0 и Uвых1 , входные токи Iвх0 и Iвх1 , пороговое напряжение Vпор , число входов (коэффициент объединения по входу Kоб ),

нагрузочную способность n (коэффициент разветвления по выходу Kраз ), помехоустойчивость Uпом , задержку распространения сиг-

1,0 |

0,1 |

tз.ср |

tз0,1 t1,0з |

|

|

нала при включении tз |

и выключении tз |

|

, |

||

2 |

|||||

|

|

|

|

потребляемую мощность Pпот и некоторые другие. Параметры ис-

следуемых в работе ИМС приведены в табл. 4.2. Эти параметры позволяют определить особенности каждой серии и дают общую ориентацию при выборе элементной базы на этапе разработки.

Большинство параметров ЛЭ определяется с помощью статических и переходных характеристик, которые ниже приведены для ТТЛ инвертора (серия К155), как наиболее часто используемого ЛЭ.

Схема измерения входного тока Iвх при соответствующем входном напряжении показана на рис. 4.2, а. На основе данных, полученных при измерениях для разных входных напряжений, строится входная характеристика Iвх f (Uвх ) логического элемента, изо-

браженная на рис. 4.2, б. Она позволяет определить входные токи Iвх0 и Iвх1 при соответствующих входных напряжениях.

Аналогично определяются выходные характеристики

U0 |

f (I |

вых |

) |

и U1 |

f (I ) (рис. 4.3). |

вых |

|

|

вых |

вых |

Входные и выходные характеристики позволяют правильно использовать ЛЭ в устройствах, особенно при одновременном ис-

72

пользовании элементов различных серий и типов (например, ТТЛ и КМОП). Определив входные и выходные токи в состояниях U 0 и

U1, можно рассчитать допустимую нагрузочную способность используемых микросхем. Она определяется как максимальное количество входов других элементов n, которое можно подключить к выходу данного элемента при сохранении уровней выходного напряжения в пределах допустимого для состояний «0» и «1».

Рис. 4.2. Схема измерения входного тока (а), входная характеристика ЛЭ ТТЛ (б)

а) |

б) |

Рис. 4.3. Выходные характеристики ЛЭ ТТЛ |

|

Передаточная характеристика Uвых |

f (Uвх) (рис. 4.4) позво- |

ляет определить целый ряд параметров: Uвых1 , Uвых0 , Uпом, Uпом,

Vпор .

73

Переходная характеристика Uвых f (Uвх) (рис. 4.5), снимае-

мая экспериментально с помощью двухканального осциллографа, используется для определения быстродействия ЛЭ. Время задержки измеряется относительно уровня порогового напряжения.

Рис. 4.4. Передаточная |

Рис. 4.5. Переходная характеристика |

характеристика ЛЭ ТТЛ |

ЛЭ |

Остальные параметры ЛЭ определяются расcчетно или экспериментально различными способами.

Применение ЛЭ

В цифровых устройствах логические элементы используются для реализации сложных логических функций. Кроме того, ЛЭ используются для конструирования импульсных и линейных устройств.

Импульсные устройства выполняются на ЛЭ в том случае, когда необходимо получить высокое быстродействие. В данной работе изучается мультивибратор, выполненный на трех ЛЭ ТТЛ типа

(рис. 4.6).

74

Рис. 4.6. Мультивибратор на ЛЭ

В данном устройстве первый элемент за счет отрицательной обратной связи (R1) работает в линейном режиме. Колебания возникают и поддерживаются за счет положительной обратной связи (С1). Частоту выходных импульсов (при R1 = 390 Ом) можно определить по приближенной формуле:

1000

Fг C1 ,

где С1 – емкость конденсатора, нФ; Fг – частота, кГц.

Триггеры

Помимо логических элементов, реализующих основные логические функции, большое значение в качестве базовых элементов цифровой техники имеют триггеры – элементы, имеющие два устойчивых состояния и предназначенные, главным образом, для хранения одного бита информации. По способу записи информации триггеры подразделяют на асинхронные и синхронные. Запись информации в асинхронные триггеры осуществляется непосредственно при поступлении информационных сигналов на его входы, тогда как в синхронных изменение состояния происходит только в момент действия синхронизирующих импульсов.

По функциональному признаку триггеры подразделяют на RS-, D-, Т-, DV-, JK-триггеры. В зависимости от комбинации сигналов

на входе, на выходе триггера возможны пять состояний: 0, 1, Qn ,

Qn , Х, причем Qn означает, что на выходе триггер не меняет сво-

его состояния, Qn – изменяет на противоположное, Х – состояние на выходе не определено.

75

Простейший асинхронный триггер RS-типа получается при охвате двух элементов типа И-НЕ или ИЛИ-НЕ положительными обратными связями (рис. 4.7).

Рис. 4.7. Асинхронный RS-триггер: а – на элементах И-НЕ; б – на элементах ИЛИ-НЕ

На рис. 4.8 представлена схема синхронного RS-триггера и его обозначение.

Запись информации в триггер такого типа происходит при наличии разрешающего сигнала («1») на входе С. Сигналы на выходе определяются таблицей истинности (табл. 4.3).

Недостатком RS-триггера является неопределенное состояние на выходе при подаче на оба входа сигналов «1», что затрудняет его использование в цифровых устройствах.

Рис. 4.8. Синхронный RS-триггер (а) и его обозначение (б)

|

|

Таблица 4.3 |

|

|

|

S |

R |

Qn 1 |

0 |

0 |

Qn |

1 |

0 |

1 |

|

|

|

0 |

1 |

0 |

1 |

1 |

Х |

|

|

|

76

D-триггер, или триггер задержки ( -задержка) при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D. Таким образом выходной сигнал Q изменяется не сразу после изменения входного сигнала D, а только с приходом синхронизирующего импульса, т.е. с задержкой на один период импульсов.

Обозначение синхронного D-триггера (триг- гера-защелка) представлено на рис. 4.9.

Т-триггер, или счетный триггер (рис. 4.11, б), изменяет состояние выхода на противоположное по переднему или заднему фронту синхронизирующего импульса, поступающего на вход С.

Наиболее широко в цифровой технике ис-

пользуются JK-триггеры, особенностью которых является универсальность. На рис.4.10 показано обозначение и таблица истинности JK-триггера.

Рис. 4.10. JK-триггер (а) и его таблица истинности (б)

Как видно из таблицы истинности JK-триггер имеет два информационных входа. Однако в отличие от RS-триггера, в нем разрешена подача на вход J K 1. При этом на выходах триггера состояние меняется на противоположное. Универсальность JK- триггеров определяется тем, что они могут при соответствующем включении выполнять функции триггеров других типов. На рис. 4.11 показано использование JK-триггера в качестве D – (см. рис. 4.11, а) и Т – (см. рис. 4.11, б) триггеров.

Рис. 4.11. Некоторые включения на основе JK-триггера: а – D- триггер; б – Т – триггер

77

Триггеры в цифровых устройствах используются и как самостоятельные изделия, и как компоненты более сложных интегральных микросхем последовательностного типа (регистры, счетчики, оперативные запоминающие устройства).

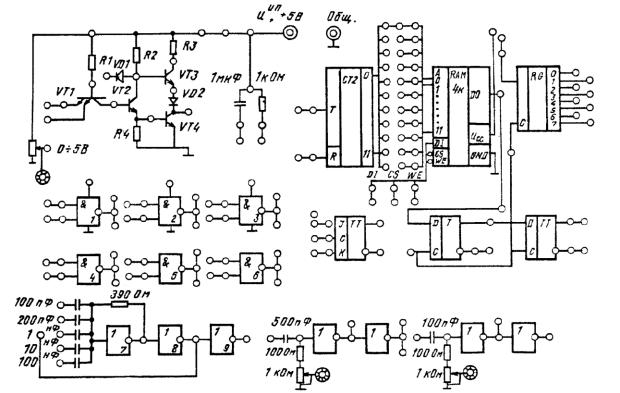

ОПИСАНИЕ ЛАБОРАТОРНОГО МАКЕТА

Лицевая панель макета для изучения ЛЭ и некоторых устройств на их основе представлена на рис. 4.12. Питание макета осуществляется от внешнего источника напряжением 5,0 В. Необходимые для исследования регулируемые формирователи напряжения встроены в макет. Там же расположен мультивибратор, предназначенный для определения динамических параметров ЛЭ. Кроме

U ип 5 В никакие сигналы на макет не подаются.

Правая часть макета в лабораторной работе не используется.

ПОДГОТОВКА К РАБОТЕ

1.Изучить по описанию и рекомендуемой литературе принцип работы и основные параметры ЛЭ. Ответить на контрольные вопросы.

2.Рассчитать потенциальную карту элемента ТТЛ, представленного на макета, т.е. напряжения в точках, отмеченных кружочками,

(см. |

рис. 4.12) |

для |

двух |

вариантов U |

вх |

: |

X |

1 |

X |

2 |

U1 |

и |

||||

|

|

|

|

|

|

|

|

|

|

|

|

вх |

|

|||

X |

X |

2 |

U 0 |

(U |

бэ |

и U |

д |

открытых транзистора и диода считать |

||||||||

1 |

|

вх |

|

|

|

|

|

|

|

|

|

|

|

|||

равными 0,7 В).

3.Для указанных на макете параметров элементов рассчитать частоты выходных импульсов мультивибратора.

4.Предложить схему на логических элементах И-НЕ, выполняющую логическую функцию ИЛИ.

5.Определить нагрузочную способность элемента 564 серии, управляющего элементами серии 555.

78

79

Рис. 4.12. Лицевая панель макета

РАБОЧЕЕ ЗАДАНИЕ

1.Снять потенциальную карту элемента ТТЛ, представленного на макете для состояний «0» и «1» на выходе. Сравнить с расчетом.

2.Снять передаточные характеристики элементов 1, 2, 3 (см. рис.4.12) серий К155, К555, 564 соответственно. Объяснить особенности.

3.Определить максимальную нагрузочную способность элемента серий 564, управляющего элементами серии 555.

4.На элементах 7, 8, 9 (см. рис.4.12) собрать мультивибратор. Определить параметры выходного сигнала для различных С. Сравнить с расчетом.

5.На элементах 1, 4 или 2, 5, или 3, 6 (см. рис.4.12) собрать асинхронный RS-триггер, представленный на рис.4.7, а. Проверить таблицу истинности.

6.Используя мультивибратор в качестве входного генератора определить:

временные параметры элементов 1, 2, 3; используя двухканальный осциллограф для снятия переходной характеристики,

зависимость потребляемой элементом мощности от частоты переключения (элемент 2). Для расчета потребляемой мощности необходимо измерить значения напряжения питания и потребляемого тока при различных частотах переключения. В этом случае напряжение питания подается на микросхему через резистор величиной 1 кОм, встроенный в макет, и ток потребления определяется по падению напряжения на резисторе.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1.Приведите таблицы истинности всех логических операций, приведенных в описании.

2.Нарисуйте схему элемента ТТЛ.

3.Укажите основные параметры логических элементов.

4.Нарисуйте переходную характеристику ЛЭ И-НЕ.

5.Нарисуйте передаточную характеристику ЛЭ ТТЛ.

6.Как зависит Uвых от количества нагрузок?

7.Как зависит Uвых0 от количества нагрузок?

80