- •Предисловие

- •Глава 1. Общие сведения о микропроцессорах

- •1.1 Классификация микропроцессоров

- •1.2 Характеристики микропроцессоров

- •1.2.1 Тактовая частота

- •1.2.2 Архитектура процессора

- •1.2.3 Технологический процесс производства

- •1.2.4 Частота системной шины

- •1.2.5 Размер кэша

- •1.3 Типы архитектур микропроцессоров

- •1.4 Структурная схема микропроцессоров

- •1.4.1 Микропроцессор Фон-Неймана

- •1.4.2 Конвейер

- •1.4.3 Зависимость между частотой и количеством ступеней конвейера

- •1.5 Представление информации в эвм

- •1.5.1 Двоичное представление целых чисел

- •1.5.2 Представление символьной информации

- •Глава 2. Архитектура микропроцессоров ia-32

- •2.1 Состав и функции регистров

- •2.1.1 Основные регистры

- •2.1.2 Регистры дополнительных функциональных модулей

- •2.2 Типы адресации

- •2.3 Система команд

- •2.3.1 Классификация команд

- •2.3.2 Формат команды

- •2.3.3 Однобайтовые команды

- •2.3.4 Непосредственно заданные операнды

- •2.3.5 Команды с регистровыми операндами

- •2.3.7 Команды с операндами, расположенными в памяти

- •Глава 3. Организация многоуровневой памяти

- •3.1 Принцип построения многоуровневой памяти

- •3.2 Организация кэш-памяти

- •3.3 Протоколы когерентности памяти микропроцессоров

- •3.4 Страничная организация памяти

- •Глава 4. Режимы работы процессоров ia-32

- •4.1 Обзор режимов работы

- •4.2 Реальный режим адресации

- •4.3 Защищённый режим

- •4.3.1 Дескрипторные таблицы

- •4.3.2 Дескрипторные регистры

- •4.3.3 Дескриптор

- •4.3.4 Односегментная модель памяти

- •4.3.5 Многосегментная модель памяти

- •Глава 5. Страничная организация памяти в процессорах ia‑32

- •5.1 Каталог страниц

- •5.2 Таблица страниц

- •5.3 Страничная переадресация

- •5.4 Диспетчер виртуальных машин системы Microsoft Windows

- •Глава 6. Архитектура процессоров с параллелизмом уровня команд

- •6.1 Подходы к использованию ресурса транзисторов в микропроцессорах

- •6.2 Суперскалярные процессоры и процессоры с длинным командным словом

- •6.3 Зависимости между командами, препятствующие их параллельному исполнению

- •6.4 Предварительная выборка команд и предсказание переходов

- •6.5 Условное выполнение команд в vliw-процессорах

- •6.6 Декодирование команд, переименование ресурсов и диспетчеризация

- •6.7 Исполнение команд

- •6.8 Завершение выполнения команды

- •6.9 Направления развития архитектуры процессоров с параллелизмом уровня команд

- •Глава 7. Мультитредовые микропроцессоры

- •7.1 Основы мультитредовой архитектуры

- •7.2 Выявление тредов

- •7.3 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков управления программы

- •7.3.1 Мультитредовая модель выполнения программы

- •7.3.2 Мультитредовые программы

- •7.3.3 Аппаратные средства мультитредовой архитектуры

- •7.3.4 Преимущества мультитредовой архитектуры

- •7.4 Мультитредовые процессоры с тредами, выявляемыми путем анализа потоков данных программы

- •7.5 Специфика мультитредовых моделей распараллеливания

- •Глава 8. Модуль обработки вещественных чисел

- •8.1 Представление чисел с плавающей запятой

- •8.2 Состав модуля fpu

- •Глава 9. Основы 64-разрядной архитектуры

- •9.1 Состав и назначение регистров микропроцессора ia-64

- •9.2 Особенности архитектуры epic

- •9.3 Архитектура x86-64

- •9.4 Структура одноядерного процессора

- •9.5 Многоядерные процессоры

- •9.6 Зачем нужны “лишние” разряды?

- •Глава 10. Современные 64-разрядные микропроцессоры корпораций Intel и amd

- •10.1 Архитектура Intel Core 2

- •10.1.1 Intel Wide Dynamic Execution

- •10.1.2 Intel Intelligent Power Capability

- •10.1.3 Intel Advanced Smart Cache

- •10.1.4 Intel Smart Memory Access

- •10.1.5 Intel Advanced Digital Media Boost

- •10.1.6 Логическая схема процессора

- •10.2 Архитектура Intel Core i7

- •10.2.1 Технология Hyper-Threading в архитектуре Nehalem

- •10.2.2 Иерархия кэш-памяти в архитектуре Nehalem

- •10.3 Хронология развития семейств микропроцессоров с архитектурой Nehalem

- •10.4 Архитектура amd Athlon 64

- •10.4.1 Ядро процессора

- •10.4.3 Контроллер памяти

- •10.4.4 Контроллер HyperTransport

- •10.5 Архитектура amd k10

- •10.4.1 Технология amd Memory Optimizer Technology

- •10.5.2 Ядро процессора

- •10.5.3 Предвыборка данных и инструкций

- •10.5.4 Выборка из кэша

- •10.5.5 Предсказание переходов и ветвлений

- •10.5.6 Процесс декодирования

- •10.5.7 Диспетчеризация и переупорядочение микроопераций

- •10.5.8 Выполнение микроопераций

- •10.5.9 Технологии энергосбережения

- •10.5.10 Шина HyperTransport 3.0

- •10.5.11 Семейство процессоров Barcelona

- •10.5.12 Семейство процессоров Phenom

- •Глава 11. Технологии, поддерживаемые современными микропроцессорами

- •11.1 Технологии тепловой защиты

- •11.1.1 Технология Thermal Monitor

- •11.1.2 Технология Thermal Monitor 2

- •11.1.3 Режим аварийного отключения

- •11.2 Технологии энергосбережения

- •11.2.1 Технология Enhanced Intel SpeedStep

- •11.2.2 Технология Cool'n'Quiet

- •11.3 Технология расширенной памяти

- •11.4 Технология антивирусной защиты

- •11.5 Технология виртуализации

- •11.6 Реализация технологий в современных микроархитектурах

- •11.6.2 Em64t – NetBurst

- •11.6.3 Intel Core

- •11.6.4 Intel Atom

- •11.6.5 Nehalem

- •11.6.6 Xeon

- •Глава 12. Графические микропроцессоры

- •12.1 Основные термины и определения

- •12.2 Технологии построения трёхмерного изображения

- •12.2.1 Технологии повышения реалистичности трехмерного изображения

- •12.3 Шейдерный процессор

- •12.4 Особенности современных графических процессоров

- •Глава 13. Однокристальные микроконтроллеры

- •13.1 Общая характеристика микроконтроллеров

- •13.2 Микроконтроллеры семейства avr

- •Почему именно avr?

- •13.3 Общие сведения об омк avr

- •13.4 Характеристики avr-микроконтроллеров

- •Глава 14. Технология производства микропроцессоров

- •14.1 Особенности производства процессоров

- •14.2 Новые технологические решения

- •14.3 Технология производства сверхбольших интегральных схем

- •I. Выращивание кристалла кремния

- •II. Создание проводящих областей

- •III. Тестирование

- •IV. Изготовление корпуса

- •V. Доставка

- •14.4 Перспективы производства сбис

- •Англо-русский словарь терминов и аббревиатур

- •Библиографический список

- •Интернет-ссылки

- •350072. Краснодар, ул. Московская, 2, кор. А.

9.3 Архитектура x86-64

Архитектура x86-64 с одной стороны совместима с 32-разрядной архитектурой x86, с другой стороны – является 64-разрядной. Согласно кросслицензионному соглашению архитектуру x86-64 развивают и поддерживают корпорации AMD (технология AMD-64) и Intel (технология EM64T).

В настоящее время развивается именно эта архитектура, так как она поддерживает совместимость с IA-32 без внутренней трансляции.

Например, 64-разрядные процессоры семейства Hammer, разработанные фирмой AMD, базируются на архитектуре x86-64, которая является расширением IA-32.

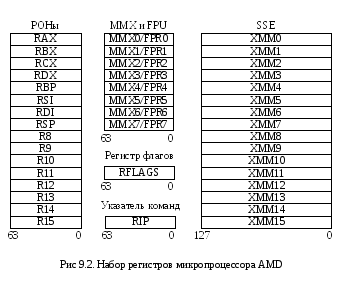

На рисунке 9.2. приведён набор регистров МП AMD. Прежние 32-разрядные регистры, расширенные до 64-бит, получили имена RAX, RBX, RCX, RDX, RBP, RSI, RDI, RSP, RIP и RFLAGS. Новые регистры остались безымянными и просто пронумерованы от R8 до R15. Для обращения к младшим 8-, 16- и 32-битам новых 64-разрядных регистров можно использовать постфиксы b, w и d соответственно (byte, word, dword). Например, R9 – это 64-разряный регистр, R9b – его младший байт (по аналогии с AL), а R9w – младшее слово (то же самое, что AX в EAX). Прямых наследников AH, к сожалению, не наблюдается и для манипуляции со средней частью регистров приходится использовать сдвиги.

В блок SSE в дополнение к восьми 128 разрядным регистрам XMM0-XMM7, введены восемь новых регистров XMM8-XMM15, что обеспечивает поддержку SSE2 путём увеличения количества SIMD команд.

Регистр-указатель команд RIP теперь адресуется точно так же, как и все остальные регистры общего назначения. Однако это не является новинкой. Ещё в PDP-11 (или в её отечественном клоне "Электроника БК" или "УКНЦ") указатель команд был программно доступен.

В таблице 9.2 указаны режимы работы микропроцессоров AMD-64. В режиме совместимости с прежней архитектурой x86 (Legacy Mode) ни 64-битные регистры, ни новые методы адресации недоступны. Однако можно выполнять программы в защищённом, виртуальном и реальном режимах.

Для доступа к 64-битным регистрам и выполнения 64-битных приложений необходимо перевести процессор в "длинный" режим (long mode), который делится на два подрежима: подрежим совместимости с x86 (compatibility mode) и 64-битный подрежим (64-bit mode). Подрежим совместимости предусмотрен только для того, чтобы 64-разрядная операционная система могла выполнять старые 32-битные приложения.

Таблица 9.2. Режимы работы микропроцессоров AMD-64.

|

Режим работы |

Требуемая операционная система |

Требуется перекомпиляция приложений |

Разрядность |

Регистровые расширения |

Используемые разряды РОНов | ||

|

адреса |

данных | ||||||

|

Режим Long |

64-битный подрежим |

64-битная ОС |

Да |

64 |

32 |

Да |

64 |

|

Подрежим совместимости |

Нет |

32 |

Нет |

32 | |||

|

16 |

16 |

16 | |||||

|

Режим Legacy |

Защищённый режим |

32-битная ОС |

Нет |

32 |

32 |

Нет |

32 |

|

16 |

16 | ||||||

|

Виртуальный режим |

16-битная ОС |

16 |

16 |

16 | |||

|

Реальный режим | |||||||