GEK / Перечень вопросов 2014_ВКСС

.pdf

Рис. 28.3. Организация памяти конвейерных ВС.

Примерами систем "память-память" являются Advanced Scientific Computer фирмы

Texas Instruments Inc. и системы Control Data Corporation (Star 100, Cyber 200). Все эти вычислительные системы появились в середине 70-х прошлого века после длительного цикла разработки, но к середине 80-х годов от них отказались. Причиной послужило слишком большое время запуска - порядка 100 циклов процессора. Это означает, что операции с короткими векторами выполняются очень неэффективно, и даже при длине векторов в 100 элементов процессор достигал только половины потенциальной производительности.

В вычислительных системах типа «регистр-регистр» векторы имеют сравнительно небольшую длину (в ВС семейства Cray - 64), но время запуска значительно меньше чем в случае «память-память». Преимущество ВС с режимом «регистррегистр» - эффективная обработка коротких векторов Недостаток: обработка длинных векторов (векторные регистры должны загружаться сегментами несколько раз). В настоящее время ВП типа «регистр-регистр» доминируют на компьютерном рынке.

Конвейерные процессоры.

Обобщенная структура векторного процессора приведена на рис.28.4. На схеме показаны основные узлы процессора, без детализации некоторых связей между ними.

Рис. 28.4. Структура векторного процессора.

Особенности векторного процессора.

Обработка всех n компонентов векторов-операндов задается одной векторной командой.

Элементы векторов представляются числами в форме с плавающей запятой

(ПЗ).

АЛУ векторного процессора может быть реализовано в виде:

oединого конвейерного устройства, способного выполнять все предусмотренные операции над числами с ПЗ

oАЛУ состоит из отдельных блоков сложения и умножения, а иногда и блока для вычисления обратной величины, когда операция

деления x/y реализуется в виде x(1/y). Каждый из таких блоков также конвейеризирован.

Состав векторной системы:

Cкалярный процессор, что позволяет параллельно выполнять векторные и скалярные команды.

Векторные регистры для хранения векторов-операндов, которые представляют собой совокупность скалярных регистров, объединенных в очередь типа FIFO, способную хранить 50-100 чисел с плавающей запятой.

Набор векторных регистров (Va, Vb, Vc,...) имеется в любом векторным процессоре. Система команд векторного процессора поддерживает работу с векторными регистрами и обязательно включает в себя команды:

загрузки векторного регистра содержимым последовательных ячеек памяти, указанных адресом первой ячейки этой последовательности;

выполнения операций над всеми элементами векторов, находящихся в векторных регистрах;

сохранения содержимого векторного регистра в последовательности ячеек памяти, указанных адресом первой ячейки этой последовательности.

Регистр длины вектора. Этот регистр определяет, сколько элементов фактически содержит обрабатываемый в данный момент вектор, то есть сколько индивидуальных операций с элементами нужно сделать.

Регистр максимальной длины вектора, определяющий максимальное число элементов вектора, которое может быть одновременно обработано аппаратурой процессора. Этот регистр используется при разделении очень длинных векторов на сегменты, длина которых соответствует максимальному числу элементов, обрабатываемых аппаратурой за один прием.

Регистр маски вектора служит для выполнения таких операций, в которых должны участвовать не все элементы векторов. В этом регистре каждому элементу вектора соответствует один бит. Установка бита в единицу разрешает запись соответствующего элемента вектора результата в выходной векторный регистр, а сброс в ноль — запрещает.

Регистр вектора индексов по структуре аналогичен регистру маски. Служит для выполнения операций упаковки/распаковки для получения вектора, содержащего ненулевые элементы и для обратной операции соответственно. В векторе индексов каждому элементу исходного вектора соответствует один бит. Нулевое значение бита свидетельствует, что соответствующий элемент исходного вектора равен нулю.

22. Вычислительные системы с систолической структурой.

Систолическая архитектура вычислительного устройства является решением, агрессивно эксплуатирующим параллелизм "конвейерного" типа. Несмотря на принципиальную дороговизну решения (применение специализированных аппаратных решений), систолы являются одним из самых эффективных методов решения специализированных задач, так как часто обеспечивают на конкретной задаче быстродействие, недостижимое для большинства микропроцессорных архитектур. Значительное удешевление программируемых логических матриц сводит на нет экономическую составляющую вопроса применения и пробуждает интерес исследователей к применению систол в сложных вычислительных задачах.

Систолические системы являются очень специализированными вычислителями и производятся в основном под конкретную задачу. Фактически, задача построения систолического вычислителя сводится к постороению аппаратного конвейера, имеющего достаточно большое время получения результата (т.е. большое количество ступеней) но при этом сравнительно маленькое время между последовательной выдачей результатов, так как значительное количество промежуточных значений обрабатывается на разных ступенях конвейера.

Если провести параллель в физиологии, то систолы больше всего напоминают систему сосудов и сердце, которое постоянно посылает кровь во все артерии, сосуды и капилляры тела.

Зачем использовать систолические структуры?

Систолы отличаются простой и регулярной структурой (по крайней мере описанные в специализированной литературе):

Вычисления в систолах "ритмичны", последовательны, и происходят в своеобразной ячеисто-циклической манере;

экономически выгодно построение в небольших партия;

с технической точки зрения эксплуатировать можно практически все доступные виды параллелизма;

модульная структура систол позволяет достаточно просто расширять систолы;

вычислительная эффективность систол определяется правильным построением конвейера, чаще всего наиболее эффективны простые структуры;

систолы выгодно используют полосу пропускания каналов доступа к памяти, отличаясь предсказуемым обращением к памяти;

Что скрывается под термином "Систолическая архитектура"?

Общая методология проекции вычислительных алгоритмом на аппаратные архитектуры;

Увеличение быстродействия обработки сигналов и машинной графики: матричных операций, графовых алгоритмов, обработки информации баз данных.

Достаточно дешёвый аппаратный акселератор определённых операций;

Базовые принципы построения систолических архитектур:

oСистола представляет собой сеть связанных вычислительных ячеек, обычно простых;

oКаждая ячейка содержит в себе буферный входной регистр, защёлкивающий данные и вычислитель, оперирующий с содержимым

этого регистра. Выход вычислителя может подаваться на входы других ячеек;

o Операции в систоле производятся по типу конвейерной обработки;

oВычисления в систоле регулируются с помощью общего тактового сигнала;

oРезультатом правильного построения систолы должна быть простая, регулярная разводка с простой топологией связей;

oСовременные систолические решения основаны на парадигмах ОКМД/МКМД, являются репрограмируемыми и реконфигурируемыми.

Приведём схему типичной систолы:

Рис. 30.2. Систола, дающая на выходе скалярное произведение массивов чисел.

Структура систолы имеет ряд недостатков:

Общая тактовая частота должна быть такой, чтобы за время одного такта успевали полностью отработать все вычислители, на данном рисунке умножитель явно отрабатывает за в несколько раз большее время, чем сумматор. На выходе сумматора изменение суммы из-за очередной поданной пары значений производится через 2 такта. При конвейеризации устройства умножителя, обычно представляя его как сумматоры, длина конвейера удлиняется (до 9-33 тактов), но частота следования тактового сигнала может быть повышена на порядок. Съём результата производится с выходов сумматора, естественно предусматривается

сигнал для его обнуления перед загрузкой очередных массивов данных. Рассмотрим крайне показательный пример систолы: умножение матриц. Для примера рассмотрим умножение матриц 3 на 3:

Рис. 30.4. Умножение матриц 3 на 3.

Обычно сквозная система связей не реализуется, поэтому результаты снимаются с выходов ячеек-умножителей с верхнего левого угла до нижнего правого угла (одновременно получаемые результаты показаны толстыми наклонными линиями, соединяющими ячейки).

Некоторые замечания по разработке систол.

Процесс разработки систолической структуры обычно выглядит так:

Разрабатывается алгоритм;

проектируется архитектура - поиск параллелизма (особенно конвейерного в алгоритме);

производится проекция алгоритмы на цифровые вычислительные схемы.

23.Структура матричной вычислительной системы. Способы построения процессорного поля матрицы.

Наиболее распространенными из систем класса ОКМД (Одиночный поток команд, множественный поток данных) являются матричные системы, которые лучше всего приспособлены для решения задач, характеризующихся параллелизмом независимых объектов или параллелизмом данных. Организация систем этого типа на первый взгляд достаточно проста: общее управляющее устройство, генерирующее поток команд, и большое число устройств, работающих параллельно и обрабатывающих каждое свой поток данных. Таким образом, производительность системы оказывается равной сумме производительности всех обрабатывающих устройств. Однако на практике, чтобы обеспечить достаточную эффективность системы при решении широкого круга задач, необходимо организовать связи между обрабатывающими устройствами (в дальнейшем будем называть их процессорными элементами – ПЭ). Характер

связей может быть различным, так же как и характер взаимодействия ПЭ. Все это и определяет разные свойства систем.

Матричный или векторный процессор (Array Processor) представляет собой "матрицу" связанных идентичных элементарных процессоров, управляемых одним потоком команд. Элементарный процессор (ЭП) включает в себя как арифметикологическое устройство и память, так и локальный коммутатор. Сеть связей между ЭП (точнее, локальными коммутаторами) позволяет осуществлять обмен данными между любыми процессорами. Поток команд поступает на матрицу ЭП от единого устройства управления (SIMD-архитектура, в каноническом виде).

Архитектура матричного процессора была выбрана в начале 60-х годов 20 века, была обоснована существовавшими экономическими ограничениями и необходимостью обеспечения высокой производительности при решении сложных задач. В самом деле, в то время основная доля стоимости ЭВМ приходилась на схемы устройства управления, а не на схемы арифметико-логического устройства или памяти. Поэтому централизация устройства управления и параллелизм устройств обработки и хранения информации обеспечивали компромисс между стоимостью и производительностью ВС. С развитием интегральной технологии для производства электронных схем эти экономические соображения стали несущественными при выборе архитектуры вычислительного средства. Однако в конце 20 столетия при производстве БИС, включающих множества процессоров, матричная архитектура вновь стала технико-экономически привлекательной. Имеется широкий спектр сложных научных, технических и экономических задач, которые эффективно решаются на матричных процессорах. При решении сложных задач фактически один и тот же алгоритм параллельно (одновременно) реализуется над многими частями исходного массива данных. Ясно, что перед решением сложной задачи на матричном процессоре требуется предварительная организация данных в векторы или упорядоченные множества. Следовательно, в каждом ЭП размещаются и обрабатываются свои компоненты векторов или свои локальные массивы данных.

Способы построения процессорного поля матрицы.

Первой матричной системой следует считать систему SOLOMON, упрощенная структура которой представлена на рис. 29.1. Система содержит 1024 ПЭ, соединенных в виде матрицы 32X32. Каждый ПЭ в матрице соединен с четырьмя соседними и включает в себя процессор, обеспечивающий выполнение последовательных поразрядных арифметических и логических операций, а также оперативное ЗУ емкостью 16 Кбит, разбитое на модули по 4 Кбит каждый. Длина слова переменная – от 1 до 128 разрядов. Разрядность слов устанавливается программно. По каналам связи от УУ передаются команды и общие константы. В ПЭ используется так называемая многомодальная логика, которая позволяет каждому ПЭ выполнять (т. е быть активным) или не выполнять (быть пассивным) общую операцию в зависимости от значений обрабатываемых данных.

Рис. 29.1. Система типа ОКМД.

В каждый момент все активные ПЭ выполняют одну и ту же операцию над данными, хранящимися в собственной памяти и имеющими один и тот же адрес. Идея многомодальности заключается в том, что в каждом ПЭ имеется специальный регистр на четыре состояния – регистр моды. Мода (или модальность) заносится в этот регистр от УУ. При выполнении последовательности команд модальность передается в коде операции и сравнивается с содержимым регистра моды. Если есть совпадение, то операция выполняется. В других случаях ПЭ не выполняет операцию, но может в зависимости от кода пересылать свои операнды соседнему ПЭ. Такой механизм позволяет, в частности, выделить строку или столбец ПЭ, что может быть полезным при операциях над матрицами. Взаимодействуют ПЭ с периферийным оборудованием через внешние ПЭ.

Система SOLOMON оказалась нежизнеспособной вследствие громоздкости, недостаточной гибкости и эффективности. Однако идеи, заложенные в ней, получили развитие в системе ILLIAC-IV, разработанной Иллинойсским университетом и изготовленной фирмой «Барроуз».

Рис. 29.2. Система ILLIАС-IV (проект).

По первоначальному проекту система ILLIAC-IV должна была включать в себя 256 ПЭ, разбитых на 4 группы – квадранты, каждый из которых должен управляться специальным процессором (УП). Управление всей системой,

содержащей кроме ПЭ и УП также внешнюю память и оборудование ввода – вывода, предполагалось от центрального управляющего процессора (ЦУП). Однако реализовать этот замысел не удалось из-за возникших технологических трудностей при создании интегральных схем, ОЗУ и удорожания всего проекта почти в два раза. В результате с опозданием на два года (в 1971 г.) система была создана в составе одного квадранта и одного УП и с начала 1974 г. введена в

эксплуатацию. Ранее предполагалось получить на этой системе производительность примерно 1 млрд. операций в секунду, однако реализовано 200 млн. операций в секунду. Тем не менее этого оказалось достаточно, чтобы система в течение ряда лет считалась самой высокопроизводительной в мире.

Рис. 29.3. Квадрант системы ILLIAC-IV.

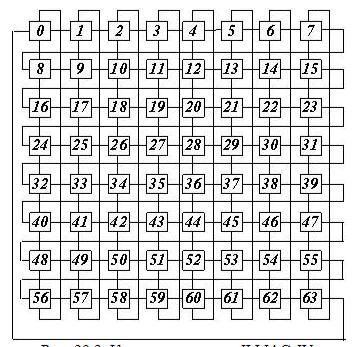

В каждом квадранте 64 ПЭ образуют матрицу размером 8x8. Схема связей между ПЭ (рис. 29.3) похожа на схему системы SOLOMON, но связь с внешней средой имеют все ПЭ без исключения. Реально действующая система ILLIAC-IV состоит, таким образок, из двух частей: центральной с устройством управления и 64 ПЭ, а также подсистемы ввода – вывода, включающей в себя универсальную ЭВМ В- 6700, файловые диски и лазерную архивную память большой емкости. Каждый ПЭ состоит из собственно процессора и ОЗУ. Процессор оперирует с 64-разрядными числами и выполняет универсальный набор операций. Быстродействие процессора достаточно высокое, операция сложения 64-разрядных чисел выполняется за 240 нс, а умножения – за 400 нс. Таким образом, процессор выполняет в среднем 3 млн. операций в секунду, а следовательно производительность системы равна 3X64≈200 млн. операций в секунду.

Емкость ОЗУ каждого ПЭ составляет 2048 64-разрядных слов, длительность цикла обращения к памяти 350 нс. Память выполнена на интегральных схемах. Каждый процессор имеет счетчик адресов и индексный регистр, так что конечный адрес в каждом процессоре может формироваться как сумма трех составляющих: адреса, содержащегося в команде для данного ПЭ, кода, содержащегося в центральном индексном регистре УУ, и кода, содержащегося в собственном индексном регистре. Это существенно повышает гибкость системы по сравнению с системой SOLOMON, где все ПЭ выбирают информацию по одному адресу. Каждый процессор кроме индексного регистра имеет в своем составе пять программно-

адресуемых регистров: накапливающийся сумматор, регистр для операндов, регистр пересылок, используемый при передачах от одного ПЭ к другому, буферный регистр на одно слово и регистр управления состоянием ПЭ (аналогичный регистру моды в системе SOLOMON). Регистр управления имеет 8 разрядов. В зависимости от содержимого этого регистра ПЭ становится активным или пассивным, а также выполняет ряд пересылочных операций. Если вычисления не требуют полной разрядности, то процессор может быть разбит на два 32разрядных подпроцессора или даже восемь 8-разрядных. Это позволяет в случае необходимости обрабатывать векторные операнды из 64, 2X64=128 и 8X64=512 элементов.

Как видно из рис. 2.6, каждый i-й ПЭ связан с четырьмя

другими: и м. При такой связи передача данных между любыми двумя ПЭ осуществляется не более, чем за 7 шагов, а среднее число шагов равно 4.

По шине состояния ПЭ могут передавать сигналы о состоянии в УУ, которое таким образом всегда определяет состояние системы. Оперативное ЗУ каждого процессорного элемента связано со своим процессором, устройством управления центральной частью и подсистемой ввода – вывода.

Подсистема ввода – вывода включает в себя стандартную ЭВМ В-6700 (первоначально В-6500) и два уровня внешней памяти: на магнитных дисках с фиксированными дорожками и лазерную память. Накопители на дисках имеют магнитные головки для каждой дорожки (128 головою на диск), и обмен данными осуществляется по 256-разрядной шине. Емкость каждого диска – около 1 млрд. бит. Для того чтобы согласовать скорость передачи информации с дисков и работу управляющей ЭВМ, в систему включено буферное ОЗУ, состоящее из четырех модулей памяти.

Лазерная память представляет собой одностороннее ЗУ очень большой емкости (1012 бит). Информация записывается на тонкой металлической пленке путем прожигания микроотверстий лазерным лучом. Емкость ЗУ – 1200 млрд. бит. Время доступа к данным от 0,2 до 5 с.

Машина В-6700 выполняет и различные другие функции: транслирует и компонует программы, управляет запросами на ресурсы, производит предварительную обработку информации и т. д.

Следует подчеркнуть, что сверхвысокая производительность системы достигается только на определенных типах задач, таких, например, как операции над матрицами, быстрое преобразование Фурье, линейное программирование обработка сигналов, где как раз имеет место параллелизм данных или параллелизм независимых объектов. Необходимо отметить также и то, что разработка программ для систем ILLIAC-IV, обеспечивающих высокую производительность, является весьма сложным делом. Для упрощения этой работы были разработаны специальные алгоритмические языки.

Система ILLIAC-IV была включена в состав вычислительной сети ARPA. В результате усовершенствования программного обеспечения производительность системы выросла до 300 млн. операций в секунду.

В начале 80-х годов в Советском Союзе в классе систем ОКМД была создана «Параллельная система 2000» (ПС-2000), которая также может быть отнесена к матричным. Эта система ориентирована на решение задач, характеризующихся параллелизмом данных, независимых ветвей и объектов. Разработчики системы считают, в частности, что ПС-2000 найдет особенно широкое и эффективное применение для обработки геофизической информации, получаемой при поиске нефти и газа, решения задач плазменной кинетики, расчетов устойчивости

летательных аппаратов, обработки гидролокационных сигналов и изображений, решения задач в частных производных и др.

Рис. 29.4. Система ПС-2000.

Укрупненная структура системы ПС-2000 изображена на рис. 29.4. Центральная часть системы – мультипроцессор ПС-2000, состоящий из решающего поля и устройства управления мультипроцессором. Решающее поле строится из одного, двух, четырех или восьми устройств обработки (УО), в каждом из которых восемь процессорных элементов. Таким образом, мультипроцессор может содержать 8, 16, 32 или 64 процессорных элемента. Процессорный элемент обрабатывает 24разрядные слова, используемые для представления 12-, 16- и 24разрядных чисел с фиксированной запятой, в которых 20 разрядов определяют мантиссу и 4 разряда

– шестнадцатеричный порядок. Емкость оперативной памяти процессорного элемента – 4096 или 16 384 24-разрядных слова с циклом обращения соответственно 0,64 или 0,94 мкс. Мультипроцессор из 64 процессорных элементов обеспечивает при обработке данных следующую производительность (в

миллионах операций в секунду): |

|

Сложение с фиксированной запятой (регистр–регистр) |

200 |

Сложение с плавающей запятой |

66,4 |

Умножение |

28,5 – 50,0 |

Время выполнения основных операций (в микросекундах): |

|

Транспонирование матрицы 64X64 |

0,45 |

Умножение матриц 64X64: |

|

с фиксированной запятой |

1,0 |

с плавающей запятой |

1,4 |

Быстрое преобразование Фурье на 1024 комплексные точки: |

|

с фиксированной запятой |

1,0 – 2,5 |

с плавающей запятой |

1,4 – 2,8 |

Устройство управления содержит блок микропрограммного управления емкостью 16384 микрокоманды, ОЗУ емкостью 4096 или 16384 24-разрядных слов и АЛУ. В блок микропрограммного управления загружаются микропрограммы обработки данных, ввода – вывода и управления. В комплект программного обеспечения системы входит набор микропрограмм базовой системы операций, ориентированной, на обработку матриц, реализацию быстрого преобразования Фурье и решение задач математической статистики, спектрального анализа,