- •Table of Contents

- •Index

- •Keyword Reference

- •Installation

- •Installation of BASCOM

- •BASCOM IDE

- •Running BASCOM-AVR

- •File New

- •File Close

- •File Save

- •File Save As

- •File Print Preview

- •File Print

- •File Exit

- •View PinOut

- •View PDF viewer

- •View Error Panel

- •Edit Undo

- •Edit Redo

- •Edit Cut

- •Edit Copy

- •Edit Paste

- •Edit Find

- •Edit Find Next

- •Edit Replace

- •Edit Goto

- •Edit Toggle Bookmark

- •Edit Goto Bookmark

- •Edit Indent Block

- •Edit Unindent Block

- •Edit Remark Block

- •Program Compile

- •Program Syntax Check

- •Program Show Result

- •Program Simulate

- •Program Send to Chip

- •Tools Terminal Emulator

- •Tools LCD Designer

- •Tools LIB Manager

- •Tools Graphic Converter

- •Tools Stack Analyzer

- •Tools Plugin Manager

- •Tools Batch Compile

- •Options Compiler

- •Options Compiler Chip

- •Options Compiler Output

- •Options Compiler Communication

- •Options Compiler I2C, SPI, 1WIRE

- •Options Compiler LCD

- •Options Communication

- •Options Environment

- •Options Simulator

- •Options Programmer

- •Supported Programmers

- •ISP programmer

- •PG302 programmer

- •Sample Electronics cable programmer

- •KITSRUS Programmer

- •MCS Universal Interface Programmer

- •STK500 Programmer

- •Lawicel BootLoader

- •AVR ISP Programmer

- •USB-ISP Programmer

- •MCS Bootloader

- •Options Monitor

- •Options Printer

- •Window Cascade

- •Window Tile

- •Window Arrange Icons

- •Window Minimize All

- •Help About

- •Help Index

- •Help MCS Forum

- •Help MCS Shop

- •Help Support

- •Help Knowledge Base

- •Help Credits

- •BASCOM Editor Keys

- •Program Development Order

- •PlugIns

- •Font Editor

- •PinOut

- •BASCOM HARDWARE

- •Additional Hardware

- •AVR Internal Hardware

- •AVR Internal Registers

- •AVR Internal Hardware TIMER0

- •AVR Internal Hardware TIMER1

- •AVR Internal Hardware Watchdog timer

- •AVR Internal Hardware Port B

- •AVR Internal Hardware Port D

- •Adding XRAM

- •Attaching an LCD Display

- •Memory usage

- •Using the 1 WIRE protocol

- •Using the SPI protocol

- •Power Up

- •Chips

- •ATtiny22

- •ATtiny13

- •ATtiny15

- •ATtiny25

- •ATtiny45

- •ATtiny85

- •ATtiny26

- •ATtiny2313

- •ATMEGA8

- •ATMEGA16

- •ATMEGA32

- •ATMEGA48

- •ATMEGA88

- •ATMEGA168

- •ATMEGA64

- •ATMEGA103

- •ATMEGA128

- •ATMEGA161

- •ATMEGA162

- •ATMEGA163

- •ATMEGA165

- •ATMEGA169

- •ATMEGA323

- •ATMEGA603

- •ATMEGA8515

- •ATMEGA8535

- •BASCOM Language Fundamentals

- •Changes compared to BASCOM-8051

- •Language Fundamentals

- •Mixing ASM and BASIC

- •Assembler mnemonics

- •Reserved Words

- •Error Codes

- •Newbie problems

- •Tips and tricks

- •ASCII chart

- •BASCOM Language Reference

- •$BAUD

- •$BAUD1

- •$BOOT

- •$CRYSTAL

- •$DATA

- •$DEFAULT

- •$EEPLEAVE

- •$EEPROM

- •$EEPROMHEX

- •$EXTERNAL

- •$FRAMESIZE

- •$HWSTACK

- •$INCLUDE

- •$INITMICRO

- •$LCDPUTCTRL

- •$LCDPUTDATA

- •$LCDRS

- •$LCDVFO

- •$LOADER

- •$LOADERSIZE

- •$NOCOMP

- •$NOINIT

- •$NORAMCLEAR

- •$PROG

- •$PROGRAMMER

- •$REGFILE

- •$ROMSTART

- •$SERIALINPUT

- •$SERIALINPUT1

- •$SERIALINPUT2LCD

- •$SERIALOUTPUT

- •$SERIALOUTPUT1

- •$SWSTACK

- •$TIMEOUT

- •$TINY

- •$WAITSTATE

- •$XRAMSIZE

- •$XRAMSTART

- •1WIRECOUNT

- •1WRESET

- •1WREAD

- •1WSEARCHFIRST

- •1WSEARCHNEXT

- •1WVERIFY

- •1WWRITE

- •ACOS

- •ALIAS

- •ASIN

- •BASE64DEC

- •BASE64ENC

- •BAUD

- •BAUD1

- •BINVAL

- •BIN2GRAY

- •BITWAIT

- •BITS

- •BLOAD

- •BSAVE

- •BUFSPACE

- •BYVAL

- •CALL

- •CHECKSUM

- •CIRCLE

- •CLEAR

- •CLOCKDIVISION

- •CLOSE

- •CLOSESOCKET

- •CONFIG

- •CONFIG 1WIRE

- •CONFIG ACI

- •CONFIG ADC

- •CONFIG ATEMU

- •CONFIG BCCARD

- •CONFIG CLOCK

- •CONFIG CLOCKDIV

- •CONFIG COM1

- •CONFIG COM2

- •CONFIG COMx

- •CONFIG DATE

- •CONFIG DCF77

- •CONFIG DEBOUNCE

- •CONFIG I2CDELAY

- •CONFIG I2CSLAVE

- •CONFIG INPUT

- •CONFIG INTx

- •CONFIG GRAPHLCD

- •CONFIG KBD

- •CONFIG KEYBOARD

- •CONFIG LCD

- •CONFIG LCDBUS

- •CONFIG LCDMODE

- •CONFIG LCDPIN

- •CONFIG PORT

- •CONFIG PRINT

- •CONFIG PRINTBIN

- •CONFIG PS2EMU

- •CONFIG RC5

- •CONFIG SDA

- •CONFIG SCL

- •CONFIG SERIALIN

- •CONFIG SERIALIN1

- •CONFIG SERIALOUT

- •CONFIG SERIALOUT1

- •CONFIG SINGLE

- •CONFIG SPI

- •CONFIG SERVOS

- •CONFIG TCPIP

- •CONFIG TIMER0

- •CONFIG TIMER1

- •CONFIG TIMER2

- •CONFIG TWI

- •CONFIG TWISLAVE

- •CONFIG WAITSUART

- •CONFIG WATCHDOG

- •CONFIG X10

- •CONFIG XRAM

- •CONST

- •COSH

- •COUNTER0 and COUNTER1

- •CPEEK

- •CPEEKH

- •CRYSTAL

- •CURSOR

- •DATA

- •DAYOFWEEK

- •DAYOFYEAR

- •DATE$

- •DATE

- •DEBUG

- •DEBOUNCE

- •DECR

- •DECLARE FUNCTION

- •DECLARE SUB

- •DEFxxx

- •DEFLCDCHAR

- •DELAY

- •DISABLE

- •DISKFREE

- •DISKSIZE

- •DISPLAY

- •DO-LOOP

- •DriveCheck

- •DriveGetIdentity

- •DriveInit

- •DriveReset

- •DriveReadSector

- •DriveWriteSector

- •DTMFOUT

- •ECHO

- •ELSE

- •ENABLE

- •ENCODER

- •EXIT

- •FILEATTR

- •FILEDATE

- •FILEDATETIME

- •FILELEN

- •FILETIME

- •FLUSH

- •FORMAT

- •FOR-NEXT

- •FOURTHLINE

- •FRAC

- •FREEFILE

- •FUSING

- •GETADC

- •GETATKBD

- •GETATKBDRAW

- •GETDSTIP

- •GETDSTPORT

- •GETKBD

- •GETRC

- •GETRC5

- •GETTCPREGS

- •GETSOCKET

- •GLCDCMD

- •GLCDDATA

- •GOSUB

- •GOTO

- •GRAY2BIN

- •HEXVAL

- •HIGH

- •HIGHW

- •HOME

- •I2CINIT

- •I2CRECEIVE

- •I2CSEND

- •I2START,I2CSTOP, I2CRBYTE, I2CWBYTE

- •IDLE

- •IF-THEN-ELSE-END IF

- •INCR

- •INITFILESYSTEM

- •INITLCD

- •INKEY

- •INPUTBIN

- •INPUTHEX

- •INPUT

- •INSTR

- •ISCHARWAITING

- •KILL

- •LCASE

- •LCDAT

- •LCDCONTRAST

- •LEFT

- •LINE

- •LINE INPUT

- •LTRIM

- •LOAD

- •LOADADR

- •LOADLABEL

- •LOADWORDADR

- •LOCAL

- •LOCATE

- •LOOKDOWN

- •LOOKUP

- •LOOKUPSTR

- •LOWERLINE

- •MAKEBCD

- •MAKEINT

- •MAKEDEC

- •MAKETCP

- •MEMCOPY

- •NBITS

- •ON INTERRUPT

- •ON VALUE

- •OPEN

- •PEEK

- •POKE

- •POPALL

- •POWER

- •POWERDOWN

- •POWERSAVE

- •PRINTBIN

- •PSET

- •PS2MOUSEXY

- •PULSEIN

- •PULSEOUT

- •PUSHALL

- •RC5SEND

- •RC5SENDEXT

- •RC6SEND

- •READ

- •READEEPROM

- •READMAGCARD

- •RESET

- •RESTORE

- •RETURN

- •RIGHT

- •ROTATE

- •ROUND

- •RTRIM

- •SECELAPSED

- •SECOFDAY

- •SEEK

- •SELECT-CASE-END SELECT

- •SETFONT

- •SETTCP

- •SETTCPREGS

- •SENDSCAN

- •SENDSCANKBD

- •SERIN

- •SEROUT

- •SETIPPROTOCOL

- •SHIFT

- •SHIFTCURSOR

- •SHIFTIN

- •SHIFTOUT

- •SHIFTLCD

- •SHOWPIC

- •SHOWPICE

- •SINH

- •SOCKETCONNECT

- •SOCKETLISTEN

- •SOCKETSTAT

- •SONYSEND

- •SOUND

- •SPACE

- •SPIIN

- •SPIINIT

- •SPIMOVE

- •SPIOUT

- •SPLIT

- •START

- •STCHECK

- •STOP

- •STRING

- •SYSSEC

- •SYSSECELAPSED

- •SYSDAY

- •SWAP

- •TCPCHECKSUM

- •TCPREAD

- •TCPWRITE

- •TCPWRITESTR

- •TANH

- •THIRDLINE

- •TIME$

- •TIME

- •TOGGLE

- •TRIM

- •UCASE

- •UDPREAD

- •UDPWRITE

- •UDPWRITESTR

- •UPPERLINE

- •VARPTR

- •VERSION

- •WAIT

- •WAITKEY

- •WAITMS

- •WAITUS

- •WHILE-WEND

- •WRITE

- •WRITEEEPROM

- •X10DETECT

- •X10SEND

- •#IF ELSE ENDIF

- •International Resellers

- •International Resellers

- •ASM Libraries

- •EXTENDED I2C

- •MCSBYTE

- •MCSBYTEINT

- •TCPIP

- •LCD4BUSY

- •GLCD

- •GLCDSED

- •LCD-EPSON

- •AVR-DOS File System

- •CF Card

- •Compact FlashCard Driver

- •Elektor CF-Interface

- •XRAM CF-Interface for simulation

- •New CF-Card Drivers

- •Floating Point

- •FP_TRIG

- •DOUBLE

- •I2C SLAVE

- •I2CSLAVE

- •I2C TWI Slave

- •SPISLAVE

- •DATE TIME

- •EUROTIMEDATE

- •DATETIME

- •PS2-AT Mouse and Keyboard Emulation

- •AT_EMULATOR

- •PS2MOUSE_EMULATOR

- •BCCARD

- •BCCARD

- •BCDEF

- •BCCALL

- •BCRESET

- •Tools

- •LCD RGB-8 Converter

© MCS Electronics, 1995-2007

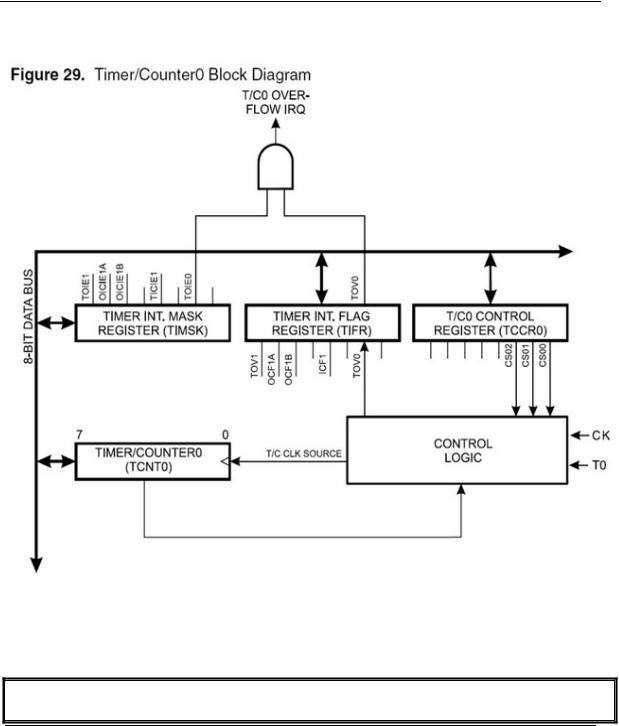

The 8-bit Timer/Counter0 features both a high resolution and a high accuracy mode with lower pre-scaling values. Similarly, high pre-scaling values make the Timer/Counter0 useful for lower speed functions or exact timing functions with infrequent actions.

AVR Internal Hardware TIMER1

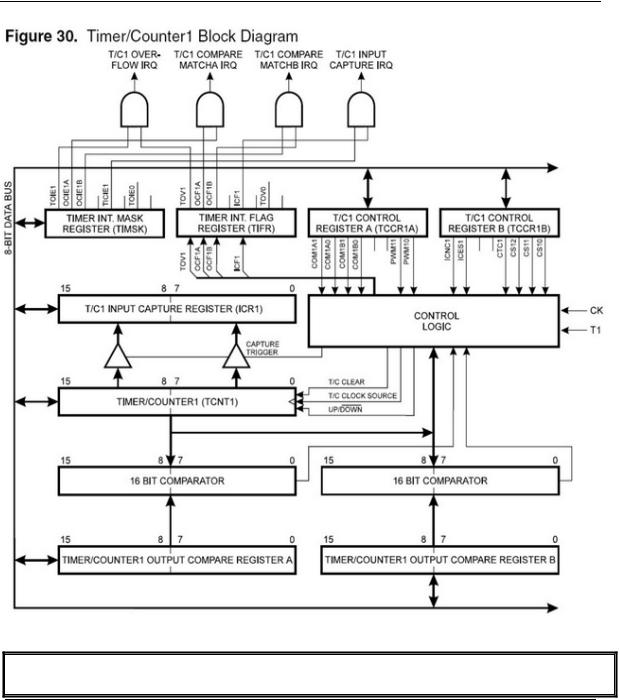

The 16-Bit Timer/Counter1

The 90S8515 was used for the documentation. Other chips might have a somewhat different timer.

The 90S8515 was used for the documentation. Other chips might have a somewhat different timer.

The 16-bit Timer/Counter1 can select its clock source from CK, pre-scaled CK, or an external pin. In addition it can be stopped (no clock).

The different status flags (overflow, compare match and capture event) and controlsignals are found in the Timer/Counter1 Control Registers - TCCR1A and TCCR1B.

The interrupt enable/disable settings for Timer/Counter1 are found in the Timer/Counter

page -106-

© MCS Electronics, 1995-2007

Interrupt Mask Register - TIMSK.

When Timer/Counter1 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period.

The external clock signal is sampled on the rising edge of the internal CPU clock.

The 16-bit Timer/Counter1 features both a high resolution and a high accuracy usage with lower pre-scaling values.

Similarly, high pre-scaling values make the Timer/Counter1 useful for lower speed functions or exact timing functions with infrequent actions.

The Timer/Counter1 supports two Output Compare functions using the Output Compare Register 1 A and B -OCR1A and OCR1B as the data values to be compared to the Timer/Counter1 contents.

The Output Compare functions include optional clearing of the counter on compareA match, and can change the logic levels on the Output Compare pins on both compare matches.

Timer/Counter1 can also be used as a 8, 9 or 10-bit Pulse Width Modulator (PWM). In this mode the counter and the OCR1A/OCR1B registers serve as a dual glitch-free stand-alone PWM with centered pulses.

The Input Capture function of Timer/Counter1 provides a capture of the Timer/Counter1 value to the Input Capture Register - ICR1, triggered by an externalevent on the Input Capture Pin - ICP. The actual capture event settings are defined by the Timer/Counter1 Control Register -TCCR1B.

In addition, the Analog Comparator can be set to trigger the Capture.

page -107-

© MCS Electronics, 1995-2007

AVR Internal Hardware Watchdog timer

The Watchdog Timer

The Watchdog Timer is clocked from a separate on-chip oscillator which runs at approximately 1MHz. This is the typical value at VCC = 5V.

By controlling the Watchdog Timer pre-scaler, the Watchdog reset interval can be adjusted from 16K to 2,048K cycles (nominally 16 - 2048 ms). The Bascom RESET WATCHDOG - instruction resets the Watchdog Timer.

Eight different clock cycle periods can be selected to determine the reset period.

If the reset period expires without another Watchdog reset, the AT90Sxxxx resets and program execution starts at the reset vector address.

page -108-

© MCS Electronics, 1995-2007

AVR Internal Hardware Port B

Port B

Port B is an 8-bit bi-directional I/O port. Three data memory address locations are allocated for the Port B, one each for the Data Register - PORTB, $18($38), Data Direction Register - DDRB, $17($37) and the Port B Input Pins - PINB, $16($36). The Port BInput Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port B output buffers can sink 20mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port B pins with alternate functions are shown in the following table:

When the pins are used for the alternate function the DDRB and PORTB register has to be set according to the alternate function description.

Port B Pins Alternate Functions

Port |

Pin |

Alternate Functions |

PORTB.0 |

T0 |

(Timer/Counter 0 external |

|

|

counter input) |

PORTB.1 |

T1 |

(Timer/Counter 1 external |

|

|

counter input) |

PORTB.2 |

AIN0 |

(Analog comparator positive |

|

|

input) |

PORTB.3 |

AIN1 |

(Analog comparator negative |

|

|

input) |

PORTB.4 |

SS |

(SPI Slave Select input) |

PORTB.5 |

MOSI |

(SPI Bus Master Output/Slave |

|

|

Input) |

PORTB.6 |

MISO |

(SPI Bus Master Input/Slave |

|

|

Output) |

PORTB.7 |

SCK |

(SPI Bus Serial Clock) |

|

|

|

The Port B Input Pins address - PINB - is not a register, and this address enables access to the physical value on each Port B pin. When reading PORTB, the PORTB Data Latch is read, and when reading PINB, the logical values present on the pins are read.

PortB As General Digital I/O

All 8 bits in port B are equal when used as digital I/O pins. PORTB.X, General I/O pin: The DDBn bit in the DDRB register selects the direction of this pin, if DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PORTBn is set (one) when the pin configured as an input pin, the MOS pul up resistor is activated.

To switch the pull up resistor off, the PORTBn has to be cleared (zero) or the pin has to be configured as an output pin.

page -109-