Вступ

Вступ

В наш час електроніка займає все більше і більше місця ,проникаючи в усі сфери життя: починаючи від підкорення космосу і закінчуючи сільським господарством. Мінімізація пристроїв і автоматизація виробництва стимулюють розвиток електронних засобів і мікросхемотехніки та сприяють появі нових і більш досконалих технологій їх виготовлення.

Після купівлі компанії АТІ у AMD з'явилась можливість розробляти і випускати весь ряд ключових компонентів комп’ютерних систем для створення повної власної платформи: CPU, чипсети та відеокарти. Таким продуктом стала платформа Spider.

Основним компонентом Spider є багатоядерні процесори Phenom. Усі чотири ядра розміщенні на одному кристалі, в той час як Intel Core 2 Quad складається з двох «склеєних» двохядерних чипів.

Мікроархітектура Stars, яка спочатку мала назву К10, є розвитком відомої К8. Ще інженери AMD удосконалили попередню вибірку даних та інструкцій і логіку.

Новинкою для процесорів AMD є застосування кеш-пам’яті третього рівня. Її об’єм складає 2 МБ. Завдяки тому, що Agena – нативний чотирьохядерник, кеш третього рівня загальний для усіх ядер: він використовується також для обміну даними між ядрами, це дозволяє суттєво прискорити даний процес в порівнянні з традиційним методом, в якому використовується системна шина. В інтегрованому контролері пам’яті також існує цікаве нововведення – наразі він складається з двох незалежних 64-бітових контролерів. Завдяки цьому, крім стандартного двоканального 128-бітового спареного (gfnged) режиму, з’явився новий – не спарений (unganged). При його застосуванні два 64-бітових контролера пам’яті, які функціонують незалежно, що дає можливість обробляти по дві операції звернення до пам’яті одночасно.

Слід відмітити, що кеш третього

рівня і контролер пам’яті працюють на

своїй частоті, яка в моделях, що

випускаються складає 1,8 ГГц, і мають

окреме  живлення.

Така незалежність дає можливість окремо

управляти частотою та живленням кожного

з чотирьох ядер і контролера пам’яті.

Це використовується в новій версії

Cool’n’Quiet 2.0, яка дозволяє додатково

зменшити енергозатрати CPU – якщо повна

обчислювальна потужність одного або

декількох ядер не потребується, то

напруга і частота на ядрах, які не задіяні

зменшується. Завдяки власній робочій

частоті контролера пам’яті реальна

частота пам’яті тепер завжди точно

відповідає той, що бажається.

живлення.

Така незалежність дає можливість окремо

управляти частотою та живленням кожного

з чотирьох ядер і контролера пам’яті.

Це використовується в новій версії

Cool’n’Quiet 2.0, яка дозволяє додатково

зменшити енергозатрати CPU – якщо повна

обчислювальна потужність одного або

декількох ядер не потребується, то

напруга і частота на ядрах, які не задіяні

зменшується. Завдяки власній робочій

частоті контролера пам’яті реальна

частота пам’яті тепер завжди точно

відповідає той, що бажається.

Була збільшена швидкість роботи шини HyperTransport, яка зв’язує процесор з чипсетом – нова версія HyperTransport 3.0 має пропускну здатність до 20,8 ГБ/с, в той час як у HyperTransport 2.0 вона складає 8 ГБ/с.

Важливою перевагою платформи Spider є спадковість: хоча процесори Phenom використовують роз’єм АМ2+, вони можуть працювати і з платами Socket АМ2. Єдина умова – це наявність оновленого BIOS з підтримкою нових CPU. Більш того, це відноситься і к майбутнім процесорам АМ3.

1 Синтез комбінаційних схем

У пристроях залізничної автоматики та телемеханіки, обчислювальної техніки, в тому числі у мікропроцесорах, існує багато комбінаційних схем. Під комбінаційними схемами розуміють логічні схеми, сигнали на виході яких у кожний момент часу визначається комбінацією вхідних сигналів у той же момент часу.

Синтез комбінаційних схем полягає у визначенні таких способів поєднання деяких найпростіших схем, названих логічними елементами, при яких побудований пристрій реалізує поставлену задачу з перетворення вхідної двійкової інформації.

Функція, яка описує роботу комбінаційних схем називається функцією алгебри логіки (ФАЛ).

ФАЛ – це така функція, яка також як і її змінні приймає значення нуль або одиниця.

Існують різні способи задання ФАЛ:

- словесний опис;

- табличний;

- геометричний;

- числовий;

- координатний.

Також існує декілька форм подання ФАЛ.

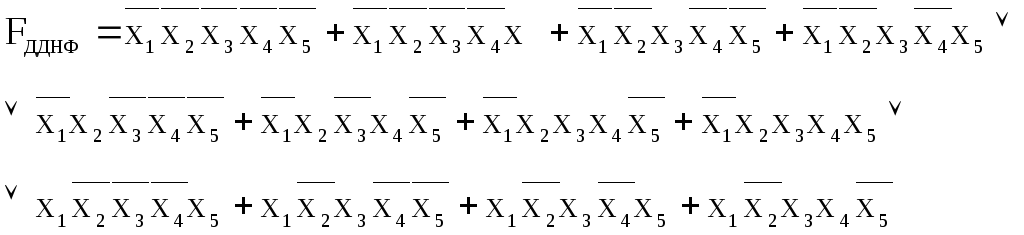

Досконала диз’юнктивна нормальна форма (ДДНФ) – диз’юнкція елементарних кон’юнкцій для тих наборів незалежних змінних, на яких функція приймає значення одиниці.

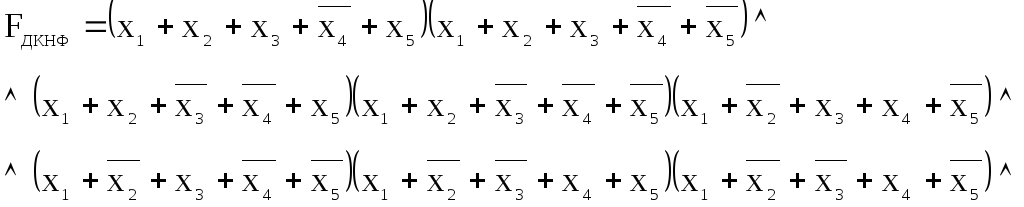

Досконала кон’юнктивна нормальна форма (ДКНФ) – кон’юнкція елементарних диз’юнкцій для тих наборів незалежних змінних, на яких функція приймає значення, яке дорівнює нулю.

1.1 Синтез комбінаційних схем в базисах

Маючи аналітичний вираз ФАЛ можна побудувати комбінаційну схему, яка йому відповідає. Для побудови комбінаційних схем використовуються логічні елементи, які конструктивно оформлені у вигляді інтегральних мікросхем.

Сукупність логічних елементів, які реалізують функції, що відповідають вимогам теореми про функціональну повноту називається базисом.

Синтез комбінаційних схем поділяють на чотири етапи:

1) складання таблиці істинності для ФАЛ, яка описує роботу проектованої логічної схеми;

2) утворення математичної формули для ФАЛ, що описує роботу схеми, яку синтезують, у вигляді ДДНФ або ДКНФ (на підставі таблиці істинності);

3) аналіз отриманої ФАЛ з метою побудови різних варіантів її математичного виразу (на основі законів бульової алгебри) та знаходження найкращого з них у відповідності з тим чи іншим критерієм. На цьому етапі здійснюється мінімізація ФАЛ (процес скорочення кількості входжень незалежних змінних та операцій в аналітичному виразі ФАЛ);

4) утворення функціональної (логічної) схеми пристрою з елементів, які складають вибраний базис.

В даній курсовій роботі розглядається ФАЛ, яка задана числовим способом

![]() ,

,

згідно якої утворюється таблиця істинності (таблиця 1.1).

Таблиця 1.1 – Таблиця істинності для заданої ФАЛ

|

№ |

Х1 |

Х2 |

Х3 |

Х4 |

Х5 |

F |

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

2 |

0 |

0 |

0 |

1 |

0 |

0 |

|

3 |

0 |

0 |

0 |

1 |

1 |

0 |

|

4 |

0 |

0 |

1 |

0 |

0 |

1 |

Продовження

таблиці 1.2

Продовження

таблиці 1.2

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

5 |

0 |

0 |

1 |

0 |

1 |

1 |

|

6 |

0 |

0 |

1 |

1 |

0 |

0 |

|

7 |

0 |

0 |

1 |

1 |

1 |

0 |

|

8 |

0 |

1 |

0 |

0 |

0 |

1 |

|

10 |

0 |

1 |

0 |

1 |

0 |

1 |

|

11 |

0 |

1 |

0 |

1 |

1 |

0 |

|

12 |

0 |

1 |

1 |

0 |

0 |

0 |

|

13 |

0 |

1 |

1 |

0 |

1 |

0 |

|

14 |

0 |

1 |

1 |

1 |

0 |

1 |

|

15 |

0 |

1 |

1 |

1 |

1 |

1 |

|

16 |

1 |

0 |

0 |

0 |

0 |

0 |

|

17 |

1 |

0 |

0 |

0 |

1 |

1 |

|

18 |

1 |

0 |

0 |

1 |

0 |

1 |

|

19 |

1 |

0 |

0 |

1 |

1 |

0 |

|

20 |

1 |

0 |

1 |

0 |

0 |

0 |

|

21 |

1 |

0 |

1 |

0 |

1 |

1 |

|

22 |

1 |

0 |

1 |

1 |

0 |

1 |

|

23 |

1 |

0 |

1 |

1 |

1 |

0 |

|

24 |

1 |

1 |

0 |

0 |

0 |

0 |

|

25 |

1 |

1 |

0 |

0 |

1 |

0 |

|

26 |

1 |

1 |

0 |

1 |

0 |

0 |

|

27 |

1 |

1 |

0 |

1 |

1 |

0 |

|

28 |

1 |

1 |

1 |

0 |

0 |

0 |

|

29 |

1 |

1 |

1 |

0 |

1 |

0 |

|

30 |

1 |

1 |

1 |

1 |

0 |

0 |

|

31 |

1 |

1 |

1 |

1 |

1 |

0 |

Далі на підставі таблиці істинності утворюються математичні формули для ФАЛ, синтезовані у вигляді ДДНФ та ДКНФ:

(1.1)

(1.1)

(1.2)

(1.2)

Після

того як було утворено формули виконується

процес мінімізації. В даному курсовому

проекті застосовано метод карт Карно.

Після

того як було утворено формули виконується

процес мінімізації. В даному курсовому

проекті застосовано метод карт Карно.

Карта Карно являє собою двокоординатну таблицю, в якій в кожній клітинці поставлені у відповідність набори значень змінних логічної функції. Набори, подані сусідніми клітинками, відрізняються значенням тільки однієї змінної. Сусідніми вважаються дві клітинки, які знаходяться поряд, та розташовані у одному стовпці або рядку. Властивість сусідства у карті Карно зручно використовувати для групування окремих одиничних наборів (кон’юнктивних термів) у так звані “підкуби”, або об’єднання в 2n одиничних наборів, де n – ціле число від 0 до 6.

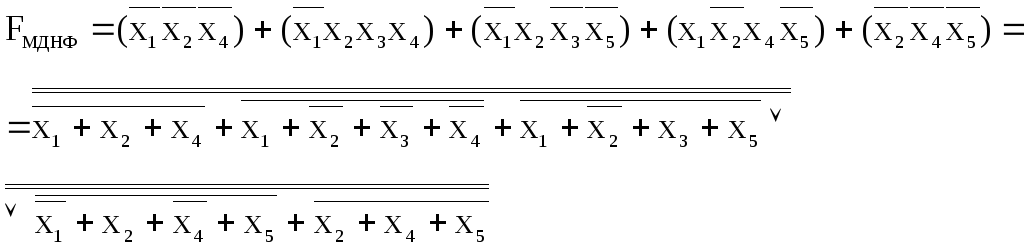

Підкуби утворюються з метою виключення однієї, двох або кількох змінних одиничного набору. Щоб визначити внесок підкуба в мінімальну ФАЛ, потрібно взяти диз’юнкцію одиничних наборів змінних, що входять до підкуба. При цьому змінні, які змінюють своє значення в різних наборах, виключаються за правилом склеювання. При утворенні одиничних підкубів у карті Карно (рисунок 1.1) мінімальне значення функції отримується у вигляді мінімальної диз’юнктивної нормальної форми (МДНФ) (1.3).

Крім МДНФ можна отримати мінімальну кон’юнктивну нормальну форму (МКНФ). Для цього в підкуби об’єднують не одиничні, а нульові набори заданої ФАЛ (рисунок 1.2). Внески підкубів у МКНФ записують у вигляді диз’юнктивних термів, зв’язаних знаком кон’юнкції (1.4).

Утворення підкубів для отримання мінімального значення функції проводиться за таким правилом:

1) утворити двоклітинкові підкуби з наборів, які мають тільки одного сусіда;

2) із

наборів, що залишились, утворити підкуби

максимального розміру, які не перетинаються

(якщо це можливо);

2) із

наборів, що залишились, утворити підкуби

максимального розміру, які не перетинаються

(якщо це можливо);

3) із наборів, що залишились, утворити підкуби максимального розміру, які перетинаються;

4) із наборів, які не мають жодного сусіда, утворити однооклітинкові підкуби;

5) закінчити утворення підкубів, якщо всі набори задіяні.

Рисунок

1.1 – Карта Карно, яка задана для одиничних

наборів

Рисунок

1.1 – Карта Карно, яка задана для одиничних

наборів

(1.3)

(1.3)

Рисунок

1.2 – Карта Карно, яка задана для нульових

наборів

Рисунок

1.2 – Карта Карно, яка задана для нульових

наборів

(1.4)

(1.4)

Після отримання МДНФ та МКНФ ФАЛ до цих виразів застосовано теорему Де Моргана. З її допомогою дані вирази приведено до вигляду, який можна реалізувати в базисі Пірса.

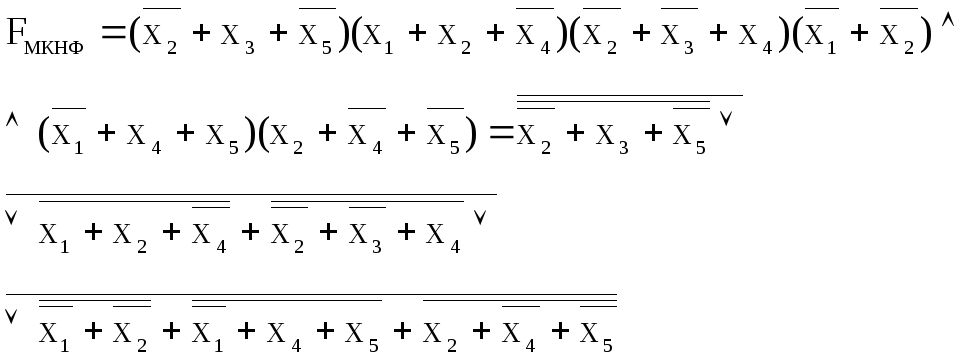

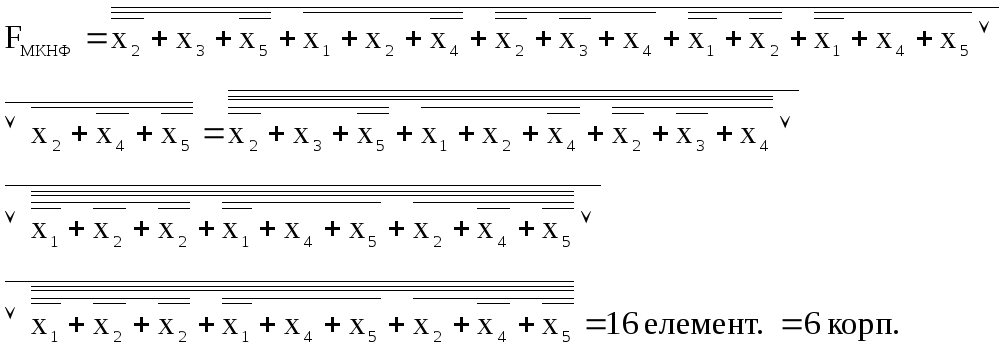

Далі вираз МКНФ перетворено у рівняння (1.5), для синтезування схеми заданої ФАЛ на мікросхемах 1533ЛА4 (рисунок1.3).

(1.5)

(1.5)

1.2 Синтез

комбінаційних схем на мультиплексорах

1.2 Синтез

комбінаційних схем на мультиплексорах

В складі різноманітних серій інтегральних мікросхем, які застосовуються в пристроях залізничної автоматики, єлементи середньої степені інтеграції – комутатори (мультиплексори). Комутатор – це мікросхема, яка має інформаційні входи, входи дозволу роботи (строби), управляючі входи та один вихід. При подачі на стробуючий вхід дозволяючого сигналу (0 або 1) – робота комутатора дозволена. Після цього при подачі на управляючі входи відповідного сигналу у вигляді двійкового коду до виходу комутатора підключається один із його інформаційних входів.

Для синтезу на комутаторах типу 555КП1 комбінаційної схеми дана аналітичним способом ФАЛ:

![]() .

.

Спочатку заданий вираз слід перетворити у ДДНФ (1.6):

(1.6)

(1.6)

Після перетворення ФАЛ у ДДНФ отриманий вираз представляється у вигляді таблиці істинності (таблиця 1.2).

Таблиця 1.2 – Таблиця істинності для заданої ФАЛ

-

Х1

Х2

Х3

Х4

Х5

F

B

0

0

0

0

0

0

1

B0=1

1

0

0

0

0

1

1

2

0

0

0

1

0

1

B1=1

3

0

0

0

1

1

1

4

0

0

1

0

0

1

B2=1

5

0

0

1

0

1

1

6

0

0

1

1

0

1

B3=1

7

0

0

1

1

1

1

8

0

1

0

0

0

1

B'0=1

9

0

1

0

0

1

1

10

0

1

0

1

0

1

B'1=

11

0

1

0

1

1

0

12

0

1

1

0

0

1

B'2=1

13

0

1

1

0

1

1

14

0

1

1

1

0

1

B'3=1

15

0

1

1

1

1

1

16

1

0

0

0

0

1

B''0=1

17

1

0

0

0

1

1

18

1

0

0

1

0

1

B''1=1

19

1

0

0

1

1

1

20

1

0

1

0

0

1

B''2=1

21

1

0

1

0

1

1

22

1

0

1

1

0

1

B''3=1

23

1

0

1

1

1

1

24

1

1

0

0

0

1

B'''0=1

25

1

1

0

0

1

1

26

1

1

0

1

0

1

B'''1=1

27

1

1

0

1

1

1

28

1

1

1

0

0

1

B'''2=1

29

1

1

1

0

1

1

30

1

1

1

1

0

1

B'''3=1

31

1

1

1

1

1

1

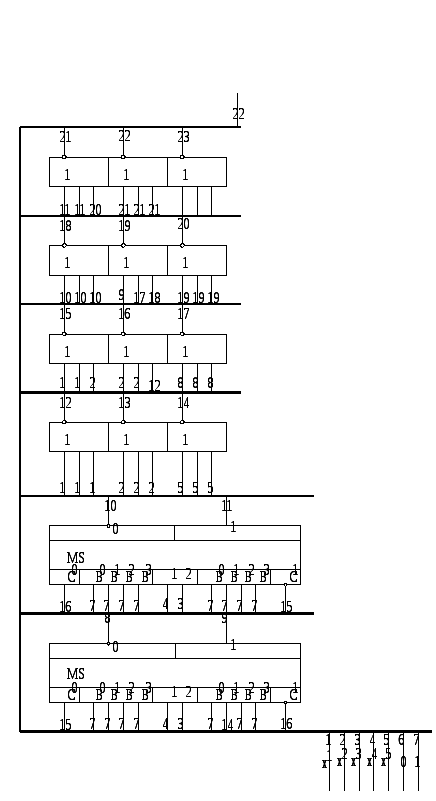

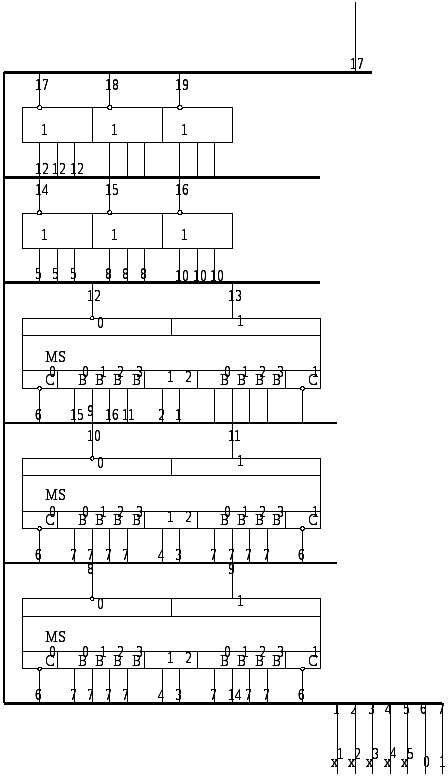

Для синтезування заданої ФАЛ на комотаторах типу 555КП1 (рисунок 1.4) виконуються такі дії: на управляючі входи мультиплексорів (рисунок 1.4) подаються сигнали які відповідають змінним х3 та х4;на інформаційні входи подаються сигнали отримані шляхом співставлення змінної х5 зі стовбчиком значень функції F (таблиця 1.2), при цьому розглядуючи строки по-парно. Якщо функція не змінюється при зміні значень х5, то на вхід подається сигнал, який відповідає значенню функції. А якщо із зміною х5 змінюється і функція, то на вхід подається значення, що відповідає змінній х5.

Для чергування роботи комутаторів складається таблиця істиності для стробуючих входів (таблиця 1.3) та відповідні рівняння (1.7).

Таблиця

1.3 – Таблиця стробуючих входів

Таблиця

1.3 – Таблиця стробуючих входів

-

Х1

Х2

С1

С2

С3

С4

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

1

1

0

0

0

1

![]() ;

;

![]() ;

;

![]() ;

;

![]() . (1.7)

. (1.7)

Виходи елементів об’єднуьтся за допомогою базиса Пірса, виконаного на мікросхемах 1533ЛА4.

Для побудови ФАЛ на трьох комутаторах 555 КП1 виконуються такі дії: на управляючі входи перших двох мультиплексорів подаються змінні х3 та х4; на їх інформаційні входи подаються значення, що відповідають таблиці істиності (таблиця 1.2); на управляючі входи третьго комутатора подаються виходи перших двох комутаторів; на його інформаційні входи – змінні х1 та х2. На стробуючі входи усіх комутаторів подається 0 або 1 – усі мультиплексори повинні працювати одночасно. Значення функції знімається з виходу останнього комутатора.

з

з