Разработка и описание структурной схемы эвм

В данном курсовом проекте разрабатывается структурная схема гипотетической ЭВМ, функциональная схема отдельного блока и алгоритм его работы.В состав ЭВМ входят:

центральный процессор(центральное обрабатывающее устройство и микропрограмное устройство управления), оперативна память, блок синхронизации, система прерывания программ, таймер,

система ввода-вывода, монитор и клавиатура, накопитель на гибких магнитных дисках, «Винчестер».

ЭВМ – двухадресная, длина команды – переменная.

Разрядность ЭВМ – 16.

Емкость оперативной памяти – 16Мб.

Индивидуальные исходные данные:

Структура ЭВМ - магистральная 2-х шинная.

Оперативная память – страничная виртуальная.

Система прерываний – последовательная макро.

Ввод – ПДП.

Кэш – TLB

Система контроля – --------------------------------------

AB\DB

ЦП

TLB

CB

ОП

УУОП Винчестер Контроллер

интерфейса клавиатуры Адаптер

Таймер

Система

прерывания программ

НГМД

Клавиатура Монитор

Рис.1

Центральный процессор

Команды, операнды (из ОП)

Результаты операций (в ОП)

……

Запросы прерываний

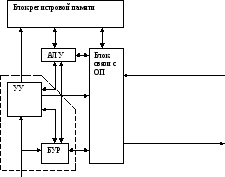

Рис.2 Упрощенная структурная схема процессора

Процессор занимает центральное место в структуре ЭВМ, так как он осуществляет управление взаимодействием всех устройств, входящих в состав ЭВМ. Процессор дешифрирует и выполняет команды программы, организует обращения к оперативной памяти, в нужных случаях инициирует работу ПУ, воспринимает и обрабатывает запросы прерывания. Упрощенная схема процессора приведена на рис. 2, где изображены только его основные части:

- Арифметико-логическое устройство (АЛУ) - производит логические и арифметические операции над данными.

- управляющее устройство (УУ) - вырабатывает управляющие сигналы для выборки очередной команды из памяти, дешифрирования кода команды, формирования адресов операндов, выборки операндов из памяти, передачи их в АЛУ, выполнения в АЛУ операции, предусмотренной кодом команды, передачи полученного в АЛУ результата операции в память, инициирования операций ввода-вывода, организации реакции процессора на запросу прерывания, поступающие от узлов самого процессора, других устройств, в том числе ПУ.

- блок управляющих регистров (БУР) - предназначен для временного хранения управляющей информации. Содержит регистры и счетчики, участвующие в управлении вычислительным процессом: регистры, хранящие информацию о состоянии процессора, регистр-счетчик адреса команды – счетчик команд, счетчики тактов, регистр запросов прерывания и др.

- блок регистровой памяти (местная память) - используется для повышения быстродействия и логических возможностей процессора.

- блок связи с ОП - организует обмен информацией процессора с оперативной памятью и защиту участков ОП от недозволенных данной программе обращений, а также связь ЦП с ПУ.

С

истема

прерывания программ (для внешних

прерываний) – последовательная макро

.Это означает, что имеется общая линия

для сигнала прерывания от периферии к

процессору, а также последовательная

линия подтверждения прерывания.

Запоминание состояния процессора идет

на макро уровне (уровне команд).

истема

прерывания программ (для внешних

прерываний) – последовательная макро

.Это означает, что имеется общая линия

для сигнала прерывания от периферии к

процессору, а также последовательная

линия подтверждения прерывания.

Запоминание состояния процессора идет

на макро уровне (уровне команд).

ЦП

«Дейзи»-цепочка

ПУ1 ПУk

Способ формирования и передачи в ЦПУ вектора прерывания.

Периферийное устройство выставляет запрос на прерывание на общую линию. В ответ на это процессор формирует сигнал подтверждения прерывания. Линия подтверждения прерывания при этом разрывается (на устройстве, которое выставляло запрос) По его приходу периферийное устройство выставляет вектор прерывания на шину данных.

Принятый способ возврата из прерываний и его реализация.

Начало фронта подтверждения прерывания инициирует начало передачи вектора прерывания (через некоторое время задержки).Затем на устройстве линия подтверждения разрывается. Для того, чтобы

процессор

знал, что на шине вектор,

процессор

знал, что на шине вектор,

Запрос

прерывания сигнал подтверждения

через канал шины

Запрос

прерывания сигнал подтверждения

через канал шины

управления

возвращается в процессор.

управления

возвращается в процессор.

Подтверждение

Идет запись и обработка вектора

Подтверждение

Идет запись и обработка вектора

прерывания.

По окончании обработки идет

прерывания.

По окончании обработки идет

вектор

восстановление состояния.Далее

вектор

восстановление состояния.Далее

выполняется команда, следующая за исходной. Таким образом осуществляется возврат из прерывания. Предусмотрен защитный механизм(механизм таймаута).По отправке сигнала подтверждения запускают таймер. Если сигнал подтверждения не возвращается (сбой в шине, или неисправность устройства), то через установленное время происходит принудительный возврат процессора в исходное состояние.

Запоминание и восстановление состояния прерываемой программы.

По приходу сигнала запроса прерывания происходит запоминание текущей программы. Так как запоминание идет на макро уровне, то ожидается завершение текущей команды, затем сохраняются значения Регистров Общего Назначения (РОН)+регистр флагов +указатель текущей команды IP CS ( получается уже следующей команды).После прихода вектора выполняется соответственная программа обработки по завершении которой происходит восстановление состояния прерванной програмы. Так как текущая команда выполнена, то начинается выполнение следующей.

Управление приоритетами.

В случае, когда запрос на прерывание выставляют одновременно два и более устройств, необходимо решать порядок поступления векторов на процессор. Высшим приоритетом обладает ПУ1, затем ПУ2 и так далее до ПУk. Данная процедура обеспечивается тем, что ключ на линии подтверждения в устройстве при отправке вектора, размыкается и сигнал подтверждения прерывания не доходит до следующих(менее приоритетных) устройств.

В случае внутренних прерываний процессор выполняет соответственную процедуру.