Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования «Ивановский государственный энергетический университет имени В.И. Ленина»

Кафедра электроники и микропроцессорных систем

ОТЧЕТ

По лабораторной работе №4

Выполнили студенты гр.II-42

Маров Д.А.

Никонов К.Н.

Проверил

Аббясов А.М.

Иваново 2012

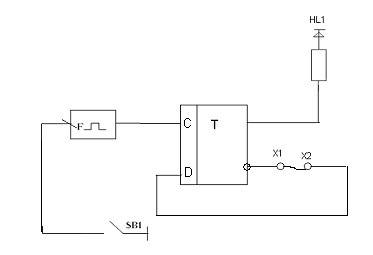

1)Счётный Т-триггер

Cхема:

Временная диаграмма:

С

D

HL1

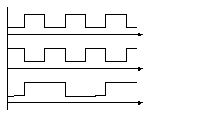

2) Двухразрядные последовательный и параллельный регистры

2.1) Параллельный регистр:

Схема:

Временная диаграмма:

2.2) Последовательный регистр

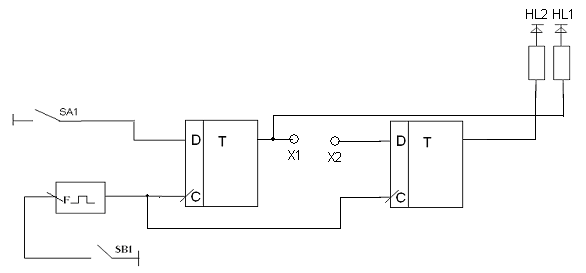

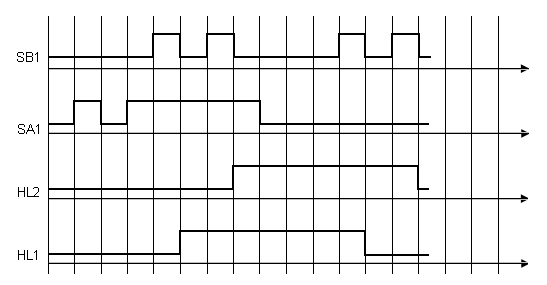

Схема:

Временная диаграмма:

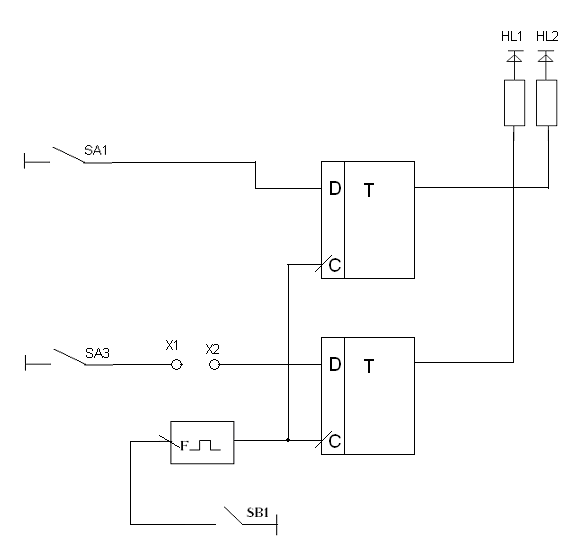

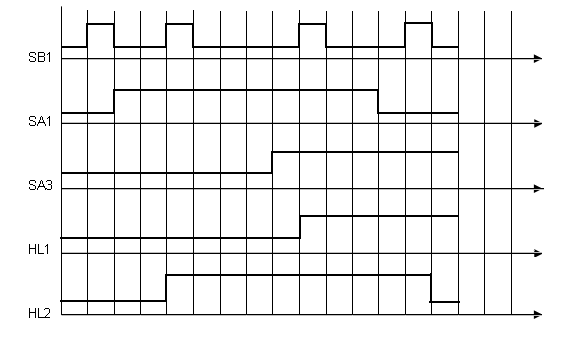

3) Последовательный и параллельный регистры

3.1) Последовательный регистр

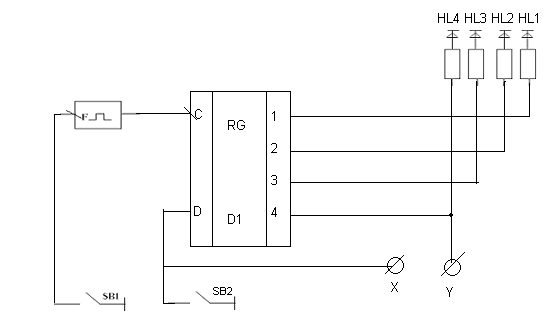

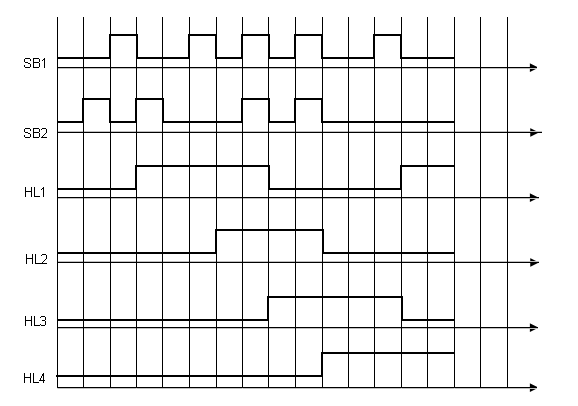

Схема:

Временная диаграмма:

3.2) Параллельный регистр

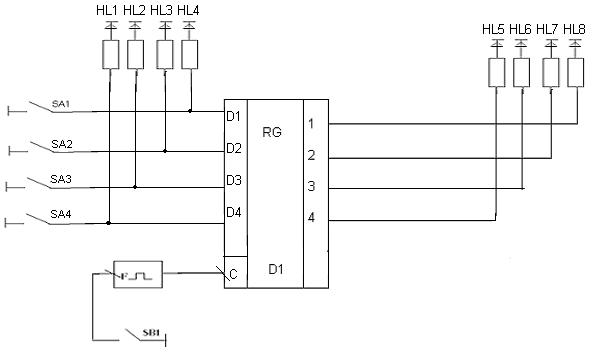

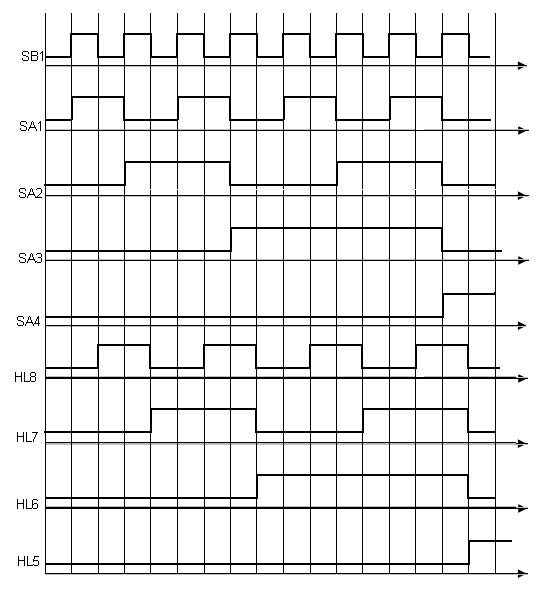

Схема:

Временная диаграмма:

4) Данная схема работает в двух режимах: при SA5=1 – последовательном и SA5=0 – параллельном. При параллельном режиме работы управление схемой производится подачей сигналов с SA1-SA4 и SB1, SB3. При подаче сигнала с SB1 мы записываем входной сигнал мы записываем входной сигнал в регистр. При этом сумматор выведет результат сложения входных данных и данных с регистра на дисплей HG1. При получении результата суммирования выходящего за пределы цифр 16-ричной системы загорается индикатор HL1. При последовательном режиме работы происходит изменения в управлении регистром, в данном случае он управляется с помощью сигналов, идущих с SB1 и SB2. SB3 в обоих случаях увеличивает результат суммирования на один.