- •9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

- •9.1 Комбінаційні цифрові пристрої (кцп)

- •9.1.1 Аналіз і синтез кцп

- •9.1.1.1 Аналіз кцп

- •9.1.1.2 Синтез кцп

- •9.1.2 Типові кцп

- •9.1.2.1 Шифратори та дешифратори

- •9.1.2.1.1 Шифратори двійкового коду

- •9.1.2.1.2 Шифратори двійково-десяткового коду

- •9.1.2.1.3 Дешифратори двійкового коду

- •9.1.2.1.4 Дешифратор bcd - коду всемисегментний код

- •9.1.2.1.4.1 Семисегментні індикатори на світлодіодах

- •9.1.2.2 Мультиплексори й демультиплексори

- •9.1.2.2.1 Мультиплексори

- •9.1.2.2.2 Демультиплексори

- •9.1.2.2.3 Мультиплексори-селектори (мультиплексори-демультиплексори)

- •9.1.2.3 Cуматори і напівсуматори

- •9.1.2.4 Пристрої контролю парності (пкп)

- •9.1.2.5 Цифрові компаратори

- •9.1.3 Використання для проектування кцп мультиплексорів, дешифраторів і постійного запам’ятовуючого пристрою

- •9.1.3.1 Побудова кцп на мультиплексорах

- •9.1.3.2 Побудова кцп на дешифраторах

- •9.1.3.3 Побудова кцп на постійному запам’ятовуючому пристрої (пзп)

- •9.2 Послідовні цифрові пристрої

- •9.2.1 Тригери

- •9.2.1.1 Тригери на логічних елементах

- •9.2.1.1.1 Rs - тригери

- •9.2.1.1.1.1 Асинхронні rs - тригери

- •9.2.1.1.1.2 Синхронні rs - тригери

- •9.2.1.1.2 Т-тригери (тригери з лічильним входом)

- •9.2.1.1.3 D - тригери (тригери затримки)

- •9.2.1.1.4 Jk - тригери

- •9.2.1.2 Тригери у інтегральному виконанні

- •9.2.2 Регістри

- •9.2.2.1 Паралельні регістри

- •9.2.2.2 Послідовні (зсуваючі) регістри

- •9.2.2.3 Регістри зсуву

- •9.2.2.4 Послідовно-паралельні і паралельно-послідовні регістри

- •9.2.2.5 Регістри у інтегральному виконанні

- •9.2.3 Лічильники

- •9.2.3.1 Асинхронний двійковий лічильник, що підсумовує, з послідовним перенесенням

- •9.2.3.2 Асинхронний двійковий лічильник, що віднімає, із послідовним перенесенням

- •9.2.3.3 Асинхронні реверсивні двійкові лічильники з послідовним перенесенням

- •9.2.3.4 Синхронний лічильник з наскрізним перенесенням

- •9.2.3.5 Десяткові лічильники

- •9.2.3.6 Лічильники в інтегральному виконанні

- •9.2.4 Подільники частоти

- •9.2.5 Розподілювачі

9.1.2.2 Мультиплексори й демультиплексори

У сучасних мікропроцесорних пристроях управління й однокристальних мікроЕОМ широко застосовуються КЦП, що здійснюють підключення (комутування) виходу одного з паралельно увімкнених цифрових пристроїв на загальну шину або, навпаки, з'єднання загальної шини з входом одного з декількох паралельно увімкнених пристроїв. Ці функції виконують пристрої, що називаються мультиплексорами й демультиплексорами.

9.1.2.2.1 Мультиплексори

Мультиплексор - це комбінаційний цифровий пристрій, що з'єднує (комутує) один із декількох інформаційних вхідних сигналів з одним загальним виходом. Приклад позначення мультиплексора на електричних схемах показаний на рисунку 9.14, а.

Пристрій містить вісім інформаційних входів: D0, D1, ..., D7, три адресні входи: А0, А1, А2 і один вхід V, що синхронізує.

У залежності від комбінації адресних сигналів А0, А1, А2 він забезпечує комутацію одного з восьми інформаційних вхідних сигналів Di на загальний вихід F. Нульовий синхросигнал на вході V дозволяє передачу інформації з обраного входу на вихід.

Булевий вираз, що описує функціонування аналізованого мультиплексора має вигляд

__ __ __ __ __ __ __

Y = A2 . A1 . A0 . V . D0 A2 . A1 . A0 . V . D1

__ __ __ __ __

A2 . A1 . A0 . V . D2 A2 . A1 . A0 . V . D3

__ __ __ __ __

A2 . A1 . A0 . V . D4 A2 . A1 . A0 . V . D5

__ __ __

A2 . A1 . A0 . V . D6 A2 . A1 . A0 . V . D7 (9.5)

Мультиплексор можна реалізувати за допомогою логічних елементів заданого базису. У його структуру можна ввести і більш складні цифрові пристрої, наприклад, перетворювач двійкового коду в десятковий (дешифратор).

Схема реалізує булевий вираз

__ __ __ __ __ __ __

Y = A1 . A0 . V . D0 + A1 . A0 . V . D1 + A1 . A0 . V . D2+

__

+ A1 . A0 . V . D3 . ( 9.6 )

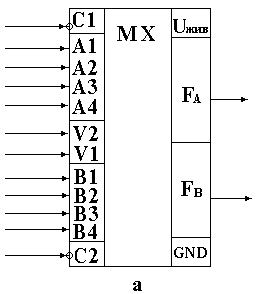

Існують мультиплексори в інтегральному виконанні, наприклад, ІМС К555КП2 (рисунок 9.15).

Рисунок 9.15

Мультиплексор КП2 (рисунок 9.15, а) складається з двох частин, кожна з яких містить чотири інформаційних канали А1...А4 (В1...В4); і один вихід Fа (Fв). Управляючі (адресні) входи V2, V1 - спільні, тобто сигнали на них одночасно впливають на обидві частини ІМС. Правила роботи схеми відбиває таблиця 9.5.

Таблиця 9.5

|

Стробуючі входи С1, С2 |

Управляючі входи V2 V1 |

Вихід Fа |

Вихід Fв | |

|

0 |

0 |

0 |

А1 |

В1 |

|

0 |

0 |

1 |

А2 |

В2 |

|

0 |

1 |

0 |

А3 |

В3 |

|

0 |

1 |

1 |

А4 |

В4 |

|

1 |

Х |

Х |

0 |

0 |

|

Примітка: Х - будь-яке значення: 0 або 1 | ||||

Для збільшення кількості каналів об'єднують декілька мультиплексорів, використовуючи для цього стробуючі входи, як це зображено на рисунку 9.15,б.