- •9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

- •9.1 Комбінаційні цифрові пристрої (кцп)

- •9.1.1 Аналіз і синтез кцп

- •9.1.1.1 Аналіз кцп

- •9.1.1.2 Синтез кцп

- •9.1.2 Типові кцп

- •9.1.2.1 Шифратори та дешифратори

- •9.1.2.1.1 Шифратори двійкового коду

- •9.1.2.1.2 Шифратори двійково-десяткового коду

- •9.1.2.1.3 Дешифратори двійкового коду

- •9.1.2.1.4 Дешифратор bcd - коду всемисегментний код

- •9.1.2.1.4.1 Семисегментні індикатори на світлодіодах

- •9.1.2.2 Мультиплексори й демультиплексори

- •9.1.2.2.1 Мультиплексори

- •9.1.2.2.2 Демультиплексори

- •9.1.2.2.3 Мультиплексори-селектори (мультиплексори-демультиплексори)

- •9.1.2.3 Cуматори і напівсуматори

- •9.1.2.4 Пристрої контролю парності (пкп)

- •9.1.2.5 Цифрові компаратори

- •9.1.3 Використання для проектування кцп мультиплексорів, дешифраторів і постійного запам’ятовуючого пристрою

- •9.1.3.1 Побудова кцп на мультиплексорах

- •9.1.3.2 Побудова кцп на дешифраторах

- •9.1.3.3 Побудова кцп на постійному запам’ятовуючому пристрої (пзп)

- •9.2 Послідовні цифрові пристрої

- •9.2.1 Тригери

- •9.2.1.1 Тригери на логічних елементах

- •9.2.1.1.1 Rs - тригери

- •9.2.1.1.1.1 Асинхронні rs - тригери

- •9.2.1.1.1.2 Синхронні rs - тригери

- •9.2.1.1.2 Т-тригери (тригери з лічильним входом)

- •9.2.1.1.3 D - тригери (тригери затримки)

- •9.2.1.1.4 Jk - тригери

- •9.2.1.2 Тригери у інтегральному виконанні

- •9.2.2 Регістри

- •9.2.2.1 Паралельні регістри

- •9.2.2.2 Послідовні (зсуваючі) регістри

- •9.2.2.3 Регістри зсуву

- •9.2.2.4 Послідовно-паралельні і паралельно-послідовні регістри

- •9.2.2.5 Регістри у інтегральному виконанні

- •9.2.3 Лічильники

- •9.2.3.1 Асинхронний двійковий лічильник, що підсумовує, з послідовним перенесенням

- •9.2.3.2 Асинхронний двійковий лічильник, що віднімає, із послідовним перенесенням

- •9.2.3.3 Асинхронні реверсивні двійкові лічильники з послідовним перенесенням

- •9.2.3.4 Синхронний лічильник з наскрізним перенесенням

- •9.2.3.5 Десяткові лічильники

- •9.2.3.6 Лічильники в інтегральному виконанні

- •9.2.4 Подільники частоти

- •9.2.5 Розподілювачі

9.2.1.1.4 Jk - тригери

Найбільш універсальні серед синхронних тригерів .

а

б

Рисунок 9.40

Рисунок 9.40, в

Таблиця 9.13

Розглянемо роботу JK-тригера. Початковий стан схеми - нульовий (UQ=0 ) (рисунок 9.40,в). При надходженні зрізу першого тактового імпульсу (момент t1) сигнал на J-вході дорівнює 1, а на К-вході - 0. Тому тригер переключається в одиничний стан. Зрізом другого тактового імпульсу схема переключається в нульовий стан (момент t2), тому що в цей час J=0, а К=1. В момент t3 обидва керуючих сигнали J=K=0, тому стан схеми не змінюється (Qt+1=Qt). При надходженні зрізу 4-го синхроімпульсу (момент t4) J=K=1, тому тригер переключається в становище, протилежне початковому,

__

(Q t+1 = Q t ).

На основі універсального JK-тригера може бути побудований ряд інших тригерів.

Синхронний RS-тригер. Ототожнимо J=S і K=R. При забороні комбінації J=S=1 і K=R=1 таблиця зводиться до таблиці істинності RS-тригера (таблиця 9.11). Тому розглянута схема (рисунок 9.40) може використовуватися в якості двотактного синхронного RS-тригера.

а б

Рисунок 9.41

D-тригер. У цьому тригері J=K= D , тобто крім тактового є тільки один вхід D (рисунок 9.41,б). З таблиці 9.13 (2-й і 3-й рядки) видно, що в D-тригері Qt+1=D, тобто останній запам'ятовує сигнал на вході D у момент зрізу тактового імпульсу і береже його до наступного синхросигналу.

9.2.1.2 Тригери у інтегральному виконанні

В сучасних серіях ІМС існує велика кількість різноманітних тригерів.

Нижче як приклад наведено позначення на електричних схемах двох тригерів широкого використання, що випускаються у вигляді інтегральної мікросхеми (рисунок 9.42). Мікросхема К555 ТМ2 включає два D-тригера с додатковими S і R входами для встановлення схеми у початковий стан (рисунок 9.42,а). Активними сигналами на S і R входах постають низькі рівні напруг (логічні нулі).

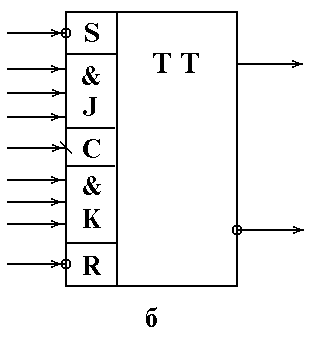

Мікросхема К555 ТВ1 (рисунок 9.42,б) містить один JK-тригер, який включає два асинхронних R і S входи для установлення схеми у початковий стан і два додаткових тривходових кон’юнктора, включених на J і K входах. Додаткові елементи І реалізують логічні функції

J = J1 . J2 . J3 , ( 9.19 )

K= K1 . K2 . K3 .

Це розширює можливості JK-тригера , наприклад, спрощує побудову синхронних лічильників на подібних мікросхемах.

Рисунок 9.42