- •9 Функціональні пристроїкомп'ютерної (цифрової) електроніки

- •9.1 Комбінаційні цифрові пристрої (кцп)

- •9.1.1 Аналіз і синтез кцп

- •9.1.1.1 Аналіз кцп

- •9.1.1.2 Синтез кцп

- •9.1.2 Типові кцп

- •9.1.2.1 Шифратори та дешифратори

- •9.1.2.1.1 Шифратори двійкового коду

- •9.1.2.1.2 Шифратори двійково-десяткового коду

- •9.1.2.1.3 Дешифратори двійкового коду

- •9.1.2.1.4 Дешифратор bcd - коду всемисегментний код

- •9.1.2.1.4.1 Семисегментні індикатори на світлодіодах

- •9.1.2.2 Мультиплексори й демультиплексори

- •9.1.2.2.1 Мультиплексори

- •9.1.2.2.2 Демультиплексори

- •9.1.2.2.3 Мультиплексори-селектори (мультиплексори-демультиплексори)

- •9.1.2.3 Cуматори і напівсуматори

- •9.1.2.4 Пристрої контролю парності (пкп)

- •9.1.2.5 Цифрові компаратори

- •9.1.3 Використання для проектування кцп мультиплексорів, дешифраторів і постійного запам’ятовуючого пристрою

- •9.1.3.1 Побудова кцп на мультиплексорах

- •9.1.3.2 Побудова кцп на дешифраторах

- •9.1.3.3 Побудова кцп на постійному запам’ятовуючому пристрої (пзп)

- •9.2 Послідовні цифрові пристрої

- •9.2.1 Тригери

- •9.2.1.1 Тригери на логічних елементах

- •9.2.1.1.1 Rs - тригери

- •9.2.1.1.1.1 Асинхронні rs - тригери

- •9.2.1.1.1.2 Синхронні rs - тригери

- •9.2.1.1.2 Т-тригери (тригери з лічильним входом)

- •9.2.1.1.3 D - тригери (тригери затримки)

- •9.2.1.1.4 Jk - тригери

- •9.2.1.2 Тригери у інтегральному виконанні

- •9.2.2 Регістри

- •9.2.2.1 Паралельні регістри

- •9.2.2.2 Послідовні (зсуваючі) регістри

- •9.2.2.3 Регістри зсуву

- •9.2.2.4 Послідовно-паралельні і паралельно-послідовні регістри

- •9.2.2.5 Регістри у інтегральному виконанні

- •9.2.3 Лічильники

- •9.2.3.1 Асинхронний двійковий лічильник, що підсумовує, з послідовним перенесенням

- •9.2.3.2 Асинхронний двійковий лічильник, що віднімає, із послідовним перенесенням

- •9.2.3.3 Асинхронні реверсивні двійкові лічильники з послідовним перенесенням

- •9.2.3.4 Синхронний лічильник з наскрізним перенесенням

- •9.2.3.5 Десяткові лічильники

- •9.2.3.6 Лічильники в інтегральному виконанні

- •9.2.4 Подільники частоти

- •9.2.5 Розподілювачі

9.2.1.1.2 Т-тригери (тригери з лічильним входом)

Такий тригер містить лічильний вхід, що позначається буквою Т, і переключається кожним імпульсом на Т-вході.

а в

б

Рисунок 9.34

Тригер виконаний на основі синхронного двоступінчатого RSC-тригера з динамічним синхровходом, охопленого двома зворотніми зв'язками.

В момент зрізу лічильних вхідних імпульсів тригер переключається в протилежний стан Qt+1 = Q-t. На рисунку приведені діаграми часу, що пояснюють роботу Т-тригера. Початковий стан схеми - одиничний ( UQ=1 ). Зрізом кожного лічильного імпульсу вихідний сигнал змінює своє значення. Період вихідних імпульсів ТВИХ = 2 ТВХ , а частота fВИХ = fВХ/2 , тобто Т-триггер ділить вхідну частоту на 2.

Рисунок 9.35

На рисунку 9.34,в приведене позначення на електричних схемах Т-тригера, що переключається перепадом з 0 в 1 на лічильному вході.

9.2.1.1.3 D - тригери (тригери затримки)

Містять інформаційний (D) вхід і тактовий (синхро) вхід (рисунок 9.36).

а б

Рисунок 9.36

Існують однотактні D-тригери (рисунок 9.36,а), що переключаються потенціалом або імпульсом на тактовому вході, і двотактні D-тригери, що переключаються динамічним сигналом (перепадом), наприклад, з 1 в 0 (рисунок 9.36,б).

б

а

б

Рисунок 9.37

В момент надходження тактового імпульсу D-тригер переключається в стан, обумовлений сигналом на інформаційному вході D, тобто схема запам'ятовує сигнал на вході D у момент надходження синхроімпульсу (Qt+1=D) і береже його до наступного тактового імпульсу. Затримка дорівнює інтервалу часу між моментами приходу інформаційного сигналу на D-вхід і надходженням синхросигналу на С-вхід : tзат1 = t2 - t1 ; tзат2 = t4 - t3 (рисунок 9.37,б). D-тригери широко застосовуються в якості елементів пам'яті, спроможних зберігати 1 біт інформації.

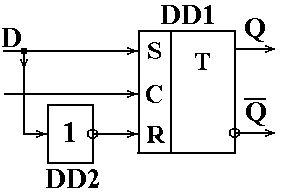

Нижче показані: позначення на електричних схемах (рисунок 9.38,а) і принципові схеми (рисунок 9.38,б) двотактного D-тригера, що переключається перепадом з 1 в 0 на динамічному синхровході С.

б

в Рисунок 9.38

Тригер виконаний на основі двох однотактних RSC-тригерів (DD1, DD2) і двох інверторів (DD3, DD4).

D-тригер можна використовувати в якості тригера з рахунковим входом (Т-тригера), якщо з'єднати його виводи як показано на рисунку 9.38,в.