4 семестр (2 курс)лала / ЭП (Электронные приборы) / Техническая электроника 2000 (Ткаченко Ф.А

.).pdf

311

Поскольку у идеального ОУ KU→∞, Rвx→∞, а ток смещения очень мал по сравнению с током обратной связи, то согласно закона Кирхгофа

I1+I2+I3=Iос. (11.19)

Вследствие того, что инвертирующий вход имеет практически нулевой потенциал, то в нем отсутствует взаимное влияние входных сигналов. Выражение (11.19) может быть представлено в виде

I |

= |

U1 |

; I |

2 |

= |

U2 |

; I |

3 |

= |

U3 |

|

; I |

ос |

= − |

Uвых |

; |

|

||||||

|

|

|

|

|

|

||||||||||||||||||

1 |

|

R1 |

|

R2 |

|

R3 |

|

|

|

|

Rос |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

Rос |

|

|

|

Rос |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

Rос |

(11.20) |

||||||||||

Uвых = − U1 |

|

|

|

|

+ U2 |

|

|

|

|

+ U3 |

|

|

|

|

|||||||||

R1 |

|

R2 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

R3 |

|

|||||||||

и при Rос=R1=R2=R3 Uвых = –(U1+U2+U3).

Следовательно на выходе получается инвертированная сумма входных напряжений. Если R1≠R2≠R3, то на выходе получается инвертированная сумма входных напряжений (11.20) с различными масштабными коэффициентами. Инвертирующий сумматор объединяет в себе функции сумматора и усилителя при сохранении простоты схемы. Резистор R служит для компенсации сдвига нуля на выходе ОУ, вызванного временными и температурными колебаниями входного тока. Сопротивление R выбирают токай величины, чтобы эквивалентные сопротивления, подключенные ко входам ОУ были одинаковы: R=Roc||R1||R2||R3.

11.9.2. Неинвертирующий сумматор

Схема неинвертирующего сумматора, который строится на базе неинвертирующего усилителя, приведена на рис. 11.11. Так как при U0=0 напряжения на инвертирующем и неинвертиющем входах равны, то

Uн = |

R |

Uвых. |

(11.21) |

|

R + Rос |

||||

|

|

|

Учитывая, что Rвx ОУ по неинвертирующему входу очень велико, то входной ток равен 0. Согласно закона Кирхгофа можно записать

U1 − Uн |

+ |

U2 − Uн |

+ |

U3 − Uн |

= 0. |

(11.22) |

|

|

|

||||

R |

R |

R |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

312 |

Откуда U1 + U2 + U3 = n |

R |

|

Uвых , где n – число входов, и |

|

||||||||||

|

|

|

|

|||||||||||

|

|

|

R + Rос |

|

|

|

R + Rос |

|

|

|

|

|||

U |

вых |

= |

(U |

+ U |

2 |

+ U |

3 |

). |

|

|

|

(11.23) |

||

|

|

|

|

|||||||||||

|

|

n |

1 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Если |

же |

в |

схеме |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

(рис. 11.11) еще подаются |

||||

|

|

|

|

|

|

|

|

|

|

сигналы на инвертирующие |

||||

|

|

|

|

|

|

|

|

|

|

входы, то схема выполняет |

||||

|

|

|

|

|

|

|

|

|

|

операцию |

|

сложения- |

||

|

|

|

|

|

|

|

|

|

|

вычитания. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Для правильной рабо- |

|||

|

|

|

|

|

|

|

|

|

|

ты |

сумматора |

необходимо |

||

|

|

|

|

|

|

|

|

|

|

сбалансировать инвертирую- |

||||

|

|

|

|

|

|

|

|

|

|

щий |

и неинвертирующий |

|||

|

|

|

|

|

|

|

|

|

|

коэффициент усиления, т.е. |

||||

|

|

|

|

|

|

|

|

|

|

обеспечить |

равенство |

сумм |

||

|

|

|

|

|

|

|

|

|

|

коэффициентов |

усиления |

|||

инвертирующей и неинвертирующей частей схемы.

11.9.3. Интегрирующий усилитель

Интегрирующий усилитель (интегратор) строится на базе инвертирующего усилителя путем замены резистора обратной связи конденсатором и его часто называют интегратором Миллера.

Схема интегратора приведена на рис. 11.12. Интегрирование используется при решении дифференциальных уравнений, обработке и генерировании электрических сигналов. Используя те же свойства идеального ОУ (KU→∞, Rвход→∞), что и для инвертирующего усилителя, получаем, что входной ток протекает через конденсатор в цепи обратной связи

IR + IC = 0 , где IR = |

Uвх |

; |

Ic = C |

dUвых |

= C |

dUC |

. |

(11.24) |

|

dt |

|

||||||

|

R |

|

|

dt |

|

|||

313

Напряжение на конденсаторе UC и выходное напряжение усилителя изменяются по закону

|

1 t |

1 |

t |

|

||

Uвых(t) = Uc (t) = |

|

∫iCdt = − |

|

∫Uвх(t)dt . |

(11.25) |

|

C |

RC |

|||||

|

0 |

0 |

|

|||

|

|

|

|

|||

Произведение RC называют постоянной времени интегратора и имеет размерность времени, что соизмеримо с размерностью сигнала действующего на входе интегратора. При подаче на вход интегратора скачка напряжения постоянной величины Uвх=const, напряжение на выходе Uвых=Uвxt/(RC) не зависит от коэффициента усиления ОУ. Конденсаторы, используемые в интеграторах, должны иметь малые токи утечки, чтобы обеспечивать достаточную точность интегрирования. На точность интегрирования оказывают влияние входной ток ОУ, который, протекая через конденсатор обратной связи С, заряжает его, а так же напряжение смещения, которое влияет на входное напряжение, изменяя его и также подзаряжая конденсатор. Для повышения точности интегрирования необходимо:

1.Использовать ОУ с низким напряжением смещения;

2.Выбирать ОУ с входными каскадами на полевых транзисторах;

3.Включать между неинвертирующим входом и землей резистор, шунтируя его иногда конденсатором.

Интеграторы широко применяются при создании генераторов линейно изменяющегося и синусоидального напряжений, точных фазосдвигающих устройств, обеспечивающих получение фазового сдвига напряжения величиной

90° с погрешностями минуты–десятки минут, а также в качестве фильтров низких частот.

11.9.4. Дифференцирующий усилитель

Дифференцирующий усилитель (дифференциатор) предназначен для получения входного сигнала пропорционального скорости изменения входного. При дифференцировании сигнала ОУ должен пропускать только переменную составляющую входного напряжения, а коэффициент усиления дифференцирующего звена должен возрастать при увеличении скорости изменения входного напряжения. Схема дифференциатора, на входе которого включен конденсатор С, а в цепи ОС – резистор, представлена на рис. 11.13. Полагая, что ОУ идеальный, ток через резистор обратной связи можно считать равным току через конденсатор IC+IR=0,

где

IC = C dUdtC = C dUdtвх ,

тогда

|

|

|

|

|

314 |

Uвых = IR Roc = −ICRoc и Uвых = −RocC |

dUвх |

. |

|

(11.26) |

|

|

|

||||

|

dt |

|

|

|

|

Рассмотренный |

дифференциатор |

||||

используется редко из-за следующих |

|||||

недостатков: |

|

|

|

|

|

1. Низкого |

входного |

||||

сопротивления на высоких частотах, |

|||||

определяемого емкостью С; |

|

||||

2. Относительно |

высокого |

уровня |

|||

шумов на |

|

выходе |

обусловленного |

||

большим |

усилением |

на |

высоких |

||

частотах; 3. Склонности к самовозбуждению.

С увеличением частоты уменьшается реактивное сопротивление конденсатора, что приводит к увеличению коэффициента усиления дифференциального звена для высокочастотных составляющих сигнала. А это в свою очередь усиливает собственные высокочастотные шумы элементов ОУ, которые находятся за полосой полезного сигнала. Кроме того, данная схема может быть неустойчивой в области частот, где частотная характеристика дифференциатора (кривая 1 на рис .11.14), имеющая подъем 20 дБ/дек, пересекается с АЧХ скорректированного ОУ, имеющего спад − 20 дБ/ дек (кривая 2 на рис. 11.14).

|

Амплитудно-частотная |

|||

характеристика |

разомкнутой |

|||

системы |

в |

некоторой части |

||

частотного |

диапазона |

имеет |

||

спад |

–40 дБ/дек, |

который |

||

определяется |

|

разностью |

||

наклона кривых 1 и 2, а фазовый сдвиг ϕ = –180°, что и указывает на возможность самовозбуждения. Чтобы избежать проявления этих недостатков дифференциатора

принимаются следующие схемотехнические решения:

1. Резистор обратной связи шунтируется конденсатором, ёмкость которого выбирается такой, чтобы участок АЧХ ОУ со спадом -20 дБ/дек начинался на частоте более высокой, чем максимальная частота полезного дифференциального сигнала. Это приводит к уменьшению высокочастотных составляющих шума в выходном сигнале. Такой участок начинается на частоте f=1/(2πRocCoc).

2. Последовательно со входным конденсатором С включается резистор, который ограничивает коэффициент усиления на высоких частотах дифферен-

315

циатора. Это обеспечивает динамическую устойчивость и снижает входной ёмкостной ток от источника сигнала.

3. Использование ОУ с низким напряжением смещения и малыми входными токами, а также конденсаторов с малыми токами утечек и малошумящих резисторов.

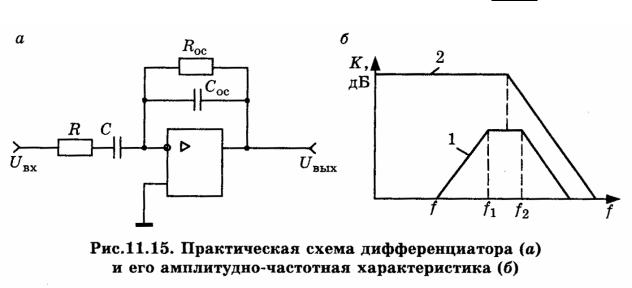

Практическая схема дифференциатора и его АЧХ приведены на рис. 11.15. Введение резистора R приводит к появлению на частотной характеристике (кривая 1 на рис. 11.15,б) горизонтального участка, где не происходит

дифференцирования на частотах, превышающих частоту f1 = 2π1RC .

Анализируя АЧХ (кривая 1 на рис. 11.15,б) видно, что в полосе частот от f до f1 схема устойчиво работает как дифференциатор, а на частотах выше f2 схема выполняет функции интегратора. В полосе частот f1…f2 схема выполняет роль полосового фильтра, и коэффициент усиления равен Roc/R. Если внешние элементы выбраны так, что RC=RocCoc, то f1=f2. Кривая 2 на рис. 11.15,б представляет АЧХ ОУ без цепей ОС.

На практике применяется большое число различных схем дифференциатора: суммирующий дифференциатор; разностный дифференциатор; диффе- ренциатор-усилитель.

11.9.5. Логарифмические схемы

Логарифмические и антилогарифмические усилители используются в быстродействующих устройствах возведения в степень, перемножения и деления сигналов, сжатия сигналов. Сжатие (уменьшение) динамического диапазона сигнала применяется для регистрации сигналов, уровень которых изменяется в широких пределах, а так же для повышения КПД усилителей, помехоустойчивости устройств связи. Для логарифмирования и антилогарифмирования сигналов используют ОУ, охваченные нелинейной обратной связью. В качестве элемента обратной связи используется полупроводниковый диод.

316

Логарифмический усилитель обеспечивает получение на выходе сигнала с переменной составляющей пропорциональной во времени логарифму переменной составляющей сигнала на его входе, и его схема представлена на рис. 11.16.

Uд = kT ln Iд . q I0

Ток, протекающий через диод в цепи обратной связи, описывается выражением

|

qUд |

|

||

|

|

|

|

|

kT |

. (11.27) |

|||

Iд ≈ I0 e |

|

|||

|

|

|

|

|

|

|

|

|

|

Падение напряжение на диоде равно и противоположно по фазе выходному напряжению и определяется из (11.27)

(11.28)

Учитывая, что для построения усилителя используется идеальный ОУ, то

I = Iд = Uвх R , |

(11.29) |

||||

Uвых = −UЉ = − |

kT |

ln |

Uвх |

. |

(11.30) |

|

|

||||

|

q RI0 |

|

|||

Используя уравнение (11.30), строится теоретическая передаточная характеристика, представленная на рис. 11.17 штриховой линией, а сплошной линией изображена передаточная характеристика, полученная экспериментально. Экспериментальная передаточная характеристика совпадает с теоретической только в диапазоне значений входного напряжения от Uвх1 до Uвх2 .

Участок передаточной характеристики, где теоретическая и экспериментальная характеристики совпадают, называют динамическим диапазоном

логарифмирования: Д=Uвх2/Uвх1. Выходное напряжение логарифмического

усилителя имеет только одну полярность, которая определяется включением диода. Логарифмический усилитель, схема которого изображена на рис. 11.16, имеет на выходе напряжение отрицательной полярности при подаче на вход положительного сигнала.

Для получения выходного напряжения как положительной, так и отрицательной полярности при подаче на вход знакопеременного входного сигнала логарифмический усилитель строят по схеме, представленной на рис. 11.18,а.

317

Передаточная характеристика такого усилителя, представленная на рис. 11.18,б, симметрична относительно начала координат. Наклон этой характеристики определяется отношением R2/R1. При малых входных сигналах сопротивления диодов велики, и заметное влияние на передаточную характеристику оказывает резистор R2. Кроме того, он уменьшает сдвиг нуля выходного напряжения ОУ, повышает стабильность усиления за счет увеличения глубины отрицательной обратной связи.

Недостатком логарифмических усилителей, схема которых представлена на рис. 11.18,а, является небольшое выходное напряжение, которое достигает максимума вблизи 0,6 В. Для получения больших значений выходного напряжения логарифмированный сигнал еще дополнительно усиливают.

Логарифмирование с большей точностью можно осуществить, если вместо диода в цепи ОС использовать транзистор, включенный по схеме с общей базой. Схема такого усилителя представлена на рис. 11.19.

Выходное напряжение определяется падением напряжения на открытом эмиттерном переходе транзистора. Коллекторная нагрузка транзистора равна R1||Rвх ОУ и является высокоомной. Выходное напряжение будет отрицательным при положительном входном напряжении. Для получения положительного выходного напряжения при отрицательном входном необходимо в цепи обратной связи использовать транзистор p–n–p типа. Для построения двухстороннего логарифмирующего устройства в цепи ОС

необходимо включать параллельно два транзистора различных типов проводимости.

318

11.9.6. Антилогарифмирующий усилитель

Это устройство, у которого выходное напряжение пропорционально во времени антилогарифму входного напряжения. Для нахождения по значению логарифмов исходных величин необходимо найти значение экспоненциальной функции от логарифма eln x = x. Антилогарифм определяется как экспонента логарифма. Для выполнения этой операции на входе ОУ включается транзистор, а в цепи ОС резистор, как показано на рис. 11.20.

Так как ток в цепи коллектора

|

|

|

|

|

|

|

qUэб |

|

|

связан с током эмиттера следующей зависимостью Iк = IЭ0e |

kT , а напряжение |

||||||||

на выходе Uвыx = RIoc = –RIK, товеличина выходного напряжения равна |

|||||||||

|

qUэб |

= −RIЭ0e− |

qUвх |

|

|

||||

|

|

|

= −RIЭ0anti lg |

qUвх |

. |

|

|||

Uвых = RIЭ0e kT |

kT |

(11.31) |

|||||||

|

|||||||||

|

|

|

|

|

kT |

|

|

||

Для получения положительного выходного напряжения при отрицательном входном, на входе схемы необходимо включать транзистор n–p–n типа. Входное сопротивление антилогарифмического усилителя мало и определяется сопротивлением открытого транзистора (эмиттерного перехода).

319

ГЛАВА 12 КОМПАРАТОРЫ НАПРЯЖЕНИЯ

Компараторы предназначены для сравнения двух входных сигналов и скачкообразного изменения выходного напряжения в случае, когда одно из сравниваемых напряжений больше другого. Один из входных сигналов называют опорным. Компараторы являются специализированными ОУ с дифференциальными входами и одиночным или парафазным цифровым выходом. На один вход компаратора подается исследуемый сигнал, на другой – опорный сигнал. Компараторы используются в самых различных областях: для сравнения уровня сигнала с пороговым значением, для получения прямоугольных сигналов из треугольных, в усилителях класса D, при импульсно-кодовой модуляции, для переключения источников питания, включения освещения и отопления и т.д. Основная идея при построении компаратора заключается в том, что транзистор выходного каскада должен включаться или выключаться в зависимости от уровня входных сигналов. Работа схемы основывается на том, что один из двух выходных транзисторов в любой момент находится в режиме отсечки. На выходе компаратора формируются сигналы высокого логического уровня, если разность входных сигналов меньше напряжения срабатывания компаратора или низкого логического уровня, если разность входных сигналов превышает напряжение срабатывания компаратора. В связи с этим приемником выходных сигналов компараторов являются схемы ТТЛ, ЭСЛ или КМОП логики. Любой ОУ может быть использован в качестве компаратора, однако промышленностью выпускается большое число специально спроектированных компараторов:

–общего применения (К521СА2, К521СА5, K554CA2),

–прецизионные (К521САЗ, К597САЗ),

–быстродействующие (К597СА1, К597СА2),

–специализированные (K521CAl, К521СА4, K1121СА1, K1401СA1).

Точность измерения компаратора характеризуется напряжением, на ко-

торое необходимо превысить уровень опорного напряжения, чтобы выходное напряжение достигло порога срабатывания логической схемы. Точностные параметры компараторов определяются параметрами ОУ. Компараторы должны обладать низким напряжением сдвига, низким значением тока смещения, устойчиво работать без самовозбуждения. Входным каскадом компаратора является дифференциальный каскад, обеспечивающий очень слабую чувствительность к синфазным входным сигналам. А так как компараторы нагружаются логическими схемами (КМОП и ТТЛ логики), обладающими временем переключения десятки наносекунд, то необходимо, чтобы и компараторы обладали таким же 6ыстродействием.

Основными параметрами компараторов являются: чувствительность (точность, с которой компаратор может различить входной и опорный сигнал), быстродействие tздр (определяемое временем от начала сравнения до момента,

320

когда выходное напряжение достигает порога срабатывания логической схемы), нагрузочная способность (способность компаратора управлять определенным числом входов цифровых устройств).

Для повышения быстродействия компараторов необходимо, чтобы транзисторы схемы работали в активном режиме или быстро выходили из состояния насыщения. Это обеспечивается применением транзисторов с барьером Шотки. В быстродействующих интегральных компараторах почти все используемые транзисторы являются транзисторами с барьером Шотки.

Скоростные компараторы обычно делают с двумя противофазными цифровыми выходами, что позволяет в последующих цифровых устройствах исключить несколько ключей и тем самым повысить быстродействие всей схемы. Часто для повышения быстродействия компараторов полупроводник легируют золотом, что уменьшает время жизни неосновных носителей и способствует быстрому выходу транзистора из режима насыщения. Рассмотрим работу компаратора с использованием обычного ОУ в диапазоне низких частот, представленного на рис. 12.1,a.

На инвертирующий вход подается постоянное положительное опорное напряжение величиной Uoп, а на неинвертирующий вход – синусоидальное напряжение. На выходе компаратора за счет большого коэффициента усиления ОУ получается последовательность почти прямоугольных импульсов (рис. 12.1,б). Переключение схемы происходит тогда, когда Uвх = Uoп, однако реальный ОУ имеет небольшой входной ток и ненулевое напряжение смещения нуля, что вносит ошибки в работу компараторов, сдвигая моменты переключения в одну или другую сторону. При наличии большого дифференциального входного напряжения для защиты микросхемы на входе включаются встречно-параллельно два диода (pис. 12.1,а), которые с резисторами R1 и R2 образуют ограничители. Роль резисторов могут выполнять внутренние сопротивления источников напряжений Uoп и Uвх.

Если напряжение опорного сигнала равно нулю, то компаратор называют нуль-индикатором или детектором нулевого уровня. При необходимости сравнения двух разнополярных напряжений входной и опорный сигналы подаются