4 семестр (2 курс)лала / ЭП (Электронные приборы) / Техническая электроника 2000 (Ткаченко Ф.А

.).pdf

201

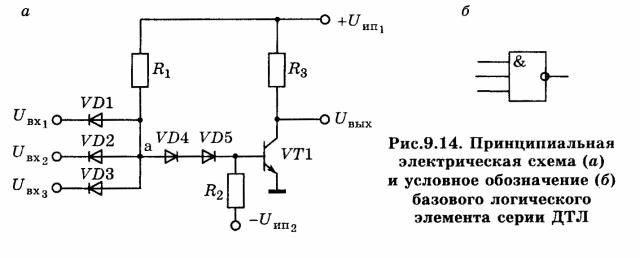

назначены для увеличения порога запирания и помехоустойчивости схемы в закрытом состоянии, а резистор R2 и Uип2 обеспечивают оптимальную вели-

чину тока этих диодов. Диоды VD1…VD3 должны обладать минимальным сопротивлением в проводящем состоянии; высоким (максимальным) обратным напряжением; малой емкостью и малым временем восстановления обратного сопротивления.

Рассмотрим принцип работы ДТЛ. Пусть на один (или на все входы) подается низкий входной сигнал логического нуля U0вх . Входной диод (или все

диоды) открывается и оказывается замкнутым на общую шину. От источника питания Uип1 через резистор R1, открытый диод и входную цепь протекает ток,

при этом потенциал точки a уменьшается до уровня прямого падения напряжения на диоде Ua = U0вх + Uпр, где Uпр – падение напряжения на открытом

входном диоде. При отсутствии VD4, VD5 потенциал базы транзистора VТ1 был бы положительным, а транзистор – открыт. За счет падения напряжения Uд см на диодах VD4, VD5 потенциал базы транзистора отрицателен – Uб=Uа– 2Uдсм, транзистор закрыт и на выходе схемы формируется высокий уровень напряжения логической единицы. Диоды смещения должны обладать большим сопротивлением, чтобы при относительно малом токе получить большое падение напряжения.

При одновременной подаче на все входы высокого уровня напряжения логической единицы диоды VD1…VD3 запираются. Транзистор VT1 переходит в область насыщения за счет тока, протекающего от источника питания Uип1 через R1, смещающие диоды VD4, VD5, в базу транзистора. На выходе

схемы появляется низкий уровень напряжения, близкий к нулю U0вых.

С целью уменьшения входного тока инвертора при действии на входе схемы напряжения логического нуля входную цепь усложняют, включая транзистор VТ1 (рис. 9.15), который работает как эмиттерный повторитель и увели-

202

чивает усиление по току. А для улучшения выходных характеристик логического элемента выходной каскад строится по более сложной схеме.

За счет падения напряжения на эмиттерном переходе транзистора VТ1, работающего в активном (ненасыщенном) режиме, повышается общая помехоустойчивость и уменьшается время переходных процессов при включении и выключении схемы. Сложный инвертор позволяет повысить нагрузочную способность. Схема обладает малым выходным сопротивлением в обоих состояниях, благодаря чему

заряд и разряд паразитных емкостей в нагрузках следующего каскада протекает быстрее, работа этого инвертора будет рассмотрена при рассмотрении базового элемента ТТЛ.

9.10. Транзисторно–транзисторная логика (ТТЛ)

Элементы транзисторно-транзисторной логики являются дальнейшим усовершенствованием ДТЛ, которая осуществляется заменой диодной сборки многоэмиттерным транзистором. Многоэмиттерный транзистор представляет собой совокупность нескольких транзисторных структур, имеющих общий коллектор и общую базу и непосредственно взаимодействующих друг с другом только за счет движения основных носителей. Эмиттерные переходы МЭТ выполняют функции входных диодов в схемах ДТЛ, а коллекторный переход – роль смещающего диода. Характерной особенностью элементов транзисторнотранзисторной логики является высокая помехоустойчивость, большое быстродействие, хорошая нагрузочная способность, малая потребляемая мощность, высокая надежность, малая стоимость.

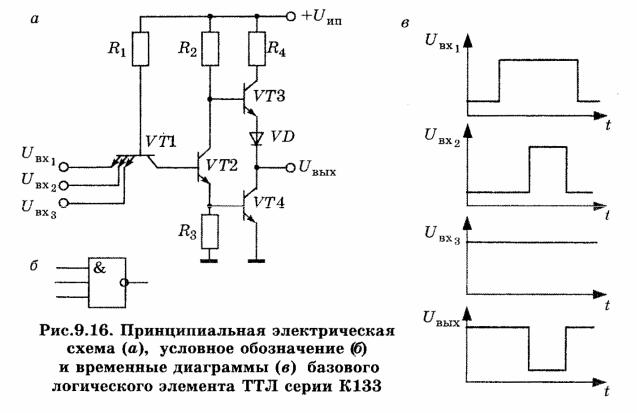

Принципиальная электрическая схема, условное обозначение, временные диаграммы базового логического элемента серий ТТЛ приведены на рис. 9.16. Базовый логический элемент ТТЛ выполняет операцию И–НЕ (является элементом Шеффера). Схема базового элемента ТТЛ состоит из двух частей. Входная часть реализует логическую функцию И с помощью VТ1 и резистора R1. Выходная цепь реализует функцию НЕ и содержит сложный инвертор на транзисторах VТ2…VТ4. Сложный инвертор включает в свой состав простой инвертор (VТ2, R2) и эмиттерный повторитель (VТ3) с динамической нагрузкой (VТ4), которая управляется эмиттерным током транзистора VТ2. Простой ин-

203

вертор в этой схеме (VТ2) является фазоинверсным каскадом. Если транзистор VТ2 открыт, то через него протекает большой эмиттерный ток, который является базовым током транзистора VТ4. Транзистор VТ4 открывается и переходит в режим насыщения. А транзистор VТ3 закрывается низким коллекторным потенциалом транзистора VТ2. Выходное напряжение близко к нулю. Если транзистор VТ2 закрыт, то транзистор VТ3 открыт, ибо потенциал базы транзистора VТ3 близок к Uип, а транзистор VТ4 закрыт. Выходное напряжение имеет высокий уровень и соответствует логической единице. При запирании транзистора VТ4 ток рассасывания избыточных носителей из базы транзистора VТ4 протекает через резистор R3 на землю. Резистор R4 ограничивает ток выходного каскада во время перехода схемы из открытого состояния в закрытое, когда транзистор VТ3 уже открылся, а транзистор VT4 еще находится в режиме насыщения. Диод VD обеспечивает надежное запирание транзистора VТ3, при напряжении на выходе схеме равном нулю. Сопротивление резистора R4 выбирается исходя из заданного значения предельно допустимого тока транзисторов VТ3, VТ4 и диода VD и составляет величину порядка 50…500 Ом. Для сопротивлений других резисторов существуют оптимальные значения: R1/R2=2…4; R2/R3=1…2; R2/R4=10.

Рассмотрим принцип работы схемы. Если хотя бы на один из входов подано напряжение логического нуля, то соответствующий эмиттерный переход многоэмиттерного транзистора VТ1 открывается. Ток базы Iб1 ≈ Uип / R1 тран-

зистора VT1 потечет во входную цепь, при этом ток коллектора VТ1 уменьшается, коллекторный переход открывается и транзистор VТ1 насыщается по

204

коллекторной цепи. Напряжение на базе транзистора VТ2 равно сумме входного напряжения и остаточного напряжения на насыщенном транзисторе VТ1:

Uб2 = U0вх + Uост1 . Поэтому транзистор VТ2 запирается, а транзистор VТ3 и

диод VD открываются высоким потенциалом коллектора транзистора VТ2. Транзистор VТ4 – закрыт. Напряжение на выходе имеет высокий уровень и соответствует логической единице "1".

Если на всех логических входах действуют высокие уровни напряжения, то эмиттерные переходы транзистора VТ1 закрываются, VТ1 работает в инверсном активном режиме. Ток от Uип через R1, открытый коллекторный переход транзистора VТ1 поступает в базу транзистора VТ2. Транзисторы VТ2, VТ4 открываются, и на выходе схемы имеется уровень напряжения, соответствующий логическому нулю. Транзистор VТ3 и диод VD закрыты.

Базовые элементы различных серий ТТЛ различаются только инверторами, которые должны улучшать переходные характеристики, повышать помехоустойчивость и нагрузочную способность, потреблять небольшую мощность. Для уменьшения входных токов транзистор VТ1 должен обладать малым коэффициентом передачи тока базы в инверсном режиме h21эi ≈ 0,005K0,05 .

Логические элементы со сложным инвертором потребляют большую мощность, занимают большую площадь кристалла, поэтому на их основе изготавливаются цифровые микросхемы малой и средней степени интеграции.

Быстродействие логических элементов различных серий ТТЛ можно повысить двумя путями:

–уменьшая сопротивление резисторов и паразитные емкости;

–обеспечивая работу транзисторов в активном, т.е. ненасыщенном режиме, при котором отсутствует накопление и рассасывание носителей в базах транзисторов. Оба эти способа повышения быстродействия нашли практическое применение.

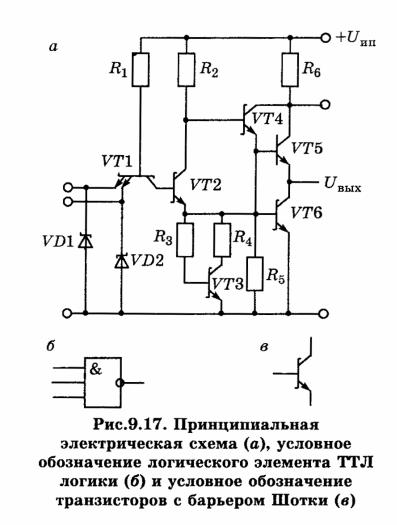

Первый способ использовался при создании ТТЛ серий К130 и К131. Второй способ повышения быстродействия цифровых микросхем ТТЛ связан с применением транзисторов с барьером Шотки. При этом высокое быстродействие сочетается с умеренным потреблением мощности. Диоды Шотки подключаются параллельно коллекторному переходу транзистора, а транзисторы с диодами Шотки называют транзисторами с барьером Шотки или транзисторами Шотки (рис. 9.17,а,б). Когда транзистор закрыт или работает в ненасыщенном, активном режиме, потенциал коллектора выше потенциала базы. Диод Шотки закрыт и не влияет на работу транзистора. При насыщении транзистора потенциал коллектора уменьшается, диод Шотки открывается при напряжении 0,3…0,5 В и фиксирует этот уровень напряжения на коллекторном переходе, не позволяя транзистору перейти в режим насыщения. Применение транзисторов Шотки позволяет уменьшить или почти полностью исключить время рассасывания избыточного заряда в базе и тем самым снизить время выключения схемы. На рис. 9.17,в показана принципиальная схема базового элемента ТТЛШ

205

серии. Промышленностью выпускается следующие серии ТТЛШ логики: К530, К531, КР1531 и маломощные К555, КР1533 с потребляемой мощностью порядка 2 мВт. По принципу действия эта схема аналогична базовому ТТЛ логическому элементу (рис. 9.16). Отличие состоит лишь в том, что в выходном каскаде использован составной транзистор VТ4, VТ5, обеспечивающий повышенный выходной ток, а каскад с ОЭ (генератор тока) на транзисторе

VТ3 с резисторами R3, R4, включенный в эмиттерную цепь

транзистора VТ2, улучшает форму передаточной характеристики, приближая ее к прямоугольной. Транзистор VТ5 реализуется без диода Шотки, т.к. он работает в

активном режиме (эмиттерный повторитель).

В перспективных интегральных микросхемах применяются новые интегральные транзисторы со структурой "Изопланар-П", у которых использована оксидная изоляция между транзисторами, а не привычный p–n переход. Граничная частота у транзисторов с такой структурой достигает 5 ГГц, что в 3 раза выше, чем у транзисторов с планарной структурой.

Выигрыш в быстродействии схем с использованием транзисторов Шотки приводит к некоторому ухудшению статических параметров: понижается

пороговое напряжение, повышается значение логического нуля U0вых , ухуд-

шается помехоустойчивость. Для повышения помехоустойчивости логических элементов в эмиттерные цепи многоэмиттерного транзистора VТ1 вводят диоды VD1–VD2, включенные в обратном направлении для сигналов логической единицы и нуля. Если напряжения на входах логического элемента меняют свой знак на противоположный, то диоды VD1, VD2 открываются. Сигнал помехи не поступает на вход транзистора VТ1, и не происходит ложное срабатывание схемы.

206

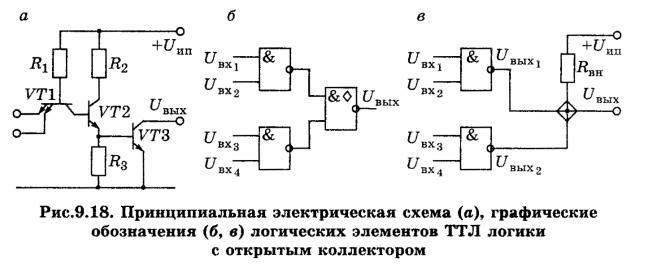

9.11. Микросхемы ТТЛ серий с открытым коллектором

Для расширения функциональных возможностей у отдельных микросхем выходы выполнены так, что верхний выходной транзистор и относящиеся к нему элементы отсутствуют. Такие логические элементы называют элементами со свободным (открытым) коллектором (рис. 9.18).

Верхний транзистор обычной транзисторной выходной пары отсутствует, а вывод имеет коллектор нижнего транзистора VТ3. Если хотя бы один из входных сигналов равен 0, транзистор VТ3 закрыт, на выходе схемы формируется напряжение низкого уровня. Такой выходной каскад не способен сам по себе сформировать на выходе высокий уровень напряжения. На практике коллектор транзистора VТ3 такой микросхемы подключается внешним монтажом к дополнительному источнику напряжения через нагрузочное сопротивление. Нагрузочным сопротивлением может быть резистор, реле, элементы индикации (светодиод, лампа накаливания), коаксиальный кабель, вход усилителя мощности и др. Напряжение, к которому подключается внешняя нагрузка, может значительно превышать напряжение питания микросхемы.

Микросхемы с открытым коллектором позволяют:

–быть переходным звеном от логической части устройства к элементам выводаинформации, т.е. используются дляуправления внешними устройствами;

–обеспечить реализацию дополнительной логической функции при непосредственном соединении между собой выходов нескольких микросхем.

Объединение выходов нескольких функциональных узлов называют монтажной (проводной) логикой. При таком соединении, если на выходе одного или нескольких элементов будет низкий потенциал (логический 0 в положительной логике), то низкий потенциал будет на выходе всей схемы. При наличии логической единицы на всех выходах на общей объединенном выходе будет значение логической единицы. Параллельное подключение нескольких открытых коллекторов к общей нагрузке создает систему, выполняющую логическую операцию И (монтажное И)

207

Uвых = Uвых1 Uвых2 . |

(9.25) |

Каждый из логических элементов в свою очередь выполняет логическую операцию И–НЕ

Uвых1 = |

|

|

; Uвых2 = |

|

|

. |

(9.26) |

||

Uвх1 Uвх2 |

Uвх3 Uвх4 |

||||||||

Следовательно, выходная логическая функция системы |

|

||||||||

Uвых = |

|

|

|

. |

(9.27) |

||||

Uвх1 Uвх2 |

Uвх3 Uвх4 |

||||||||

При работе схем с монтажной логикой необходимо учитывать, что каждый компонент схемы утрачивает самостоятельность и действует как элемент общей системы. Графическое представление рассмотренной функции представлено на рис. 9.18,б, в. Включение логических выходов на общую нагрузку (монтажная логика) условно изображается в виде логического элемента, выполняющего соответствующую логическую функцию (рис. 9.18,б). А то, что это не реальная микросхема, а способ соединения выводов, к символу выполняемой операции добавляется условный знак – ◊ (ромб) в поле микросхемы или в точке соединения выводов (рис. 9.18,в). Примерами элементов с открытым коллектором являются микросхемы К155ЛА7; К155ЛА11.

Подавая разные значения напряжения питания в схемах с открытым коллектором, можно получать разные уровни выходного сигнала. Это позволяет осуществлять согласование микросхем серии ТТЛ с другими сериями, имеющими другие значения логических нулей и единиц, не используя дополнительных преобразователей уровней.

Максимальное число объединяемых элементов и максимальное значение Rн макс ограничиваются соотношением значения этого сопротивления и токов утечки выходных транзисторов. Когда все транзисторы закрыты, падение напряжения на Rн от суммарного тока утечки не должно снижать высокий уровень на выходе ниже допустимого (рис. 9.19,а). Rн мин ограничено максимально допустимым током открытого выходного транзистора (рис. 9.19,б).

Сопротивление Rн макс находят из условия обеспечения большого выходного напряжения U1вых (рис. 9.19,а)

Rн макс = |

Uип − U1вых |

, |

(9.28) |

|

Kоб выхIут вых − Kоб вхI1вх |

||||

|

|

|

где Kоб вых – число объединенных выходов;

Iут вых – ток утечки на выходе;

Rоб вх – число подключенных входов.

Минимальное сопротивление Rн мин находят из условия получения мини-

мального выходного напряжения – логического нуля Uвых0 |

(рис. 9.19,б) |

|||

|

|

Uип − Uвых0 |

|

|

R’ “ЏЏ= |

|

|

, |

(9.29) |

0 |

0 |

|||

|

Iвых макс −Kоб вхIвх |

|

||

208

где I0вых макс– максимальный допустимый выходной ток одного элемента при обеспечении логического нуля на его выходе.

Конкретное значение Rн выбирают из условия требуемого быстродействия при наименьшей потребляемой мощности. Максимальное быстродействие достигается тогда, когда Rн близко к минимальному значению. С повышением Rн увеличивается время заряда паразитных емкостей при высоком уровне выходного напряжения, и уменьшается потребление тока при низком уровне.

9.12. Правила схемного включения элементов

Выпускаемые промышленностью микросхемы ТТЛ серий выполняют простейшие логические операции (И–НЕ; ИЛИ–НЕ и др.), содержат в одном корпусе несколько независимых логических элементов, связанных между собой только источником питания.

Если некоторые логические элементы, входящие в состав корпуса, не используются, то рекомендуется такие элементы включать так, чтобы на их вы-

ходах был высокий потенциал U1вых. Для этого входы неиспользуемых элемен-

тов ТТЛ серий, выполняющих операции И–НЕ и ИЛИ–НЕ соединяют с общей (земляной) шиной. В таком состоянии элемент потребляет (рассеивает) минимальную мощность, и его выход можно использовать как источник логической единицы на входах других схем.

209

Неиспользованные входы логического элемента ТТЛ серий можно оставлять свободными, но при этом снижается помехоустойчивость из-за воздействия наводок на свободные выводы. В сериях ТТЛ и ТТЛШ неиспользованные входы объединяют с другими используемыми входами, если это не ведет к превышению нагрузочной способности предыдущего каскада, либо подключают к источнику логической единицы.

В качестве источника логической единицы используют неиспользованные элементы, входы которых заземлены, или источник питания микросхемы, который подключают ко входу через резистор с сопротивлением 1 кОм, ограничивающий входной ток. К одному такому резистору обычно подключается до 20 неиспользованных входов.

Для уменьшения помех по цепи питания в точках подключения к шинам групп логических элементов включаются развязывающие керамические конденсаторы емкостью порядка 0,1 мкФ на один корпус. При большом числе одновременно переключаемых логических элементов броски тока в цепи питания достигают единиц–десятков А. Поэтому между цепью питания и общей шиной устанавливаются электролитические конденсаторы большой емкости, которые компенсируют кратковременные импульсы тока и обеспечивают уменьшение взаимосвязи логических элементов через цепь питания.

Небольшие значения выходных сопротивлений элементов ТТЛ серий приводят к тому, что во время переключения схемы ток в цепи питания возрастает и может в несколько раз превышать ток, потребляемый схемой в статическом режиме. Поэтому при увеличении частоты переключения, мощность потребляемая ТТЛ схемой со сложным инвертором растет, все это приводит к недопустимости соединения выходов нескольких схем. Если такое соединение осуществить, то в состоянии, когда один из элементов имеет на выходе низкий

уровень напряжения U0вых, а другой – высокий U1вых, через последовательно

включенные транзистор VТ3 одной схемы и транзистор VТ4 другой схемы (рис. 9.16) будет протекать большой ток.

Величина этого тока определяется выражением (9.30) и может в несколь-

ко раз превышать ток в статическом режиме |

|

|||

(Iэ |

4 |

) |

≈ (Uип − Uпр) R4 , |

(9.30) |

|

макс |

|

|

|

где Uпр – падение напряжения на открытом транзисторе.

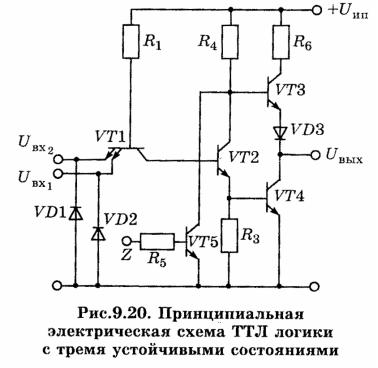

При этом резко возрастает потребляемая мощность, и возможен выход схем из строя, так как транзисторы обычно не рассчитаны на длительное протекание больших токов. В связи с этим при проектировании цифровых схем не допускается объединение выходов таких элементов. Если несколько узлов или блоков работают на общую нагрузку, то объединение выходов является необходимым. Для этих целей используется схема ТТЛ с тремя устойчивыми состояниями, представленная на рис. 9.20.

В приведенной схеме отличие от базового элемента состоит в том, что имеется третье состояние, при котором выходные транзисторы закрыты, и схе-

210

ма полностью отключается от нагрузки сигналом управляющего вывода Z, дающим разрешение по выходу. Третье состояние элемента не зависит от комбинации логических сигналов на входе элемента. Такие схемы объединяют по выходам, и они работают на общую нагрузку. Управление микросхем предусматривает обслуживание нагрузки в любой момент времени одним элементом, а другие элементы должны находиться в третьем состоянии. Выходное сопро-

тивление закрытых транзисторов велико и элемент практически отключен от нагрузки. Такое состояние элементов называют высокоимпедансным. Это состояние достигается тем, что в схему включен транзистор VТ5 и резистор R5. При подаче на управляющий вход Z напряжения логического нуля, транзистор VT5 закрывается, элемент работает как обычный базовый элемент. Если на управляющий вход Z подается напряжение логической единицы, транзистор VТ5 переходит в режим насыщения, а транзисторы VТ3, VТ4 закрываются. Такие микросхемы используются в информационной технике для обслуживания проводника шины данных, и примером являются микросхемы К531ЛА17П,

К531ЛА19П.

9.13. Эмиттерно–связанная логика

Цифровые микросхемы эмиттерно–связанной логики составляют схемы на переключателях тока с объединенными эмиттерами, обладающие по сравнению с другими типами цифровых схем наибольшим быстродействием и большой потребляемой мощностью.

Большое быстродействие ЭСЛ логики обеспечивается:

–за счет работы транзисторов в ненасыщенном (линейном) режиме;

–за счет применения на выходах схемы эмиттерных повторителей, ускоряющих процесс заряда и разряда нагрузочных емкостей;

–за счет ограничения перепада выходного напряжения, что приводит к снижению статической помехоустойчивости.

Наибольшее распространение получили ЭСЛ серии 100, 500, К500, 700, К1500, обеспечивающие выполнение любых арифметических и логических операций.