OEVMiS_ekz_shpory

.pdf

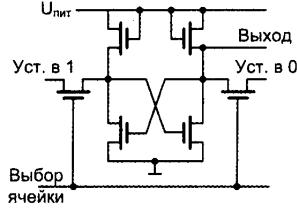

Важным моментом, характеризующим SRAM, является технология записи. Известны два варианта записи: стандартная и запаздывающая. В стандартном режиме адрес и данные выставляются на соответствующие шины в одном и том же такте. В режиме запаздывающей записи данные для нее передаются в следующем такте после выбора адреса нужной ячейки, что напоминает режим конвейерного чтения, когда данные появляются на шине в следующем такте.

Динамические оперативные запоминающие устройства.

Запоминающий элемент динамического ОЗУ способен хранить информацию только в течение достаточно короткого промежутка времени, после которого информацию нужно восстанавливать заново, иначе она будет потеряна. Такой ЗЭ состоит из одного конденсатора и запирающего транзистора (рис).

Наличие или отсутствие заряда в конденсаторе интерпретируется как 1 или 0 соответственно. Простота схемы позволяет достичь высокой плотности размещения ЗЭ и в итоге снизить стоимость. С другой стороны, считать значение, хранящееся в ячейке DRAM, невозможно, не изменив эту информацию, поэтому после опе-

рации считывания заряд нужно восстановить. Такое восстановление производится путем занесения считанной информации в специальный буфер, с последующей перезаписью из буфера на то же место, благодаря чему происходит перезаряд конденсаторов. Кроме того, накапливаемый на конденсаторе заряд из-за паразитных утечек со временем теряется. Периодическое восстановление заряда путем перезаписи информации называется регенерацией и осуществляется каждые 2-8 мс.

В различных типах микросхем динамической памяти нашли применение три основных метода регенерации: одним сигналом RAS (на шину адреса выдается адрес регенерируемой строки, сопровождаемый сигналом RAS); сигналом CAS, предваряющим сигнал RAS (при появлении первым сигнала СAS начинается специальный цикл регенерации); автоматическая регенерация (связана с энергосбережением, когда система переходит в режим «сна» и тактовый генератор перестает работать).

Асинхронные динамические ОЗУ. Работа таких микросхем не привязана жестко к тактовым импульсам.

Синхронные динамические ОЗУ. В синхронных DRAM обмен информацией синхронизируется внешними тактовыми сигналами и происходит в строго определенные моменты времени, что позволяет взять все от пропускной способности шины процессорпамять и избежать циклов ожидания.

Специальные типы оперативной памяти Специализированные ОЗУ – кот. используют специализированные архитектуры, в

которых стандартные функции (запись, хранение, считывание) сочетаются с некоторыми дополнительными возможностями или учитывают особенности применения памяти: память с множественным доступом (многопортовые ОЗУ); память типа очереди (ОЗУ типа FIFO). Оба типа относятся к статическим ОЗУ.

В отличие от стандартного в n-портовом ОЗУ имеется п независимых наборов шин адреса, данных и управления, гарантирующих одновременный и независимый доступ к ОЗУ n устройствам. Данное свойство позволяет существенно упростить создание многопроцессорных и многомашинных вычислительных систем, где многопортовое ОЗУ выступает в роли общей или совместно используемой памяти.

Более эффективным видом ОЗУ, где запись и считывание информации могут вестись одновременно, служит память типа FIFO. Микросхема представляет собой двухпортовое ОЗУ, где один порт предназначен для занесения информации, а второй – для считывания. От обычного двухпортового ОЗУ FIFO-память отличается:

- у микросхемы нет входов для указания адреса ячейки, занесение и считывание данных производится в порядке их поступления через одну входную точку и одну выходную;

- необходимостью слежения за состоянием очереди. Для этого в микросхеме имеются регистры-указатели адресов начала и конца очереди, а также специальные флаги, которые указывают на две ситуации: отсутствие данных (в этом случае блокируется считывание из микросхемы) и полное заполнение памяти (блокируется запись).

26. Внешняя память. Характеристики ЗУ внешней памяти.

Наиболее распространенные виды внешних ЗУ – это твердотельные, магнитные и оптические диски, а также магнитоленточные устройства.

Многие из характеристик ЗУ внутренней памяти применимы и к ЗУ внешней памяти, часть характеристик модифицируются для учета их специфики.

Внешние ЗУ обычно выполняются в виде отдельных конструктивов или встраиваемых блоков. В последнем случае они монтируются в специально отведенных для них местах корпуса ВМ. К ядру ВМ внешние ЗУ подключаются аналогично устройствам ввода/вывода.

Емкость ЗУ внешней памяти достаточно велика, поэтому ее характеризуют такими крупными единицами, как мегабайт, гигабайт, терабайт и петабайт.

Важной характеристикой ЗУ является единица пересылки. Применительно к внешней памяти, данные передаются единицами, превышающими размер слова – блоками.

В ЗУ внешней памяти используется два основных метода доступа:

-последовательный доступ (позволяет обращаться к ячейкам ЗУ в определенной последовательности). ЗУ с последовательным доступом ориентировано на хранение информации в виде последовательности блоков данных, называемых записями. Для доступа к нужному элементу (слову или байту) необходимо прочитать все предшествующие ему данные. Время доступа зависит от положения требуемой записи в последовательности записей на носителе информации и позиции элемента внутри данной записи. Примером может служить ЗУ на магнитной ленте;

-прямой доступ. Каждая запись имеет уникальный адрес, отражающий ее физическое размещение на носителе информации. Обращение осуществляется по адресу к началу записи, с последующим последовательным доступом к определенной единице информации внутри записи. В результате время доступа к определенной позиции является величиной переменной. Такой режим характерен для магнитных дисков.

Быстродействие ЗУ внешней памяти обычно оценивают с помощью двух дополнительных параметров:

-время доступа ТЦ. В ЗУ с подвижным носителем информации – это время, затрачиваемое на установку головки записи/считывания (или носителя) в нужную позицию;

-среднее время считывания или записи N битов TN. Для ЗУ внешней па-

мяти определяется соотношением TN = TA + N/R, где TA – среднее время доступа; R – скорость пересылки в бит/с.

С точки зрения физического типа запоминающего устройства, наибольшее распространение получили три технологии внешних ЗУ: полупроводниковая память, лежащая в основе твердотельных дисков, память с магнитным носителем информации, используемая в магнитных дисках и лентах, и память с оптическим носителем – оптические диски.

Стоимость ЗУ, как и в случае внутренней памяти, принято оценивать отношением общей стоимости ЗУ к его емкости в битах, т.е. стоимостью хранения одного бита информации.

27. Управление вводом/выводом. Системы ввода/вывода. Модули ввода/вывода. Каналы и процессоры ввода/вывода.

Системы ввода/вывода - обеспечивают обмен информацией между ядром ВМ и разнообразными внешними устройствами (ВУ).

Технически система ввода/вывода реализуется комплексом модулей ввода/вывода (МВВ). Две основные функции МВВ: обеспечение интерфейса с ЦП и памятью ("большой" интерфейс); обеспечение интерфейса с одним или несколькими периферийными устройствами ("малый" интерфейс).

Можно выделить три основных способа подключения СВВ к ядру процессора.

Вварианте с раздельными шинами памяти и ввода/вывода обмен информацией между ЦП и памятью физически отделен от ввода/вывода, поскольку обеспечивается полностью независимыми шинами.

Во втором варианте с совместно используемыми линиями данных и адреса па-

мять и СВВ имеют общие для них линии адреса и линии данных, разделяя их во времени. В то же время управление памятью и СВВ, а также синхронизация их взаимодействия с процессором осуществляются независимо по раздельным линиям управления.

Последний тип архитектуры ВМ предполагает подключение СВВ к системной шине на общих правах с процессором и памятью.

Адресное пространство ввода/вывода может быть совмещено с адресным про-

странством памяти или быть выделенным.

При совмещении адресного пространства для адресации модулей вво-

да/вывода отводится определенная область адресов в адресном пространстве памяти.

Вслучае выделенного адресного пространства для обращения к модулям вво-

да/вывода применяются специальные команды и отдельная система адресов. Достоинства выделенного адресного пространства: адрес внешнего устройства в команде ввода/вывода может быть коротким, благодаря чему сокращается длина таких команд

иупрощаются схемы дешифрации адреса; программы становятся более наглядными, так как операции ввода/вывода выполняются с помощью специальных команд; разработка СВВ может проводиться отдельно от разработки памяти.

Недостатки выделенного адресного пространства: ввод/вывод производится только через специально выделенный регистр (обычно аккумулятор) центрального процессора; малая разрядность адреса периферийного устройства ограничивает число подключаемых устройств.

Модули ввода/вывода - отвечают за управление одним или несколькими ВУ и за обмен данными между этими устройствами с одной стороны, и основной памятью или регистрами ЦП – с другой. Основные функции МВВ: локализация данных; управление и синхронизация; обмен информацией; буферизация данных; обнаружение ошибок.

Под локализацией данных понимается возможность обращения к одному из ВУ, а также адресации данных на нем.

Каждому модулю назначается определенный диапазон адресов, независимо от того, является ли пространство адресов совмещенным или раздельным. Старшие разряды в адресах диапазона, выделенного модулю, обычно одинаковы и обеспечивают выбор одного из МВВ в рамках системы ввода/вывода. Младшие разряды адреса представляют собой уникальные адреса регистров данного модуля или подключенных к нему ВУ. Одной из функций МВВ является проверка вхождения поступившего по шине адреса в выделенный данному модулю диапазон адресов. При положитель-

ном ответе модуль должен обеспечить декодирование поступившего адреса и перенаправление информации к адресуемому объекту или от него.

Функция управления и синхронизации заключается в том, что МВВ должен координировать перемещение данных между внутренними ресурсами ВМ и внешними устройствами.

Основной функцией МВВ является обеспечение обмена информацией. Со стороны «большого» интерфейса – это обмен с ЦП, а со стороны «малого» интерфейса – обмен с ВУ.

Функция обмена информацией с ЦП включает в себя: распознавание команды; пересылку данных между МВВ и ЦП по шине данных; извещение о состоянии; распознавание адреса.

Наряду с обеспечением обмена с процессором МВВ должен выполнять функцию обмена информацией с ВУ. Такой обмен также включает в себя передачу данных, команд и информации о состоянии.

Важной задачей модуля ввода/вывода является буферизация данных.

Еще одной из важнейших функций МВБ является обнаружение ошибок, возникающих в процессе ввода/вывода. Центральный процессор следует оповещать о каждом случае обнаружения ошибки.

Методы управления вводом/выводом В ВМ находят применение два способа организации ввода/вывода:

- программно управляемый ввод/вывод (прямой ввод/вывод, условный ввод/вывод, ввод/вывод по прерываниям);

-прямой доступ к памяти.

Каналы и процессоры ввода/вывода Помимо рассмотренных методов управления вводом/выводом для максималь-

ное высвобождение ЦП от управления процессами ввода/вывода используются следующие меры:

1)расширение возможностей МВВ и предоставление ему прав процессора со специализированным набором команд, ориентированных на операции ввода/вывода. ЦП дает указание такому процессору ввода/вывода выполнить хранящуюся в памяти ВМ программу ввода/вывода. Процессор ввода/вывода извлекает и исполняет команды этой программы без участия центрального процессора и прерывает ЦП только после завершения всей программы ввода/вывода;

2)рассмотренному в пункте 1 процессору ввода/вывода придается собственная локальная память, при этом возможно управление множеством устройств ввода/вывода с минимальным привлечением ЦП.

В первом случае МВВ называют каналом ввода/вывода (КВВ), а во втором –

процессором ввода/вывода.

28. Понятие конвейерной обработки. Организация конвейера

Совершенствование элементной базы уже не приводит к кардинальному росту производительности ВМ. Более перспективными в этом плане представляются архитектурные приемы, среди которых один из наиболее значимых — конвейеризация. Для пояснения идеи конвейера начертим блок схему, где показан отдельный функциональный блок (ФБ) . Исходные данные помещаются во входной регистр Рг вх, обрабатываются в функциональном блоке, а результат обработки фиксируется в выходном регистре Рг вых. Если максимальное время обработки в ФБ равно Тmax, то новые данные могут быть занесены во входной регистр Рг не ранее, чем спустя Tmax.

Рг вх |

|

ФБ |

Рг вых |

|

|

||

Рг |

ФБ1 |

Рг1 |

ФБ2 |

Рг2 |

ФБ3 |

Рг |

|

вх |

вых |

||||||

|

|

|

|

|

|||

Рг вх -входной регистр, ФБ -функциональный блок,РГ1 и Рг2-буферные регистры, Рг вых-выходной регистр. Буферные регистры используются для хранения результата предыдущего блока, если следующий еще не готов их принять.

В архитектуре вычислительных машин можно найти множество объектов, где конвейеризация обеспечивает ощутимый прирост производительности ВМ. Ярким примером таких объектов являются операционные устройства и память, однако наиболее ощутимый эффект достигается при конвейеризации этапов машинного цикла.

29.Классификация конвейерных устройств

По способу синхронизации работы ступеней конвейеры могут быть синхронными и асинхронными. Для традиционных ВМ характерны синхронные конвейеры. Связано это, прежде всего, с синхронным характером работы процессоров. Ступени конвейеров в процессоре обычно располагаются близко друг от друга, благодаря чему тракты распространения сигналов синхронизации получаются достаточно короткими и фактор «перекоса» сигналов становится не столь существенным. Асинхронные конвейеры оказываются полезными, если связь между ступенями не столь сильна, а длина сигнальных трактов между разными ступенями сильно рознится.

Так же конвейер может быть линейным и нелинейным. В линейном конвейере все этапы выполняются один за одним как по цепочке .Но в ряде ситуаций оказывается выгодным, когда функциональные блоки соединены между собой не последовательно, а в соответствии с логикой обработки, при этом одни блоки в цепочке могут пропускаться, а другие - образовывать циклические структуры.

30.Показатели эффективности конвейеров.

Чтобы охарактеризовать эффект, достигаемый за счет конвейеризации вычислений, обычно используют три показателя: ускорение, эффективность и производи-

тельность.

Под ускорением понимается отношение времени обработки без конвейера и при его наличии. Теоретически наилучшее время обработки входного потока из N значений на конвейере с K ступенями и тактовым периодом ТК можно определить выражением

( )

В процессоре без конвейера общее время выполнения составляет NKTк. Таким образом, ускорение вычислений S за счет конвейеризации вычислений можно описать формулой

|

( |

) |

При |

ускорение стремится к величине, равной количеству ступеней в |

|

конвейере.

Эффективность E определяется как доля ускорения, приходящаяся на одну ступень конвейера:

Производительность P определяется как эффективность, деленная на длительность тактового периода:

|

( |

) |

При |

эффективность стремится к единице, а производительность – к ча- |

|

стоте тактирования конвейера:

31. Конвейерное выполнение команд. Командный конвейер.

Цикл команды представляет собой последовательность этапов. Возложив реализацию каждого из них на самостоятельное устройство и последовательно соединив такие устройства, мы получим классическую схему конвейера команд. Выделим в цикле команды шесть этапов:

1.Выборка команды. Чтение очередной команды из памяти и занесение ее в регистр команды.

2.Декодирование команды. Определение кода операции и способов адресации операндов.

3.Вычисление адресов операндов. Вычисление исполнительных адресов каждого из операндов в соответствии с указанным в команде способом их адресаций.

4.Выборка операндов. Извлечение операндов из памяти. Эта операция не нужна для операндов, находящихся в регистрах.

5.Исполнение команды. Исполнение указанной операции.

6.Запись результата. Занесение результата в память.

Так для каждой команды будут выполнятся данные этапы конвейера, кроме того все этапы могут выполнятся одновременно. Таким образом использование конвейера позволяет существенно сократить время обработки команд.

Конвейерное выполнение команд основано на тех же принципах, что и поточные методы производства. Конвейеризация эффективна только тогда, когда загрузка конвейера близка к полной, а скорость подачи новых команд и операндов соответствует максимальной производительности конвейера.

32.Организация скалярного конвейерного процессора.

Конвейерным называется процессор, в котором используется конвейерное выполнение команд. Скалярным называется такой конвейерный процессор, в котором в каждом машинном цикле запускается на выполнение только одна машинная команда.

Основу скалярного конвейерного процессора составляют конвейер целочисленных операций (целочисленный конвейер) и конвейер операций с плавающей запятой (конвейер ПЗ).

Целочисленный конвейер содержит следующие ступени (всего пять ступеней):

1)ступень предварительной выборки PF (Prefetch). На этой ступени машинные команды выбираются из кэша команд (памяти);

2)ступень декодирования полей команды D1 (Decode 1). На этой ступени декодируются поля команды, определяются операция, подлежащая выполнению, и местоположение операндов;

3)ступень декодирования D2 (Decode 2) – ступень генерации адреса. На этой ступени производится вычисление эффективного адреса операнда, расположенного в памяти;

4)ступень исполнения EX (Execution). На этой ступени производится выборка операндов из РОН и кэша данных (памяти), выполнение операции в АЛУ и запись в кэш данных (память);

5)ступень записи результата WB (Write Back). На этой ступени производится обратная запись результата в РОН, модификация состояния процессора и завершение выполнения команды.

Конвейер ПЗ содержит восемь ступеней. При этом он имеет общие с целочисленным конвейером ступени PF, D1 и D2, но, кроме того, включает еще пять допол-

|

нительных ступеней (переход пока- |

|

Кэш команд |

||

зан штрих пунктирной стрелкой): |

||

|

||

|

||

|

1) ступень EX. На этой ступени про- |

Целочислен- |

PF |

|

|

|

|

|

|

|

|

изводится чтение из кэша данных |

|||||

|

ный |

|

|

|

|

|

|

|

|

|

(памяти) или регистра или запись в |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

РОН |

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

кэш данных (память); |

|

|

|

|

|

|

|

|

|

|

|

|

2) первая исполнительная ступень |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

|

|

Конвейер |

X1. На этой ступени выполняется фа- |

||||

|

|

|

|

|

|

|

|

|

за 1 операции с плавающей запятой |

||||||

|

|

|

|

|

|

|

|

|

|

|

ПЗ |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

или запись в РОН ПЗ. С этой ступени |

|

|

|

|

|

|

EX |

|

|

EX |

|

|

|

РОН |

||

|

|

|

|

|

|

|

|

|

|

|

возможен обход на ступень EX; |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

ПЗ |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

3) вторая исполнительная ступень |

||

|

|

|

|

|

|

WB |

|

|

X1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X2. На этой ступени выполняется фа- |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

за 2 операции с плавающей запятой; |

|

|

|

|

|

|

|

|

|

X2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4) ступень WF. На этой ступени про- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

изводится округление и обратная за- |

|

|

|

|

|

|

|

|

|

WF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

пись результата в РОН ПЗ. С этой |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ступени возможен обход на ступень |

|

|

|

|

|

|

|

|

|

ER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EX; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5) ступень ER. На этой ступени вы- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

водится сообщение о наличии оши- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

бок. |

|

|

|

|

|

|

|

|

Кэш данных |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33.Конфликты в командном конвейере.

Косновным факторам, нарушающим непрерывность конвейерной реализации команд, можно отнести следующие:

1)задержка начала выполнения следующей команды, связанная с ожиданием выборки операнда этой командой или определения его адреса. Такая задержка возникает, когда для выполнения следующей команды требуется результат действий, реализованных предыдущей командой, или когда предыдущей командой определяется адрес операнда следующей команды (модификация адреса);

2)команды условного перехода. При ветвлении программы по результатам проверки условий командой условного перехода команды, следующие за командой перехода и находящиеся в процессе конвейерной обработки (на разных стадиях командного конвейера), остаются невыполненными. В этом случае требуется повторная загрузка конвейера, начиная с команды, расположенной по адресу ветвления (по адресу перехода, заданному в команде условного перехода);

3)отсутствие в кэш-памяти требуемых данных или команд или конфликт-

ное обращение к памяти. В случае отсутствия в кэш-памяти требуемых данных или команд задержка конвейера возникает из-за того, что требуемые данные или команды еще необходимо передать в кэш-память из основной памяти. Конфликтное обращение к памяти может произойти, например, при наложении друг на друга этапов IF, OF, S команд, следующих одна за другой;

4)изменение предшествующей командой содержания последующей команды или содержимого регистра состояния. В этом случае последующая команда должна ожидать завершения предыдущей команды;

5)прерывания. В случае возникновения прерывания и перехода к подпрограмме его обработки команды, находящиеся в это время на командном конвейере, остаются незавершенными, и приходится заново загружать конвейер командами, входящими в подпрограмму обработки прерывания;

6)машинные команды, реализующие сложные операции (например, опера-

ции с плавающей запятой). Для выполнения таких команд требуется много машинных циклов, поэтому последующая за ней команда долго не может достичь стадии выполнения операции в командном конвейере.

Существуют три класса конфликтов:

1)структурные конфликты, которые возникают из-за конфликтов по ресурсам, когда аппаратные средства не могут поддерживать все возможные комбинации команд в режиме одновременного выполнения с совмещением;

2)конфликты по данным, которые могут возникнуть при наличии зависимости по данным между смежными командами;

3)конфликты по управлению, которые возникают при конвейеризации команд переходов и других команд, изменяющих значение программного счетчика.

Конфликты в конвейере приводят к необходимости приостановки выполнения команд. Обычно в простейших конвейерах, если приостанавливается какая-либо команда, то все следующие за ней команды также приостанавливаются. Команды, предшествующие приостановленной, могут продолжать выполняться, но во время приостановки не выбирается ни одна новая команда.