OEVMiS_ekz_shpory

.pdf

18. Устройство управления на основе жесткой (схемной) логики. Микропрограммный автомат с жесткой логикой. Порядок синтеза микропрограммного

автомата с жесткой логикой.

УУ на основе жесткой логики – устройство, в котором сигналы управления реализованы за счет однажды соединенных между собой логических схем.

Счетчик

тактов

Свойства: Высокое быстродействие, определ. только задержек ЛЭ и элементов памяти. Малые удельные затраты аппаратных средств.

Пропорциональный рост объема аппаратных средств в зависимости от сложности реализуемого алгоритма.

Дешифратор тактов |

|

|

|

Порядок синтеза |

||

|

Флаги |

1) |

разработать |

микро- |

||

|

|

|

|

микропрограммного |

||

|

|

|

автомата: 1 Выбор ти- |

|||

|

|

|

пов ЛЭ 2 Кодирование |

|||

|

|

|

сост. автомата 3 Синтез |

|||

|

|

|

комбинационной схемы |

|||

|

|

|

программу работы опе- |

|||

|

|

|

||||

|

|

|

рационного блока – со- |

|||

|

|

|

держательную |

граф- |

||

|

|

|

схему |

алгоритма |

||

|

|

|

(ГСА). |

|

|

|

|

|

|

2) |

составить |

список |

|

микроопераций и логических условий, обозначив микрооперации символами yi, логические условия – xi;

3)завменив микрооперации и логические условия в содержательной ГСА соответствующими символами yi и xi, получить ГСА;

4)выполнить разметку ГСА по следующим правилам: • вход вершины, следующей за начальной, а также вход конечной вершины отметить символом a1; • входы всех вершин, следующих за операторными, отметить символами a2, a3, ...;

5)составить список всех путей переходов в ГСА. Для этого в отмеченной ГСА ищутся все пути переходов из одной отметки в другую, содержащие точно одну операторную вершину. Число условных вершин в таком пути может быть произвольным, в том числе и нулевым;

6)построить таблицу переходов МПА. Таблица включает пять столбцов: • am – исходное состояние, • as – состояние перехода, • X(am, as) – логические условия на переходе МПА из состояния am в состояние as, • Y(am, as) – выходные сигналы (микрооперации) на переходе МПА из состояния am в состояние as, • h – номер строки (перехода).

7)выбрать элементы памяти;

8)перейти к структурной таблице МПА. Эта таблица получается из таблицы переходов МПА путем добавления трех столбцов: • K(am) – коды состояний am, • K(as) – коды состояний as, • F(am, as) – множество функций возбуждения элементов памяти на переходе МПА из состояния am в состояние as;

9)по структурной таблице записать выражения для функций Fr (r = 1, ..., R) и yn (n = 1,

..., N). Эти выражения получаются как дизъюнкции выражений вида AmX(am,as), где Am

– конъюнкция, соответствующая коду состояния am, взятых по всем строкам структурной таблицы МПА, в которых записаны yn или Fr = 1;

10)по полученным выражениям построить комбинационную схему МПА.

19 Устр-во упр-я на основе программируемой логики. Принцип мпу. Организация уст-ва мпу. Кодирование микроопераций в устройстве мпу. Адресация микрокоманд в устройстве микропрограммного управления.

В начале 50-х годов прошлого века Уилкс предложил микропрограммную концепцию организации управления как средство систематизированного структурированного проектирования устройств управления ВМ - для инициирования любой микрооперации достаточно сформировать сигнал управления на соответствующей линии управления, т.е. перевести такую линию в активное состояние.

Отличительной особенностью МПА с программируемой логикой явл-ся хранение микрокоманд в виде кодов в памяти микропрограмм. Каждой машинной команде в этом ЗУ в явной форме соответствует микропрограмма, поэтому такой метод управления называется микропрограммированием, а устройства управления с программируемой ло-

гикой называют микропрограммными. |

|

Микропрограммное управление (МПУ) имеет следующие особенности: 1) |

устрой- |

ства МПУ отличаются большой регулярностью структуры, универсальностью, возможностью оперативного внесения изменений в алгоритм работы проектируемого устройства путем изменения содержимого управляющей памяти; 2) независимость объема оборудования от сложности реализуемых алгоритмов, а также наглядность, облегчающая изучение процесса функционирования системы; 3) возможность проектирования устройств управления со сложными системами переходов между состояниями; 4) проектирование аппаратной части ВМ можно разделить на два вида – разработку микропро-

грамм и логических схем, которые можно проводить параллельно; 5) рационально распределяя функции между аппаратными и микропрограммными средствами можно проектировать семейства ВМ, имеющих одинаковую архитектуру на уровне машинных команд, но отличающихся друг от друга величиной соотношения стоимость-производительность; 6) анализируя программу в машинных кодах и добавляя новые машинные команды, реализующие часто используемые в программах действия, можно модифицировать наборы машинных команд – выполнять настройку системы; 7) недостаток - более медленная обработка по сравнению с устройствами управления с жесткой логикой, так как на скорость работы УУ накладывает ограничение быстродействие управляющей памяти.

Организация устройства микропрограммного управления Устройство микропрограммного управления включает: память микропрограмм, регистр адреса микрокоманды, регистр микрокоманды, дешифратор микрокоманд, преобразователь кода операции, формирователь адреса следующей микрокоманды, формирователь синхроимпульсов. (рис.)

Кодирование микрокоманд Применяемые в микрокомандах варианты кодирования сигналов управления можно свести к трем группам: минимальное кодирование (горизонтальное микропрограммирование), максимальное кодирование (вертикальное микропрограммирование) и групповое кодирование (смешанное микропрограммирование). Структуры микропрограммных автоматов при различных способах кодирования микроопераций показаны на рис.

При горизонт. микропрогр. (а) под каждый сигн. упр-я в микрооперационной части микрокоманды выделен 1 разр. При максимальном (вертик.) кодировании (б) каждой микрооперации присваивается определенный код. Этот код и заносится в МО. В гори- зонт.-вертик. методе (г) в каждую группу включаются взаимно несовместимые сигналы упр-я (микрооперации), т.е. сигналы упр-я, кот. никогда не встреч-ся вместе в одной микрокоманде. При вертик.-горизонт. способе (д) все множество сигналов управления делится на несколько групп, однако в группу включаются сигналы управления (микрооперации), наиболее часто встречающиеся вместе в одном такте. При горизонт., вертик. и горизонт.-вертик. способах кодир-я микроопераций каждое поле микрокоманды несет

фиксированные функции, т.е. имеет место прямое кодирование. При косвенном кодировании одно из полей отводится для интерпретации других полей.

Адресация микрокоманд При выполнении микропрограммы адрес очередной микрокоманды относится к одной из трех категорий: определяется кодом операции команды; является следующим по порядку адресом; является адресом перехода.

Первый случай имеет место только один раз в каждом цикле команды, сразу же вслед за ее выборкой. Каждой команде из системы команд процессора соответствует своя микропрограмма в памяти микропрограмм. Поэтому 1ое действие, кот. нужно произвести после выборки команды, – преобразовать код операции в адрес первой МК соответствующей микропрограммы. Дальнейшая очередность выполнения мик-

рокоманд микропрограммы может быть задана двумя способами: путем указания в каждой МК адреса следующей микрокоманды – принудительная адресация; путем автоматического увеличения на единицу адреса текущей МК – естественная адресация.

Возможные способы реализации принудительной и естественной адресации сводятся к трем типовым вариантам: два адресных поля; одно адресное поле; переменный формат. Два первых метода представляют принудительную адресацию, а третий – есте-

ственную адресацию микрокоманд.

Простейшим вариантом является включение в микрокоманду двух адресных полей (рис лев.).

Главное достоинство принудительной адресации – высокая универсальность и быстродействие. Основной недостаток принуди-

тельной адресации – повышенные требования к емкости памяти для хранения адресов МК.

При естественной адресации отпадает необходимость во введении адресной части в каждую МК. Подразумевается, что микрокоманды следуют в естественном порядке и процесс адресации реализуется счетчиком адреса микрокоманды (СЧAM). Значение СЧAM увеличивается на единицу после чтения очередной МК.

Структура УМУ с естественной адресацией показана на рис.

Достоинство естественной адресации – экономия памяти микропрограмм, а основной недостаток состоит в том, что для любого перехода требуется полный тактовый период, в то время как при принудительной адресации переход выполняется одновременно с формированием управляющих сигналов без дополнительных обращений к управляющей памяти.

20. Операционные устройства. Операционные устройства с жесткой структурой. Операционные устройства с магистральной структурой.

В классической фон-неймановской ВМ функция арифметической и логической обработки данных возлагается на арифметико-логическое устройство (АЛУ). Учитывая разнообразие выполняемых операций и типов обрабатываемых данных, реально можно говорить не о едином устройстве, а о комплексе специализированных операционных устройств (ОПУ), каждое из которых реализует определенное подмножество арифметических или логических операций, предусмотренных системой команд ВМ. В общем случае можно выделить: ОПУ целочисленной арифметики (для чисел с фиксированной запятой); ОПУ для чисел с плавающей запятой; ОПУ для логической обработки данных;ОПУ десятичной арифметики.

Набор элементов, на основе которых строятся структуры различных ОПУ, называется структурным базисом. Структурный базис ОПУ включает в себя: регистры, обеспечивающие кратковременное хранение слов данных; управляемые шины, предназначенные для передачи слов данных; комбинационные схемы, реализующие вычисление логических условий и выполнение микроопераций по сигналам от устройства управления. Различают операционные устройства с жесткой структурой и с магистральной структурой.

Операционные устройства с жесткой структурой В ОПУ с жесткой структурой комбинационные схемы жестко распределены

между всеми регистрами. К каждому регистру относится свой набор комбинационных схем, позволяющих реализовать определенные микрооперации. Например, ОПУ с жесткой структурой, обеспечивающее выполнение операций типа сложение (рис), включает три регистра со своими логическими схемами: регистр первого слагаемого PCл1 и схему ЛРСл1; регистр второго слагаемого РСл2 и схему ЛРСл2; регистр суммы РСм и схему комбинационного сумматора См.

Логическая схема ЛРСл1 обеспечивает передачу результата из регистра РСм в регистр PCл1: прямым кодом; со сдвигом на один разряд влево; со сдвигом на два разряда вправо.

Логическая схема ЛРСл2 реализует микрооперации передачи второго слагаемого из РСл2 на левый вход сумматора: прямым кодом; инверсным кодом; со сдвигом на один разряд влево.

Комбинационный сумматор См предназначен для суммирования (обычного или по модулю 2) операндов, поступивших на его левый (ЛСм) и правый (ПСм) входы. Результат суммирования заносится в регистр РСм.

Достоинством ОПУ с жесткой структурой является высокое быстродействие, недостатком – малая регулярность структуры, что затрудняет реализацию таких ОПУ в виде больших интегральных схем.

Операционные устройства с магистральной структурой В ОПУ с магистральной структурой все внутренние регистры объединены в от-

дельный узел регистров общего назначения (РОН), а все комбинационные схемы – в операционный блок (ОПБ). Операционный блок и узел регистров сообщаются между собой с помощью магистралей – отсюда и название магистральное ОПУ.

В состав узла РОН входят N регистров общего назначения, подключаемых к магистралям A и В через мультиплексоры MUX А и MUX В. Каждый из мультиплексоров является управляемым коммутатором, соединяющим выход одного из РОН с соответству-

ющей магистралью. Номер подключаемого регистра определяется адресом а или b, подаваемым на адресные входы мультиплексора из устройства управления. По магистралям А и В операнды поступают на входы операционного блока, к которым подключается комбинационная схема, реализующая требуемую микрооперацию. Таким образом, любая микрооперация ОПБ может быть выполнена над содержимым любых регистров ОПУ. Результат микрооперации по магистрали С заносится через демультиплексор DMX С в конкретный регистр узла РОН. Демультиплексор представляет собой управляемый коммутатор, имеющий один информационный вход и N информационных выходов. Вход подключается к выходу с заданным адресом с, который поступает на адресные входы DMX С из УУ.

Основным достоинством магистральных ОПУ является высокая универсальность и регулярность структуры, что облегчает их реализацию на кристаллах ИС.

Магистральные ОПУ классифицируют по виду и количеству магистралей, организации узла РОН, типу ОПБ.

Магистрали ОПУ могут быть однонаправленными и двунаправленными, соответственно обеспечивающими передачу данных в одном или двух различных направлениях. По функциональному назначению выделяют: магистрали внешних связей, соединяющих ОПУ с памятью и каналами ввода/вывода ВМ; внутренние магистрали ОПУ, отвечающие за связь между узлом РОН и операционным блоком.

Количество магистралей зависит от архитектуры конкретной ВМ и обычно не превышает двух для внешних связей и трех – для внутренних.

Количество регистров в узле РОН магистрального ОПУ обычно превышает тот минимум, который необходим для реализации универсальной системы операций. Избыток регистров используется: для хранения составных частей адреса (индекса, базы); в качестве буферной, сверхоперативной памяти для повышения производительности ВМ за счет уменьшения требуемых пересылок между основной памятью и ОПУ.

Организация узла РОН может обеспечивать одноканальный или двухканальный доступ как по входу (записи), так и по выходу (считыванию).

Тип операционного блока определяется способом обработки данных. Различают ОПБ последовательного и параллельного типа. В последовательном операционном блоке операции выполняются последовательно разряд за разрядом. При параллельной организации операционного блока все разряды операндов обрабатываются одновременно.

21.Структура взаимосвязей вычислительной машины.

Структуру взаимосвязей ВМ – совокупность трактов связи, объединяющих между собой основные устройства ВМ. Она обеспечивает обмен информацией между: 1) ЦП и памятью, 2) ЦП и модулями В/В, 3) памятью и модулями В/В. Взаимосвязь частей ВМ и ее общение с внешним миром обеспечиваются системой шин. Чтобы охарактеризовать конкретную шину, нужно описать: - совокупность сигнальных линий; - физические, механические и электрические характеристики шины; - используемые сигналы арбитража, состояния, управления и синхронизации; - правила взаимодействия подключенных к шине устройств (протокол шины). Важным критерием, определяющим характеристики шины, является ее целевое назначение. По этому критерию можно выделить: -шины процессор-память; - шины ввода/вывода; - системные шины.

Структура взаимосвязи ВМ:

1)С непосредственными связями между устройствами ВМ – для каждого устройства свой тракт передачи данных:

Память

Процессор

|

|

|

|

|

|

УВВ |

|

УВВ |

|

|

|

|||

|

|

|

|

|

2) С общей шиной:

|

Память |

|

|

|

УВВ |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Процессор

3) С несколькими шинами

Память

Память

Процессор

УВВ УВВ

22.Арбитраж шин. Алгоритмы арбитража. Схемы арбитража.

Арбитраж шин – процедура выбора ведущего устройства, возникает, когда на роль ведущего может претендовать несколько устройств. Арбитраж основан на механизме приоритетов. Приоритет может оставаться неизменным (статич.) либо меняться (динамический). Алгоритмы динамического изменения приоритетов: 1) простая циклическая схема, 2) циклическая смена приоритетов с учетом последнего запроса, 3) смена приоритетов по случайному закону, 4) схема равных приоритетов, 5) алгоритм наиболее давнего использования, 6) на основе очереди FIFO, 7) на основе фиксированных квантов времени.

Схемы арбитража: 1) централизованная, 2) децентрализованная Централизованная – есть центральный арбитр, который предоставляет доступ к шине

одному из запросивших устройств. Различают 2 типа схем: 1) параллельный 2) последовательный

Параллельный

Центральный арбитр

1 - индивидуальная линия от арбитра ко всем возможным ведущем устройствам, каждое устройство формирует сигнал занятости шины.

2 - для выделения запроса наивысшего приоритета используется один сигнал, который проходит через цепочку ведущих устройств. Запросы объединяются на линии запроса шины по схеме «монтажного ИЛИ». Различают 3 типа схем: с цепочкой для сигнала запроса шины (ЗШ)(рис) и с цепочкой для дополнительного сигнала разрешения (РШ), с цепочкой для сигнала предоставления шины (ПШ):

Децентрализованный арбитраж –

единый арбитр отсутствует, каждый веду- щий со-

Запрос шины (ЗШ)

держит блок управления доступом к шине, которые взаимодействуют друг с другом, разделяя между собой права доступа к шине (параллельный арбитраж). Сигналы запросов поступают на контроллеры всех устройств, которые последовательно распложены в цепочке и в зависимости от логики арбитража в устройстве и определяется какое ВУ получит шину.

При кольцевой схеме сигнал возникает в различных точках кольца. Переход к след. ведущему сопровождается циклической сменой приоритетов. В след. цикле арбитража текущ. ведущий будет иметь самый низкий уровень приоритета. Соседний справа получает наивысший приоритет, каждому устр-ву в кольце присваивается уровень приоритета на единицу меньше, чем у соседа слева. Реализуется циклическая смена приоритетов с учетом последнего запроса.

При распределенном арбитраже ведущий сам определяет, стал ли он победителем в арбитраже, опознав на арбитражных линиях свой номер.

23.Протокол шины. Синхронный протокол. Асинхронный протокол.

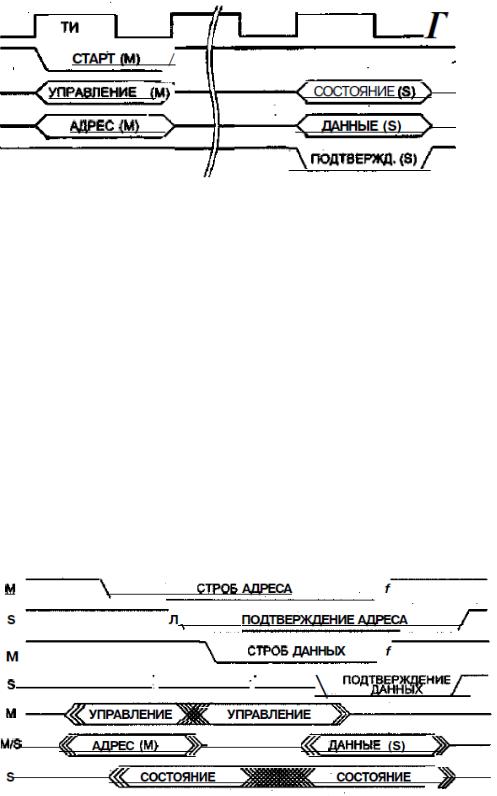

Метод, выбираемый проектировщиками шин для информирования о достоверности адреса, данных, управляющей информации и информации состояния, называется протоколом шины. Используются два основных класса протоколов — синхронный и асинхронный. В синхронном протоколе все сигналы «привязаны» к импульсам единого генератора тактовых импульсов (ГТИ). В асинхронном протоколе для каждой группы линий шины формируется свой сигнал подтверждения достоверности.

В синхронных шинах

имеется центральный ГТИ, к импульсам которого «привязаны» все события на шине. Тактовые импульсы (ТИ) распространяются по специальной сигнальной линии и представляют собой регуляр-

ную последовательность чередующихся единиц и нулей. Один период такой последовательности называется тактовым периодом шины. Именно он определяет минимальный квант времени на шине (временной слот). Все подключенные к шине устройства могут считывать состояние тактовой линии, и все события на шине отсчитываются от начала тактового периода. Изменение управляющих сигналов на шине обычно совпадает с передним или задним фронтом тактового импульса.

Синхронные протоколы требуют меньше сигнальных линий, проще для понимания, реализации и тестирования, мб быстрыми и дешевыми. С другой стороны, они менее гибки, поскольку привязаны к конкретной максимальной тактовой частоте и к конкретному уровню технологии. Из-за проблемы перекоса синхросигналов синхронные шины не могут быть длинными. По синхронному протоколу обычно работают шины «процессор-память»

В асинхронном протоколе начало очередного события на шине определяется не тактовым импульсом, а предшествующим событием и следует непосредственно за этим событием. Каждая совокупность сигналов, помещаемых на шину, сопровождается соответствующим синхронизирующим сигналом, называемым стробом. Синхросигналы, формируемые ведомым, часто называют квитирующими сигналами или подтверждениями сообщения.

В цикле асинхронной шины для подтверждения успешности транзакции используется двунаправленный обмен сигналами управления. Такая процедура носит название квитирования установления связи или

рукопожатия. В рассмотренном варианте процедуры ни один шаг в передаче данных не может начаться, пока не завершен предыдущий шаг. Такое квитирование известно как квитирование с полной взаимоблокировкой.

24. Повышение эффективности шин. Пакетный режим пересылки информации. Механизм транзакций.

Методы: пакетный режим, конвейеризация и расщепление транзакций.

Впакетном режиме один адресный цикл сопровождается множественными циклами данных. Пакет данных передается без указания текущего адреса внутри пакета. При записи в память последовательные элементы блока данных заносятся в последовательные ячейки. Скорость увеличивается за счет уменьшения числа передаваемых адресов.

Васинхронных системах достигается бОльшая скоростью за счет разрешения отправителю начинать следующий цикл данных, не ожидая подтверждения.

Приѐм, при котором очередной элемент данных может быть отправлен устройством А до того, как устройство В завершит считывание предыдущего элемента называется

конвейеризация транзакци.

Данные на шине должны оставаться стабильными в течение времени tст + tуд , после этого возможна смена данных. Макс скорость передачи определяется выражением

.

Для увеличения эффективной полосы пропускания шины используется протокол с расщеплением транзакций. Протокол допускает совмещение во времени сразу нескольких транзакций. Каждая транзакция чтения разделяется на две части: адресную транзакцию и транзакцию данных. От момента поступления запроса до момента формирования отклика шина остается незанятой и может быть использована для выполнения других транзакций, что и использует протокол расщепления транзакций.

Приемы, для расширению полосы пропускания шины: 1) отказ от мультиплексирования шин адреса и данных, 2) увеличение ширины шины данных, 3) повышение тактовой частоты шины, 4) использование блочных транзакций.

25. Физическая организация памяти. Организация микросхем памяти. Режимы работы памяти. Статические оперативные запоминающие устройства. Динамические оперативные запоминающие устройства. Специальные типы оперативной

памяти.

Организация микросхем памяти: Интегральные микросхемы (ИМС) памяти представляют собой массив запоминающих элементов (ЗЭ). Запоминающий элемент способен хранить 1 бит информации. Каждый ЗЭ в микросхеме памяти имеет определенный адрес, на основании которого осуществляется доступ к данному ЗЭ. На физическую организацию массива однобитовых ЗЭ накладывается логическая организация памяти, т. е. разрядность микросхемы n. Разрядность микросхемы определяет количество ЗЭ, имеющих один и тот же адрес. Такая совокупность запоминающих элементов называется ячейкой. В ИМС памяти реализуется координатный принцип адресации ячеек.

Запоминающие элементы, объединенные общей горизонтальной линией, принято называть строкой (row). ЗЭ, подключенные к общей вертикальной линии, называют столбцом (column). Совокупность запоминающих элементов и логических схем, связанных с выбором строк и столбцов, называют ядром микросхемы памяти.

Режимы работы памяти: Последовательный режим представляет собой вариант реализации классического доступа к памяти в синхронных микросхемах. Адрес и управляющие сигналы подаются на микросхему до поступления синхроимпульса. В момент прихода переднего фронта синхроимпульса вся входная информация запоминается во внутренних регистрах, и начинается цикл чтения. Через некоторое время, но в пределах того же цикла данные появляются на внешней шине, причем момент этот определяется только моментом прихода синхронизирующего импульса и скоростью внутренних цепей микросхемы.

Регистровый режим отличается от последовательного режима наличием регистра на выходе микросхемы. Считанные данные заносятся в промежуточный выходной регистр и хранятся там до появления отрицательного фронта (спада) синхроимпульса и в этот момент передаются на шину.

Быстрый постраничный режим. Страница - строка матрицы ЗЭ. Для доступа к очередной ячейке достаточно подавать на ИМС лишь адрес нового столбца, сопровождая его сигналом CAS. При этом обращение к первой ячейке в последовательности производится стандартным образом – поочередным заданием адреса строки и адреса столбца. Рассмотренный режим называется режимом постраничного доступа или просто постраничным режимом. В интегральных микросхемах DRAM используется модификация режима, известная как быстрый постраничный режим: активизация регистра адреса столбца производится не по сигналу CAS, а по сигналу RAS. Сигнал RAS остается активным на протяжении всего страничного цикла и позволяет заносить в регистр адреса столбца новую информацию не по спадающему фронту CAS, а как только адрес на входе ИМС стабилизируется, т.е. практически по переднему фронту сигнала CAS.

Пакетный режим – режим, при котором на запрос по конкретному адресу память возвращает пакет данных, хранящихся не только по этому адресу, но и по нескольким последующим адресам.

В конвейерном режиме процесс разбивается на два этапа. Пока данные из предыдущего цикла чтения передаются на внешнюю шину, происходит запрос на следующую операцию чтения.

Режим удвоенной скорости передачи данных. Сущность метода заключается в пе-

редаче данных по обоим фронтам импульса синхронизации, т. е. дважды за такт. Таким образом, пропускная способность увеличивается также в два раза.

Статические оперативные запоминающие устройства В них запоминающий элемент может хранить записанную информацию неограниченно долго при наличии питающего напряжения. Роль запоминающего элемента в статическом ОЗУ исполняет триггер. Такой триггер представляет собой схему с двумя устойчивыми состояниями, обычно состоящую из шести транзисторов (рис). Статические ОЗУ на настоящий момент – наиболее быстрый, но и наиболее дорогосто-

ящий вид оперативной памяти.

Статические ОЗУ могут быть построены как по асинхронной, так и по синхронной схеме. В настоящее время предпочтение отдается синхрон-

ным ЗУ. В рамках группы синхронных статических ОЗУ выделяют ИМС типа SSRAM и более совершенные РВ SRAM.