- •1. Введение

- •1.1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •1.2 Области применения цифровых микросхем

- •1.3 Виды цифровых микросхем.

- •Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Логические элементы.

- •2.1 Логические элементы

- •Инвертор

- •Логический элемент "и"

- •Логический элемент "или"

- •2.2 Диодно-транзисторная логика (дтл)

- •2.3 Транзисторно-транзисторная логика (ттл)

- •2.4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •2.5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование микросхем с различным напряжением питания

- •Глава 2

- •2.6 Триггер Шмитта

- •3.Арифметические основы цифровой техники.

- •Глава 1 Арифметические основы цифровой техники

- •3.1 Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •4.2 Синтез цифровых комбинационных схем по произвольной таблице истинности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •4.3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •4.5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •4.6 Демультиплексоры

- •5.Генераторы

- •5.1 Генераторы периодических сигналов

- •5.3 Мультивибраторы

- •5.4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •5.5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •6. Последовательностные устройства (цифровые устройства с памятью)

- •6.1 Триггеры

- •6.1.2 Rs триггер

- •6.1.3 D триггеры, работающие по потенциалу (статические d триггеры)

- •6.1.5 D триггеры, работающие по фронту (динамические d триггеры)

- •6.1.6 T триггеры

- •6.1.7 Jk триггер

- •6.2 Регистры

- •6.2.1 Параллельные регистры

- •6.2.2 Последовательные (сдвиговые) регистры

- •6.2.3 Универсальные регистры

- •6.3 Счётчики

- •6.3.1 Двоичные асинхронные счётчики

- •6.3.2 Недвоичные счётчики с обратной связью

- •6.3.3 Недвоичные счётчики с предварительной записью

- •6.3.5 Синхронные двоичные счётчики

- •7.Современные виды цифровых микросхем.

- •7.1 Микросхемы малой степени интеграции (малая логика)

- •7.2 Программируемые логические интегральные схемы (плис).

- •7.3 Программируемые логические матрицы.

- •7.4 Программируемые матрицы логики (pal).

- •7.5 Сложные программируемые логические устройства (cpld).

- •10. Особенности аналого-цифрового и цифро-аналогового преобразования.

- •10.1 Квантование аналогового сигнала по времени

- •10.2 Погрешности дискретизатора

- •10.3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •10.5 Параллельные ацп (flash adc)

- •10.6 Последовательно-параллельные ацп

- •10.7 Ацп последовательного приближения (sar adc)

- •10.9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •10.10 Цифроаналоговые преобразователи r-2r

- •11. Микросхемы цифровой обработки сигналов

- •11.1 Основные блоки цифровой обработки сигналов

- •11.1.1 Двоичные сумматоры

Входные и выходные токи цифровых микросхем

Ещё один важный параметр любой микросхемы — это предельно допустимый выходной ток. Для цифровых микросхем есть два различных значения выходного тока: ток единицы (высокого потенциала) и ток нуля (низкого потенциала). В цифровых микросхемах эти значения различаются. Путь протекания тока единицы цифровых микросхем показан на рисунке 3.4.1

Рисунок 3.4.1

Путь протекания выходного тока единицы

цифровых микросхем

Рисунок 3.4.1

Путь протекания выходного тока единицы

цифровых микросхем

На этом рисунке видно, что в простейшем случае выходной ток цифровой микросхемы (вытекающий ток) совпадает с входным током единицы нагрузочной цифровой микросхемы (микросхемы-приёмника). Часто требуется подавать сигнал с выхода одной микросхемы на несколько других микросхем. В этом случае выходной ток микросхемы будет определяться как сумма входных токов микросхем-приёмников. Количество однотипных микросхем, которые могут быть одновременно подключены к выходу микросхемы, определяют предельную нагрузочную способность микросхемы.

Путь протекания выходного тока нуля (втекающий ток) показан на рисунке 3.4.2. В этом случае выходной ток микросхемы тоже определяется суммой входных микросхем, подключенных к ее выходу.

Iвх

<

Iвых

Для того, чтобы цифровые микросхемы могли нагружаться на несколько микросхем, входной ток должен быть меньше выходного. Для ТТЛ микросхем нагрузочная способность составляет обычно 10. Для КМОП микросхем она может достигать 100, то есть на выход одной КМОП микросхемы можно нагружать до сотни входов других КМОП микросхем.

Параметры, определяющие быстродействие цифровых микросхем

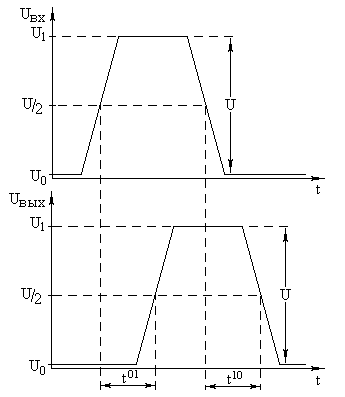

Быстродействие цифровых микросхем определяется скоростями их перехода из одного состояния в другое. При этом оно определяется временем задержки выходного сигнала относительно входного. Не следует путать это время с длительностью фронта выходного импульса цифровой микросхемы. В общем случае длительность переднего (rising — нарастающего) фронта и заднего (falling — спадающего) фронта не совпадают. Длительность фронта определяется как время нарастания (спада) выходного сигнала от напряжения 0,1 U до напряжения 0,9 U, где U — это разность напряжений между уровнем логической единицы и уровнем логического нуля. На рисунке 3.5 длительность переднего (rising — нарастающий) фронта обозначена как tф01, а длительность заднего (falling — спадающий) фронта обозначена как tф10.

Рисунок 3.5

Определение длительности переднего и

заднего фронта выходного импульса

Рисунок 3.5

Определение длительности переднего и

заднего фронта выходного импульса

Время задержки выходного сигнала относительно входного обычно больше длительности фронта выходного сигнала и именно этот параметр приводится в качестве характеристики цифровой микросхемы, определяющей её быстродействие. Это время определяется по точке пересечения входным и выходном сигналами порогового уровня. В цифровых микросхемах время задержки переднего фронта и время задержки заднего фронта обычно не совпадает. Времена задержки t01 и t10 показаны на временной диаграмме, приведенной на рисунке 3.6.

Рисунок 3.6

Определение времени задержки цифровой

микросхемы

Рисунок 3.6

Определение времени задержки цифровой

микросхемы

Описание логической функции цифровых схем

Для того, чтобы упростить анализ любых схем обычно фиксируют какие-либо параметры схемы. Для того, чтобы исключить влияние задержек распространения сигналов на выходные сигналы цифровых микросхем, можно рассматривать эти сигналы в статическом режиме.

Для того, чтобы исключить влияние конкретных схемных решений цифровых устройств, а также влияние конкретных значений выходного напряжения и токов нагрузки, входные и выходные сигналы цифровой схемы можно описывать цифрами '0' и '1'.

Выходные сигналы в простейших цифровых схемах зависят только от входных сигналов, и не зависят от их значений в предыдущие моменты времени. Такие цифровые устройства получили название комбинационных цифровых устройств. Обычно такие устройства описываются при помощи таблиц истинности.

Таблица истинности — это совокупность всех возможных комбинаций логических сигналов на входе цифрового устройства и значений выходных сигналов для каждой комбинации. Для того, чтобы не пропустить ни одной комбинации входных сигналов их обычно записывают в виде двоичного кода. Пример таблицы истинности приведен в таблице 3.1.

Таблица 3.1 Таблица истинности цифровой микросхемы

|

№ комбинации |

вх1 |

вх2 |

вх3 |

Вых1 |

Вых2 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

2 |

0 |

1 |

0 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

0 |

|

6 |

1 |

1 |

0 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

1 |

Для описания принципов работы комбинационной цифровой схемы полностью достаточно таблицы истинности. Этой же таблицы достаточно для создания её принципиальной схемы.