- •1. Введение

- •1.1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •1.2 Области применения цифровых микросхем

- •1.3 Виды цифровых микросхем.

- •Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Логические элементы.

- •2.1 Логические элементы

- •Инвертор

- •Логический элемент "и"

- •Логический элемент "или"

- •2.2 Диодно-транзисторная логика (дтл)

- •2.3 Транзисторно-транзисторная логика (ттл)

- •2.4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •2.5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование микросхем с различным напряжением питания

- •Глава 2

- •2.6 Триггер Шмитта

- •3.Арифметические основы цифровой техники.

- •Глава 1 Арифметические основы цифровой техники

- •3.1 Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •4.2 Синтез цифровых комбинационных схем по произвольной таблице истинности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •4.3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •4.5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •4.6 Демультиплексоры

- •5.Генераторы

- •5.1 Генераторы периодических сигналов

- •5.3 Мультивибраторы

- •5.4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •5.5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •6. Последовательностные устройства (цифровые устройства с памятью)

- •6.1 Триггеры

- •6.1.2 Rs триггер

- •6.1.3 D триггеры, работающие по потенциалу (статические d триггеры)

- •6.1.5 D триггеры, работающие по фронту (динамические d триггеры)

- •6.1.6 T триггеры

- •6.1.7 Jk триггер

- •6.2 Регистры

- •6.2.1 Параллельные регистры

- •6.2.2 Последовательные (сдвиговые) регистры

- •6.2.3 Универсальные регистры

- •6.3 Счётчики

- •6.3.1 Двоичные асинхронные счётчики

- •6.3.2 Недвоичные счётчики с обратной связью

- •6.3.3 Недвоичные счётчики с предварительной записью

- •6.3.5 Синхронные двоичные счётчики

- •7.Современные виды цифровых микросхем.

- •7.1 Микросхемы малой степени интеграции (малая логика)

- •7.2 Программируемые логические интегральные схемы (плис).

- •7.3 Программируемые логические матрицы.

- •7.4 Программируемые матрицы логики (pal).

- •7.5 Сложные программируемые логические устройства (cpld).

- •10. Особенности аналого-цифрового и цифро-аналогового преобразования.

- •10.1 Квантование аналогового сигнала по времени

- •10.2 Погрешности дискретизатора

- •10.3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •10.5 Параллельные ацп (flash adc)

- •10.6 Последовательно-параллельные ацп

- •10.7 Ацп последовательного приближения (sar adc)

- •10.9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •10.10 Цифроаналоговые преобразователи r-2r

- •11. Микросхемы цифровой обработки сигналов

- •11.1 Основные блоки цифровой обработки сигналов

- •11.1.1 Двоичные сумматоры

6.1.3 D триггеры, работающие по потенциалу (статические d триггеры)

В

(S+R)

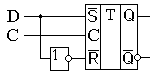

Рисунок 3.1.

Схема D триггера (защелки).

Рисунок 3.1.

Схема D триггера (защелки).

Такой триггер получил название D триггер. Название D триггера происходит от английского слова delay — задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Условно-графическое обозначение D триггера на принципиальных схемах приведено на рисунке 2.

Рисунок 3.2.

Условно-графическое обозначение

D триггера (защелки).

Рисунок 3.2.

Условно-графическое обозначение

D триггера (защелки).

Таблица истинности D триггера достаточно проста, она приведена в таблице 1. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации.

Таблица 3.1. Таблица истинности D триггера.

|

С |

D |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

1 |

1 | |

|

1 |

0 |

x |

0 |

Режим записи информации |

|

1 |

1 |

x |

1 |

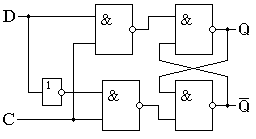

Нужно отметить, что в ТТЛ микросхемах самый распространённый элемент — это "2И-НЕ". Принципиальная схема D триггера на элементах "2И-НЕ" приведена на рисунке 3.3.

Рисунок 3.3

Принципиальная схема D триггера на

элементах "2И-НЕ".

Рисунок 3.3

Принципиальная схема D триггера на

элементах "2И-НЕ".

6.1.5 D триггеры, работающие по фронту (динамические d триггеры)

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеальном случае длительность фронта импульса равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала.

Динамический D триггер, запоминающий входную информацию по фронту, может быть построен из двух D триггеров, работающих по потенциалу (статических D триггеров). Сигнал синхронизации C будем подавать на статические D триггеры в противофазе. Схема триггера, запоминающего входную информацию по фронту (динамического D триггера) приведена на рисунке 5.1.

Рисунок 5.1.

Схема динамического D триггера,

работающего по фронту

Рисунок 5.1.

Схема динамического D триггера,

работающего по фронту

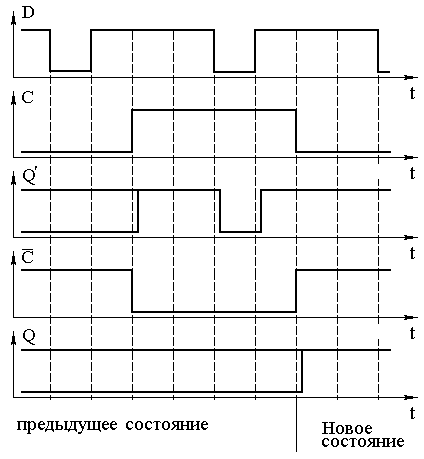

Рассмотрим работу схемы триггера, приведенной на рисунке 5.1 подробнее. Для этого воспользуемся временными диаграммами, показанными на рисунке 5.2. На этих временных диаграммах обозначение Q' соответствует сигналу на выходе первого статического D триггера. Так как на вход синхронизации второго статического D триггера тактовый сигнал поступает через инвертор, то когда первый D триггер находится в режиме хранения, второй D триггер пропускает сигнал на выход схемы. И наоборот, когда первый D триггер пропускает сигнал с входа схемы на свой выход, второй D триггер находится в режиме хранения.

Рисунок 5.2.

Временные диаграммы D триггера

Рисунок 5.2.

Временные диаграммы D триггера

То, что триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником, изображённым на выводе входа синхронизации. То, что внутри этого триггера находится два триггера, отображается в среднем поле условно-графического изображения двойной буквой T.