- •1. Введение

- •1.1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •1.2 Области применения цифровых микросхем

- •1.3 Виды цифровых микросхем.

- •Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Логические элементы.

- •2.1 Логические элементы

- •Инвертор

- •Логический элемент "и"

- •Логический элемент "или"

- •2.2 Диодно-транзисторная логика (дтл)

- •2.3 Транзисторно-транзисторная логика (ттл)

- •2.4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •2.5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование микросхем с различным напряжением питания

- •Глава 2

- •2.6 Триггер Шмитта

- •3.Арифметические основы цифровой техники.

- •Глава 1 Арифметические основы цифровой техники

- •3.1 Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •4.2 Синтез цифровых комбинационных схем по произвольной таблице истинности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •4.3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •4.5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •4.6 Демультиплексоры

- •5.Генераторы

- •5.1 Генераторы периодических сигналов

- •5.3 Мультивибраторы

- •5.4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •5.5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •6. Последовательностные устройства (цифровые устройства с памятью)

- •6.1 Триггеры

- •6.1.2 Rs триггер

- •6.1.3 D триггеры, работающие по потенциалу (статические d триггеры)

- •6.1.5 D триггеры, работающие по фронту (динамические d триггеры)

- •6.1.6 T триггеры

- •6.1.7 Jk триггер

- •6.2 Регистры

- •6.2.1 Параллельные регистры

- •6.2.2 Последовательные (сдвиговые) регистры

- •6.2.3 Универсальные регистры

- •6.3 Счётчики

- •6.3.1 Двоичные асинхронные счётчики

- •6.3.2 Недвоичные счётчики с обратной связью

- •6.3.3 Недвоичные счётчики с предварительной записью

- •6.3.5 Синхронные двоичные счётчики

- •7.Современные виды цифровых микросхем.

- •7.1 Микросхемы малой степени интеграции (малая логика)

- •7.2 Программируемые логические интегральные схемы (плис).

- •7.3 Программируемые логические матрицы.

- •7.4 Программируемые матрицы логики (pal).

- •7.5 Сложные программируемые логические устройства (cpld).

- •10. Особенности аналого-цифрового и цифро-аналогового преобразования.

- •10.1 Квантование аналогового сигнала по времени

- •10.2 Погрешности дискретизатора

- •10.3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •10.5 Параллельные ацп (flash adc)

- •10.6 Последовательно-параллельные ацп

- •10.7 Ацп последовательного приближения (sar adc)

- •10.9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •10.10 Цифроаналоговые преобразователи r-2r

- •11. Микросхемы цифровой обработки сигналов

- •11.1 Основные блоки цифровой обработки сигналов

- •11.1.1 Двоичные сумматоры

Десятичный дешифратор (декодер)

Рассмотрим пример построения дешифратора (декодера) из двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. Это классический пример, иллюстрирующий, что нулями и единицами описываются не только двоичные коды. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Около каждого разряда десятичного кода подписана десятичная цифра, которую отображает логическая единица в этом разряде. Сигнал с этих выводов дешифратора можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру. На входе дешифратора двоичный код записывается в соответствии с правилами двоичной системы счисления. Таблица истинности десятичного декодера приведена в таблице 3.1.

Таблица 3.1. Таблица истинности десятичного декодера.

|

Входы Двоичная форма |

Выходы Десятичная форма | ||||||||||||

|

8 |

4 |

2 |

1 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

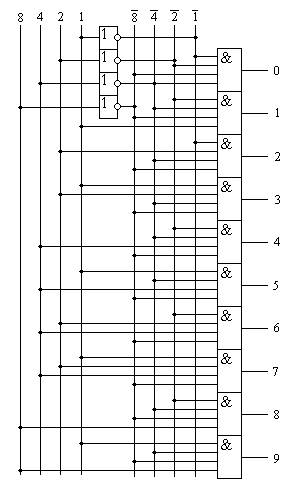

В соответствии с принципами построения схемы по произвольной таблице истинности получим схему декодера, реализующего таблицу истинности, приведённую в таблице 3.1. Эта схема приведена на рисунке 3.1.

Рисунок 3.1.

Принципиальная схема двоично-десятичного

дешифратора (декодера).

Рисунок 3.1.

Принципиальная схема двоично-десятичного

дешифратора (декодера).

Как видно на этой схеме для реализации каждой строки таблицы истинности потребовалась схема "4И". Схема "ИЛИ" не потребовалась, так как в таблице истинности на каждом выходе присутствует только одна единица.

Дешифраторы выпускаются в виде отдельных микросхем или используются в составе других микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ.

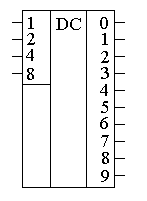

Условно-графическое обозначение микросхемы дешифратора на принципиальных схемах приведено на рисунке 3.2. На этом рисунке приведено обозначение двоично-десятичного дешифратора, полная внутренняя принципиальная схема которого изображена на рисунке 3.1.

Рисунок 3.2. Условно-графическое

обозначение двоично-десятичного

дешифратора.

Рисунок 3.2. Условно-графическое

обозначение двоично-десятичного

дешифратора.

Точно таким же образом можно получить принципиальную схему и для любого другого декодера (дешифратора). Наиболее распространены схемы восьмеричных и шестнадцатеричных дешифраторов. Для индикации такие дешифраторы в настоящее время практически не используются. В основном такие дешифраторы используются как составная часть более сложных цифровых модулей.