4 курс / Интерфейсы / 1

.docxЛабораторная работа №1

ИССЛЕДОВАНИЕ РАБОТЫ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ

С ПОМОЩЬЮ ЛОГИЧЕСКОГО АНАЛИЗАТОРА 825

Выполнила:

студентка группы 08-АС

Смирнова А.А.

Цель работы: исследование выполнения отдельных команд микропроцессора (МП) КР580ВМ80А, приобретение навыков диагностирования микропроцессорных систем (МПС) с помощью логического анализатора (ЛА).

Шина ISA

ISA Bus (Industry Standard Architecture) — шина расширения, применявшаяся с первых моделей PC и ставшая промышленным стандартом. В классическом варианте шина имела разрядность данных 8 бит и адреса — 20 бит. Позднее разрядность данных и адреса были расширены до 16 бит и 24 бит соответственно. В таком виде она существует и поныне. Конструктивно шина выполнена в виде двух щелевых разъемов с шагом выводов 2,54 мм. Подмножество ISA-8 использует только 62-контактный слот (ряды А, В), в ISA-16 применяется дополнительный 36-контактный слот (ряды С, D).

Шина обеспечивает возможность отображения 8-ми или 16-битных регистров на пространство ввода/вывода и памяти. Диапазон адресов памяти ограничен областью UMA (выше A0000h).

Диапазон адресов ввода/вывода сверху ограничен количеством используемых для дешифрации бит адреса, нижняя граница ограничена областью адресов 0—FFh, зарезервированных под устройства системной платы.

В PC была принята 10-битная адресация ввода/вывода, при которой линии адреса А[15:10] устройствами игнорировались. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100h—3FFh, то есть всего 758 адресов 8-битных регистров. На некоторые из адресов претендуют системные устройства. Впоследствии стали применять 12-битную адресацию (диапазон l00h-FFFh). При ее использовании необходимо учитывать возможность присутствия на шине старых 10-битных адаптеров, которые «отзовутся» на адрес с подходящими ему битами А[9:0] во всей допустимой области 12-битного адреса четыре раза (у каждого 10-битного адреса будет еще по три 12-битных псевдонима).

Протокол передачи данных

Для передачи данных от исполнителя к задатчику предназначены циклы чтения ячейки памяти или порта ввода-вывода, для передачи данных от задатчика к исполнителю — циклы записи ячейки памяти или порта ввода-вывода.

В каждом цикле текущий (на время данного цикла) задатчик формирует адрес обращения и управляющие сигналы, а в циклах записи еще и данные на шине. Адресуемое устройство-исполнитель в соответствии с полученными управляющими сигналами принимает (в цикле записи) или формирует (в цикле чтения) данные.

Также оно может, при необходимости, управлять длительностью цикла и разрядностью передачи.

Здесь условный сигнал CMD изображает один из следующих сигналов:

SMEMR, MEMR — в цикле чтения памяти;

SMEMW, MEMW — в цикле записи памяти;

IOR — в цикле чтения порта ввода-вывода;

IOW — в цикле записи порта ввода-вывода.

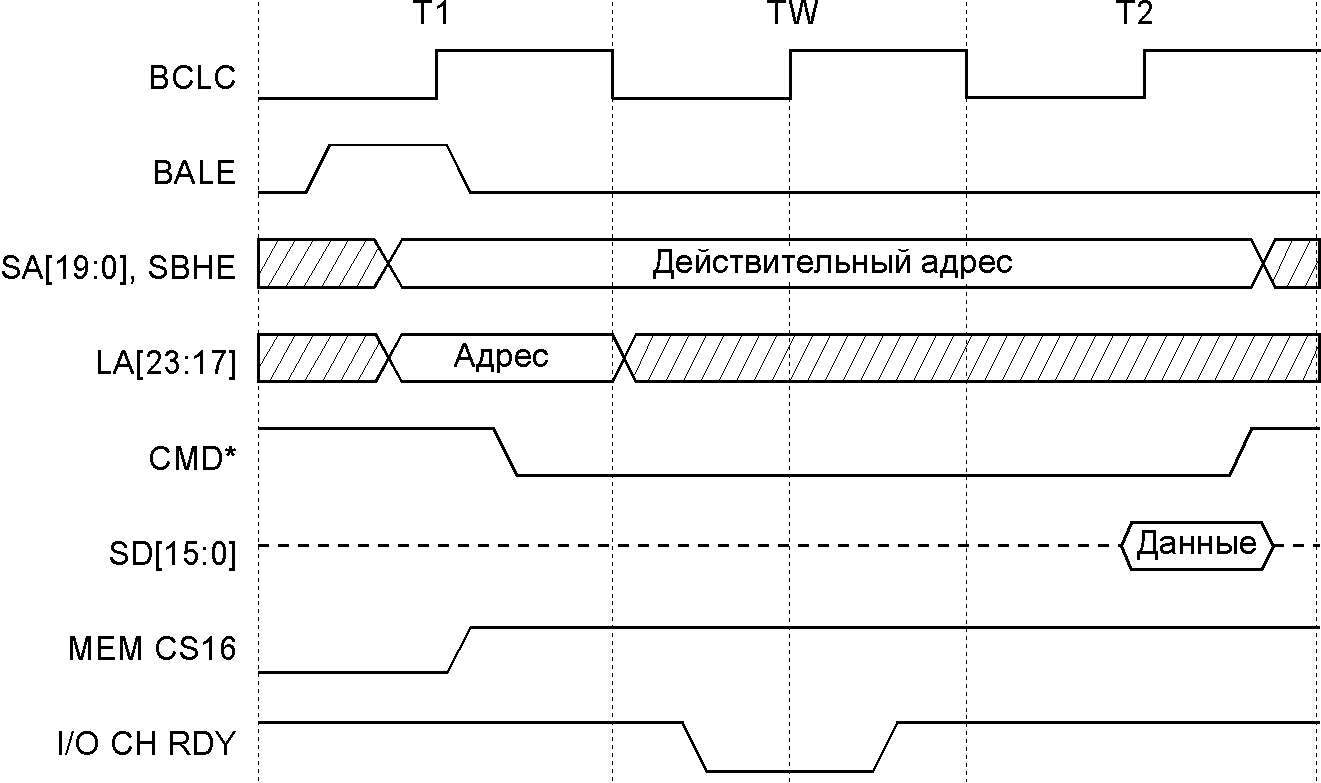

В начале каждого цикла контроллер шины устанавливает адрес обращения: на линиях SA[19:0] и SBHE действительный адрес сохраняется на время всего текущего цикла; на линиях LА[23:17] адрес действителен только в начале цикла, так что требуется его «защелкивание». Каждое устройство имеет дешифратор адреса — комбинационную схему, срабатывающую только тогда, когда на шине присутствует адрес, относящийся к данному устройству.

В фазе адресации устройства еще «не знают», к какому из пространств (памяти или ввода-вывода) относится выставленный адрес. Но дешифраторы адресов уже срабатывают, и, когда в следующей фазе шина управления сообщает тип операции, адресуемое устройство уже оказывается готовым к ее исполнению. Если устройство использует линии LA[23:17] (они нужны лишь для обращений к памяти выше границы FFFFFh), то они на дешифратор адреса должны проходить через регистр-защелку, «прозрачный» во время действия сигнала BALE и фиксирующий состояние выходов по его спаду. Это позволяет дешифратору, всегда вносящему некоторую задержку, начинать работу раньше, чем поступит управляющий сигнал чтения или записи.

При обращении к портам ввода-вывода сигналы LА[32:17] не используются. Если устройство имеет более одного регистра (ячейки), то для выбора конкретного регистра (ячейки) ему требуется несколько линий адреса. Как правило, старшие биты шины адреса поступают на вход дешифраторов адреса, формирующих сигналы выборки устройств, а младшие биты — на адресные входы самих устройств. Тогда каждое устройство в пространстве будет занимать наиболее компактную область смежных адресов размером в 2n байт, где n — номер младшей линии адреса, поступающей на дешифратор. Из них реально необходимы 2m адресов, где m — номер самой старшей линии адреса, участвующей в выборе регистра устройства. В идеале должно быть n=m+l: при большем значении n отведенное (по дешифратору) пространство адресов не будет использовано полностью и регистры устройства будут повторяться в отведенной области 2n-m-1 раз, то есть у них появятся адреса-псевдонимы (alias). Адреса-псевдонимы будут отличаться от истинного адреса (минимального из всех псевдонимов) на K×2m+1, где К — целое число. Меньшее значение n недопустимо, поскольку тогда не все регистры устройства будут доступны задатчику.

Разрядность данных в каждом цикле обращения определяется потребностями текущего задатчика и возможностями исполнителя.

Момент помещения действительных данных на линии SD[15:0] определяется управляющими сигналами чтения/записи, так что исполнителю не требуется синхронизация с тактовым сигналом шины. В циклах чтения адресованный исполнитель должен выдать данные на шину по началу (спаду) соответствующего сигнала чтения (IOR, MEMR, SMEMR) и удерживать их до конца действия сигнала (пока не произойдет подъем сигнала).

В циклах записи задатчик выставляет действительные данные несколько позже начала (спада) сигнала записи (IOW, MEMW, SMEMW). Устройство-исполнитель должно фиксировать для себя эти данные в конце цикла по подъему сигнала записи. От устройства-исполнителя не предусматривается никаких подтверждений исполнения циклов; длительность цикла устанавливает задатчик, но исполнитель может потребовать удлинения или укорочения циклов.

С помощью сигнала IOCHRDY исполнитель может удлинить цикл на произвольное число тактов, при этом задатчик будет вводить дополнительные такты ожидания (wait states). Обычно контроллер шины следит за длительностью цикла и по достижении критического времени принудительно его завершает (по тайм-ауту, возможно, и не сообщая об этом событии). Слишком длинные циклы тормозят работу компьютера, а превышение длительности 15 мкс может привести к сбою регенерации и потере данных в ОЗУ.

С помощью сигнала 0WS исполнитель предлагает задатчику укоротить цикл, исключив такты ожидания. Реакция задатчика на одновременное использование сигналов IOCHRDY и 0WS непредсказуема, этой ситуации следует избегать.